vivado中关闭代码解释器的特殊注释(pragma translate_off、pragma translate_on)

记录一个奇怪的现象:

Xilinx的一些IP核例程总会使用这种写法来添加是否添加ila的参数, 以Aurora 64B66B IP核的例程为例:

module aurora_64b66b_0_exdes #

(

parameter USE_CORE_TRAFFIC = 1,

parameter USR_CLK_PCOUNT = 9'd255,

parameter EXAMPLE_SIMULATION = 0

//pragma translate_off

| 1

//pragma translate_on

,

parameter USE_LABTOOLS = 1

//pragma translate_off

& 0

//pragma translate_on

)

(

RESET,

// Error Detection Interface

HARD_ERR,

SOFT_ERR,

DATA_ERR_COUNT,

// Status

LANE_UP,

CHANNEL_UP,

// System Interface

INIT_CLK_P,

INIT_CLK_N,

PMA_INIT,

//70MHz DRP clk for Virtex-6 GTH

DRP_CLK_IN,

// GTX Reference Clock Interface

GTHQ3_P,

GTHQ3_N,

GTHQ5_P,

GTHQ5_N,

// GTX Serial I/O

RXP,

RXN,

TXP,

TXN

);

module aurora_64b66b_0_exdes #

(

parameter USE_CORE_TRAFFIC = 1,

parameter USR_CLK_PCOUNT = 9'd255,

parameter EXAMPLE_SIMULATION = 0

//pragma translate_off

| 1

//pragma translate_on

,

parameter USE_LABTOOLS = 1

//pragma translate_off

& 0

//pragma translate_on

)

(

RESET,

// Error Detection Interface

HARD_ERR,

SOFT_ERR,

DATA_ERR_COUNT,

// Status

LANE_UP,

CHANNEL_UP,

// System Interface

INIT_CLK_P,

INIT_CLK_N,

PMA_INIT,

//70MHz DRP clk for Virtex-6 GTH

DRP_CLK_IN,

// GTX Reference Clock Interface

GTHQ3_P,

GTHQ3_N,

GTHQ5_P,

GTHQ5_N,

// GTX Serial I/O

RXP,

RXN,

TXP,

TXN

);

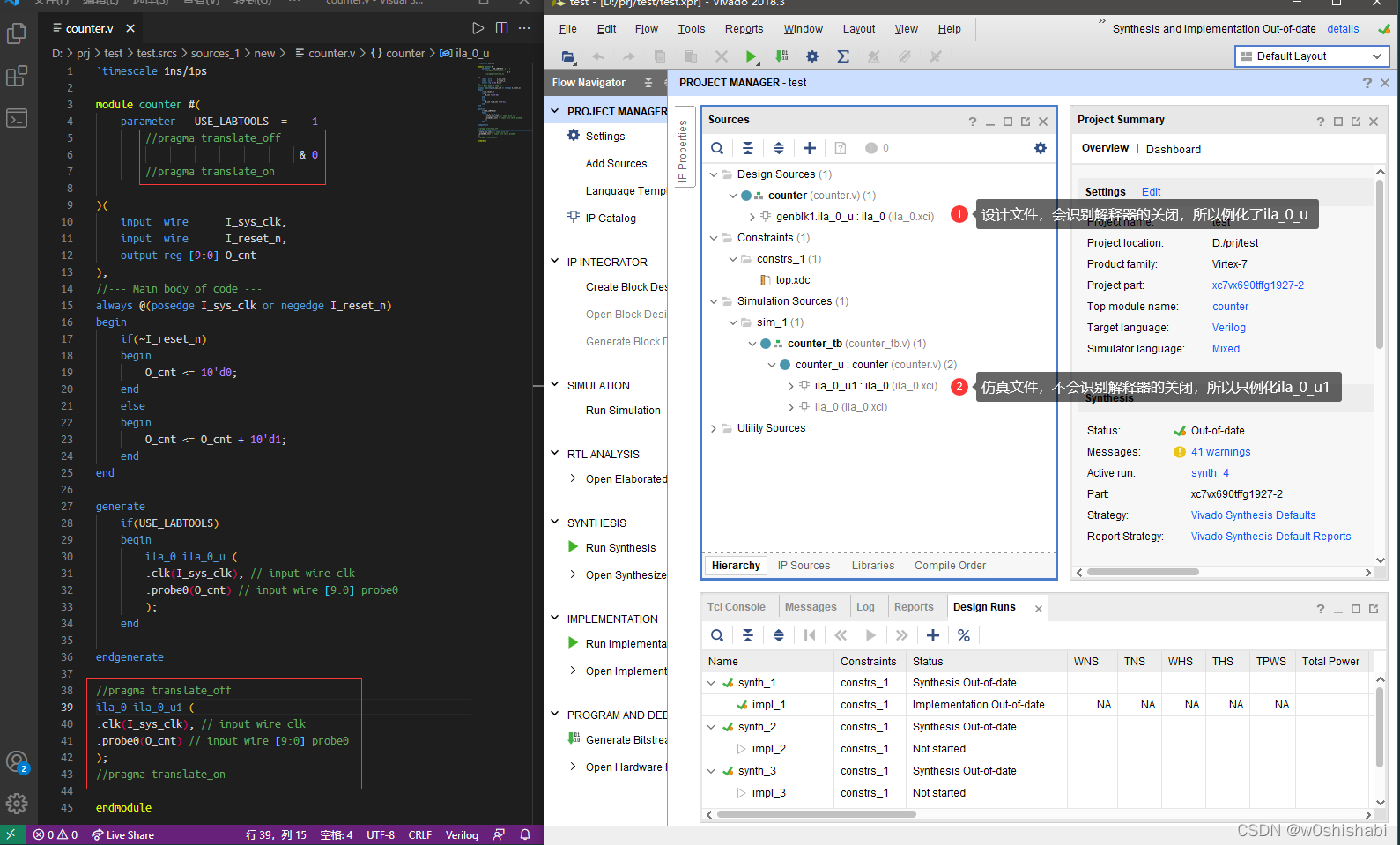

其中,参数 EXAMPLE_SIMULATION 表示是否为仿真模式,USE_LABTOOLS 表示是否添加vio ila以进行测试。

经过实验测试,这种写法可以实现的功能:

![]()

在vivado中,识别到的是 EXAMPLE_SIMULATION = 0 和 USE_LABTOOLS = 1,这样工程就处于非仿真模式,以及synthesis时就会添加测试模块vio和ila。

在modelsim等仿真工具中,结果是 EXAMPLE_SIMULATION = 0 | 1 = 1 和 USE_LABTOOLS = 1 & 0 = 0, 仿真时工程就处于仿真模式,而且会省略掉一些ila和vio模块。

按注释的字面意思猜测为pragma translate_off关闭vivado的程序解释器。

Xilinx的一些IP核例程总会使用这种写法来添加是否添加ila的参数, 以Aurora 64B66B IP核的例程为例:

module aurora_64b66b_0_exdes #

(

parameter USE_CORE_TRAFFIC = 1,

parameter USR_CLK_PCOUNT = 9'd255,

parameter EXAMPLE_SIMULATION = 0

//pragma translate_off

| 1

//pragma translate_on

,

parameter USE_LABTOOLS = 1

//pragma translate_off

& 0

//pragma translate_on

)

(

RESET,

// Error Detection Interface

HARD_ERR,

SOFT_ERR,

DATA_ERR_COUNT,

// Status

LANE_UP,

CHANNEL_UP,

// System Interface

INIT_CLK_P,

INIT_CLK_N,

PMA_INIT,

//70MHz DRP clk for Virtex-6 GTH

DRP_CLK_IN,

// GTX Reference Clock Interface

GTHQ3_P,

GTHQ3_N,

GTHQ5_P,

GTHQ5_N,

// GTX Serial I/O

RXP,

RXN,

TXP,

TXN

);

module aurora_64b66b_0_exdes #

(

parameter USE_CORE_TRAFFIC = 1,

parameter USR_CLK_PCOUNT = 9'd255,

parameter EXAMPLE_SIMULATION = 0

//pragma translate_off

| 1

//pragma translate_on

,

parameter USE_LABTOOLS = 1

//pragma translate_off

& 0

//pragma translate_on

)

(

RESET,

// Error Detection Interface

HARD_ERR,

SOFT_ERR,

DATA_ERR_COUNT,

// Status

LANE_UP,

CHANNEL_UP,

// System Interface

INIT_CLK_P,

INIT_CLK_N,

PMA_INIT,

//70MHz DRP clk for Virtex-6 GTH

DRP_CLK_IN,

// GTX Reference Clock Interface

GTHQ3_P,

GTHQ3_N,

GTHQ5_P,

GTHQ5_N,

// GTX Serial I/O

RXP,

RXN,

TXP,

TXN

);

其中,参数 EXAMPLE_SIMULATION 表示是否为仿真模式,USE_LABTOOLS 表示是否添加vio ila以进行测试。

经过实验测试,这种写法可以实现的功能:

在vivado中,识别到的是 EXAMPLE_SIMULATION = 0 和 USE_LABTOOLS = 1,这样工程就处于非仿真模式,以及synthesis时就会添加测试模块vio和ila。

在modelsim等仿真工具中,结果是 EXAMPLE_SIMULATION = 0 | 1 = 1 和 USE_LABTOOLS = 1 & 0 = 0, 仿真时工程就处于仿真模式,而且会省略掉一些ila和vio模块。

按注释的字面意思猜测为pragma translate_off关闭vivado的程序解释器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号