xilinx时钟资源

一、MMCM与PLL的区别

在Xilinx的FPGA中,时钟管理器称为Clock Management,简称CMT。我们所用到的DCM / PLL / MMCM都包含在CMT中。

DCM是比较早的FPGA中使用的,某些Sparten-3和Virtex-4,后面的器件不再使用了。在Virtex-4中,CMT包括一个PLL和两个DCM。DCM的核心是DLL,即延迟Locked Loop,它是一个数字模块,可以产生不同相位的时钟,分频,倍频,相位动态调整等,但精度有限。

PLL就是锁相环,这个大家应该都熟悉,时钟倍频,分频,调节相位等都是可以用PLL,而且PLL是一个模拟电路,它产生的频率比DCM更加准备,jitter也更好,但PLL无法动态调整相位。

MMCM是混合模式时钟管理器,它的官方解释是:这是一个PLL,上面加上了DCM的一小部分以进行精细的相移(这就是它的混合模式的原因-PLL是模拟的,但是相移是数字的) 。它是在PLL的基础上加上了相位动态调整功能,因为PLL是模块电路,而动态调相是数字电路,所以叫混合模式。MMCM是在Virtex-6中被约会的,而且Virtex-6中也只有MMCM。

7s FPGA中,最高包含了24个CMT,每个CMT包含一个MMCM和一个PLL。Ultrascale中,一个CMT包含一个MMCM和两个PLL。

MMCM是在PLL的基础上加上了相位动态调整功能

MMCM相对PLL的优势就是相位可动态调整,但PLL占用的面积更小。

二、时钟资源

在Xilinx的FPGA中,时钟网络资源分为两大类:全局时钟资源和区域时钟资源。

全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

区域时钟资源是独立于全局时钟网络的。Xilinx的器件分成若干个时钟区域,以Virtex-6为例,Virtex-6的最小器件有6个区域,最大器件有18个区域。它与全局时钟不同,区域时钟信号X只能驱动限定的时钟区域。

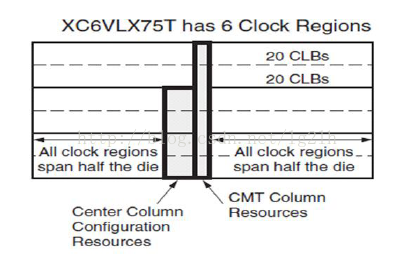

这里面提到区域时钟的概念,需要解释一下。Xilinx的FPGA器件是通过时钟区域来管理时钟网络的,以Virtex-6为例,时钟区域的大小固定为40个CLB 高,半个晶片宽。因此大尺寸的器件有更多的时钟区域。如下图所示,下图中的FPGA器件一共包含6个时钟区域,左侧三个右侧三个,从图可以看出每个区域高度是2*20CLBs,区域宽度是半个FPGA芯片的宽度。中间是CMT时钟管理模块。

每个时钟区域的中间方向有一个时钟行(HROW),以Virtex-6为例,一个时钟行,共包含12个水平时钟线,12个水平时钟线可以全部由全局时钟BUFG驱动。也可以由区域内部的时钟组件缓冲器驱动,例如BUFH和BUFR。这个时候有人会问什么是BUFG、BUFR和BUFH。

先来解释一下BUFG,这个比较简单,就是全局时钟网络时钟驱动器,如果时钟信号要走全局时钟网络,必须通过这个BUFG来驱动,BUFG可以驱动所有的CLB,RAM,IOB。spartan6 有一共有16个BUFG全局时钟线。virtex-6则一共有32个BUFG全局时钟线。参考文献链接见下面。

再看BUFH,BUFH驱动区域中的水平全局时钟树,Xilinx的时钟是通过时钟树来分布的,以spartan6时钟树为例,看下图。FPGA中间竖排是CMT时钟管理模块,就是PLL和DCM。全局时钟缓冲器BUFG是位于FPGA器件的中心位置,时钟的输入可以来自FPGA的上、下、左、右的bank,也可以来自PLL或DCM;16个BUFGMUX通过驱动vertical spine并经vertical spine 往南北方向传播,vertical spine就相当于时钟树的树干 ,根据这条线路,时钟水平延伸至HCLK时钟列并经HCLK时钟列提供了访问局部逻辑原语的路径,HCLK及所谓的水平时钟线,相当于树枝;每一个HCLK列左右两边各有16个水平时钟缓冲BUFH驱动左右逻辑资源。

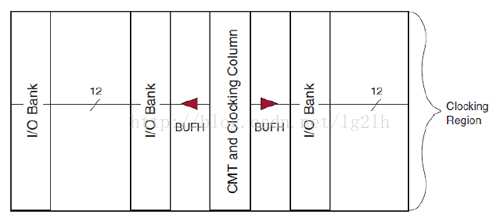

以Virtex-6每一个HCLK列左右两边各有12个水平时钟缓冲BUFH驱动左右逻辑资源,即每个时钟区域有12个BUFH时钟线。如下图

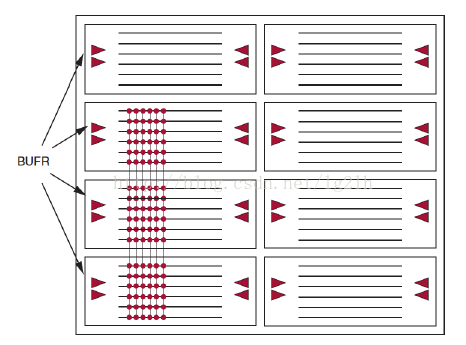

最后解释BUFR,BUFR我在SPARTAN6的时钟资源手册UG382里没有看到,应该是没有啊。BUFR是区域时钟缓冲器,要进入区域时钟网络,必须例化BUFR。一个BUFR最多可以驱动三个相邻的时钟区域中的区域时钟。顶部和底部区域中BUFR只能连接相邻的一个时钟区域,也就是说,顶部的BUFR连接它所在的下面一个相邻区域。底部的BUFR只能连接它所在的上边一个相邻区域。因此,底部和顶部BUFR的作用区域为两个时钟区域。如下图,下图是共有8个时钟区域的FPGA,每个时钟区域最多包含6个BUFR时钟线。截止现在可以看到(紫色标注)Vertex器件的每个时钟区域,共有6个BUFR和12个BUFH。SPARTAN6每个时钟区域好像就有16个BUFH。最后声明一下BUFR不仅可以驱动IO,也可以驱动CLB,RAM。下面接收的BUFIO只能驱动IOB模块。BUFR还可以1-2-4-8分频。

最后说一下BUFIO,BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BUFIO,其中的2个可以驱动相邻区域的I/O时钟网络。BUFIO不能驱动逻辑资源(CLB、BRAM等),因为I/O时钟网络只存在于I/O列中。

浙公网安备 33010602011771号

浙公网安备 33010602011771号