低成本FPGA的MIPI测试GOWIN和LATTICE CROSSLINK

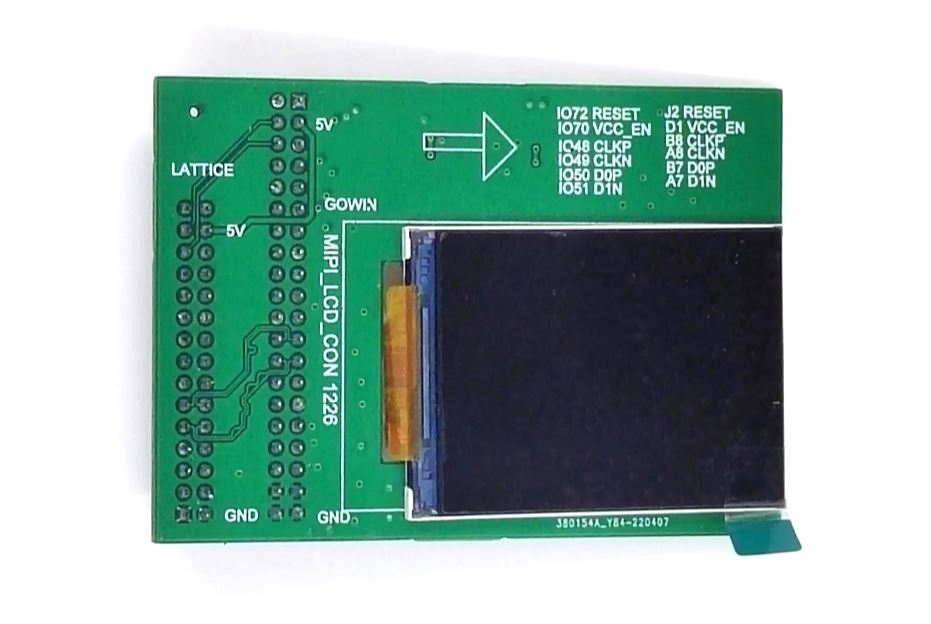

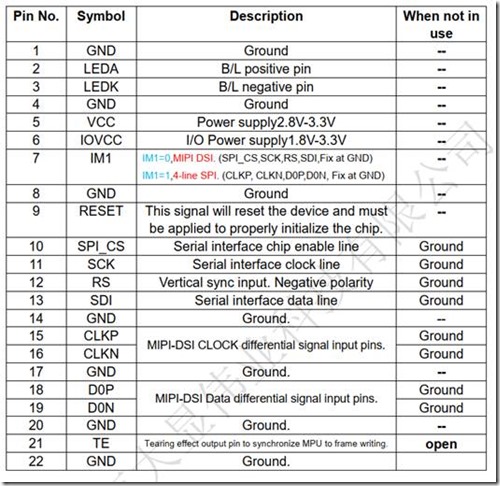

本次实验MIPI屏,2.0寸,分辨率是240*320 RGB888, 接口如下:

接上IO就是RST和MIPI的时钟和数据接口,另外就是电源和地。

一:GOWIN的测试方案

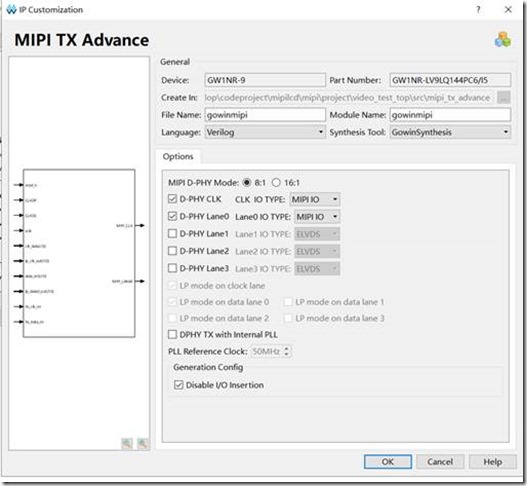

Gowin的案例中,首先是软件要升级到Gowin_V1.9.8以上版本。使用的是IP是mpi-tx_adanve,这个IP才支持LP模式。另外一个mipi-tx是不支持的lp模式。所以用这个来设计。

这个IP 有个缺点是,SCLK是外部给他,千万要注意这个,这个SCLK是CLK-BIT除以4给的时钟。

在modelsim下,找到codeproject/mipilcd/mipi/testmodel 文件夹下,找到sim_modelsim_gowin.do,如果gowin安装目录不一样,需要修改gowin_dir 变量。

set gowin_dir "D:/programmer/gowin/Gowin_V1.9.7.02Beta/IDE/simlib/gw1n"

vlog \

+define+sim \

+define+gowin \

$gowin_dir/prim_sim.v \

../project/video_test_top/src/*.v \

../project/video_test_top/src/mipi_tx_advance/gowinmipi.vo \

../project/video_test_top/src/gowin_rpll/gowin_rpll.v \

../project/video_test_top/src/gowin_rpll/gowin_vclkref.v \

../project/video_test_top/src/gowin_sdpb/gowin8b.v \

../project/video_test_top/src/gowin_sdpb/gowin24b.v \

test_video_test_top.v

# Start the simulator #

vsim work.test_video_test_top –novopt

运行 do sim_modelsim_gowin.do

gowinmipi gowinmipi_inst(

.reset_n(byteclk_rstn), //input reset_n

.MIPI_CLK_P(clk_p), //output MIPI_CLK_P

.MIPI_CLK_N(clk_n), //output MIPI_CLK_N

.clk_data(8'b0101_0101),

.clk_bit(clk_bit_i), //input clk_bit

.clk_bit_90(clk_bit_90_i), //input clk_bit_90

.lp_clk_out({mipi_lpclk_p,mipi_lpclk_n}), //input [1:0] lp_clk_out

.MIPI_LANE0_P(data_p), //output MIPI_LANE0_P

.MIPI_LANE0_N(data_n), //output MIPI_LANE0_N

.data_in0(phy_hs_data), //input [7:0] data_in0

.lp_data0_out({mipi_lp_p,mipi_lp_n}), //input [1:0] lp_data0_out

.hs_clk_en(phy_clk_hsen), //input hs_clk_en

.hs_data_en(phy_hs_en), //input hs_data_en

.sclk(byte_clk) //output sclk

);

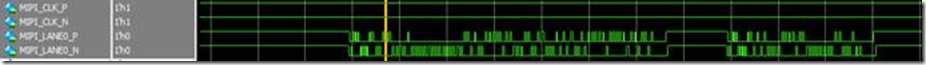

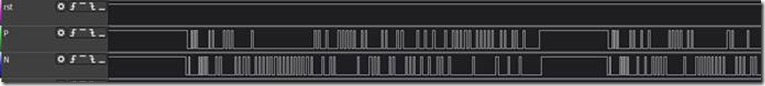

LP模式的情况下是这样

HS模式下是这样的。

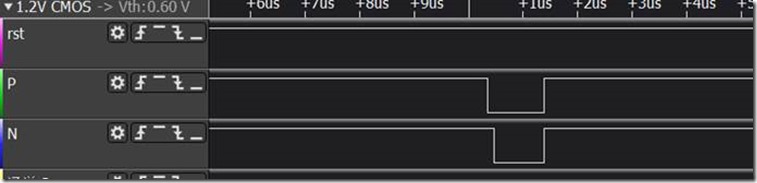

从逻辑分析仪得到波形,一致性。

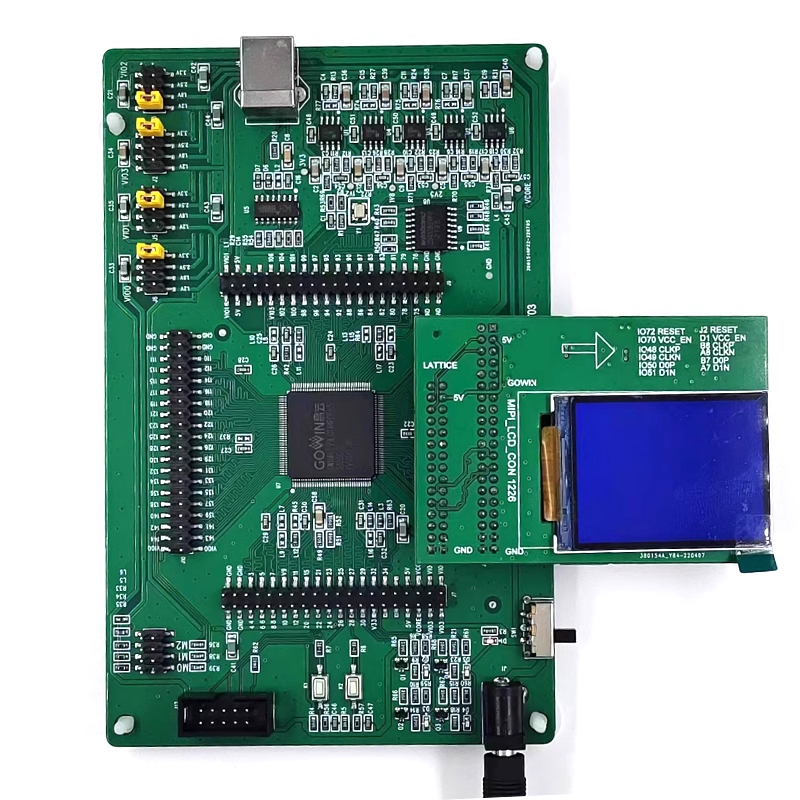

设备测试图片如下,按键可以切换MIPI测试图案。

二:lattice crosslink测试方案

直接用MIPI DPHY的IP设定要求

设定DSI模式,MIPI LANE的速率。PHY参考时钟。

latticemipi latticemipi_inst

(

.clk_txhsen(phy_clk_hsen),

.clk_txhsgate(phy_clk_gate),

.clk_txlpen(mipi_lpclk_en),

.clk_txlpn(mipi_lpclk_n),

.clk_txlpp(mipi_lpclk_p),

.d0_txhsen(phy_hs_en),

.txdata(phy_hs_data),

.d0_txlpen(mipi_lp_en),

.d0_txlpn(mipi_lp_n),

.d0_txlpp(mipi_lp_p),

.pd_pll(0),

.refclk(sys_clk),

.usrstdby(0),

.txhsbyteclk(byte_clk),

.lock(byteclk_rstn),

// .d0_rxlpn( )

// .d0_rxlpp( )

.clk_n(clk_n),

.clk_p(clk_p),

.data_n(data_n),

.data_p(data_p)

);

注意LATTICE的Crosslink的mipi ip是输出hs的时钟。所以驱动mipi 要必须了解mipi的正确的时钟,否则没办法使用。

浙公网安备 33010602011771号

浙公网安备 33010602011771号