Lattice Crosslink开发简介

选择lattice的Crosslink器件,大多是因为它功耗比较低、价格便宜,开发也比较简单,相对来说更容易上手。大部分用在手机屏,摄像头模组和平板方面。

Crosslink的开发工具是Diamond,内部逻辑资源lut大概有6k,并且有两个MIPI DPHY硬核,所以用户经常用它做MIPI接口桥接芯片。

硬件设计

Crosslink硬件设计,个人觉得有几份资料是必看的,我现在罗列出来供大家参考。

(1)Crosslink数据手册、Hardware Checklist、pinout信息等。资料下载链接为

http://www.latticesemi.com/en/Products/FPGAandCPLD/CrossLink

数据手册:简单介绍器件基本特性,比如逻辑资源、管脚数量、管脚速率、bank电压等等。

Hardware Checklist:用户画完原理图之后,再次通过这份文档检查一下,如果没有发现问题,那么证明原理图起码没有引脚分配之外的问题。

除此之外,官网还有一些PCB布局布线的一些推荐文档,原理图库,参考设计等,非常有用。

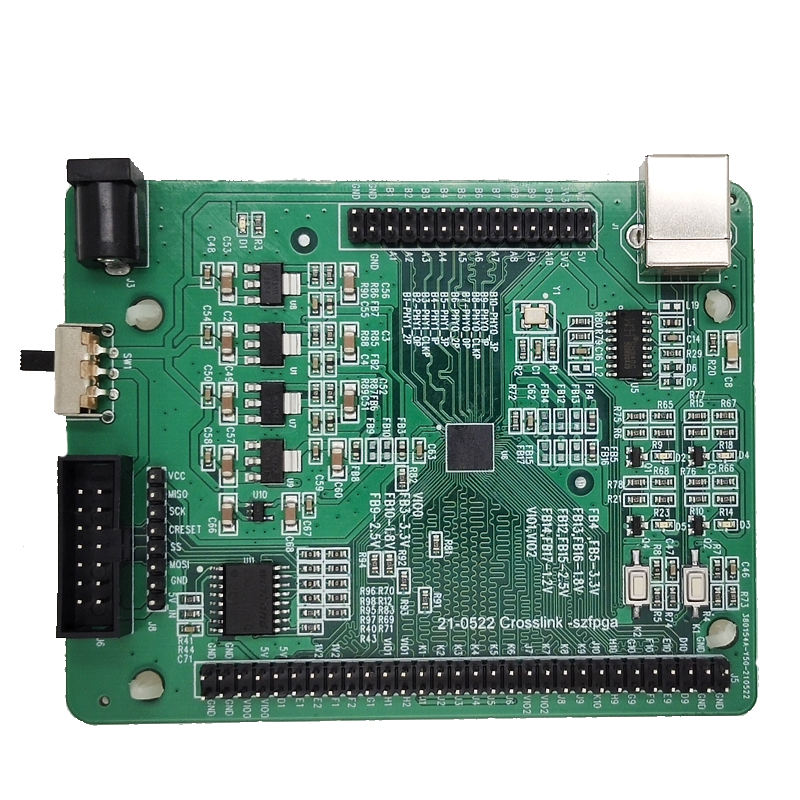

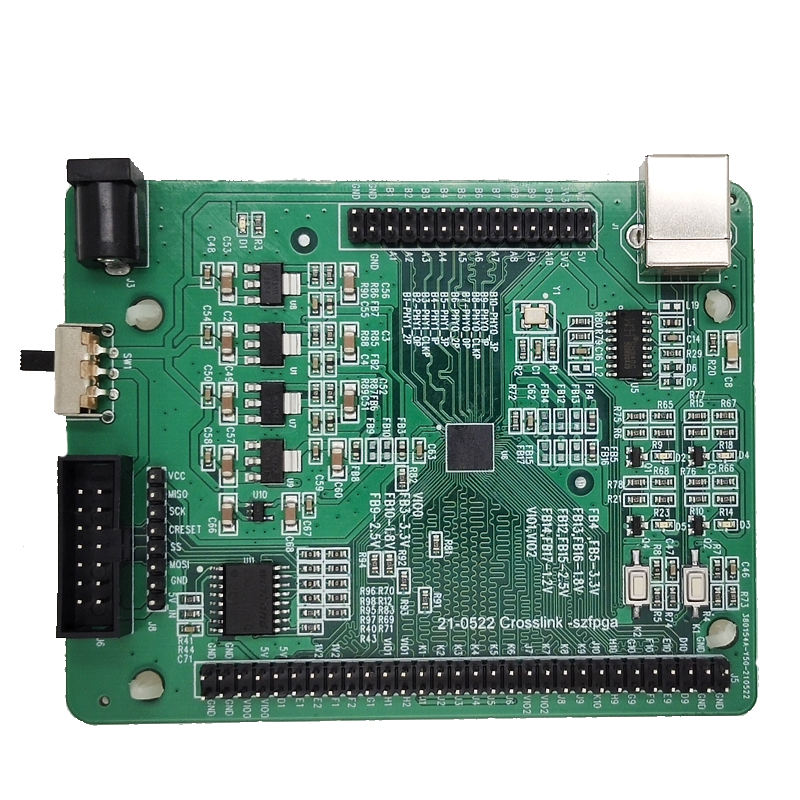

(2)crosslink开发板

在用户开发之前,如果能够得到一块开发板,那无疑非常有用,这不仅可以帮助我们快速熟悉器件软硬件环境,而且还可以作为一个硬件工程师开发的良好范本。上述链接pdf文档后面,有Crosslink的参考原理图,新用户可以借助它快速绘制原理图。

除了上述官网提供的资料以外,Lattice Crosslink还经常会遇到管脚分配的问题;

该开发板比lattice官方开发板降低了设计难度。把基本上IO引脚做了等长,MIPI引脚引出。板上可以通过选择不同bank的电压。

Crosslink的开发工具是Diamond,内部逻辑资源lut大概有6k,并且有两个MIPI DPHY硬核,所以用户经常用它做MIPI接口桥接芯片。

硬件设计

Crosslink硬件设计,个人觉得有几份资料是必看的,我现在罗列出来供大家参考。

(1)Crosslink数据手册、Hardware Checklist、pinout信息等。资料下载链接为

http://www.latticesemi.com/en/Products/FPGAandCPLD/CrossLink

数据手册:简单介绍器件基本特性,比如逻辑资源、管脚数量、管脚速率、bank电压等等。

Hardware Checklist:用户画完原理图之后,再次通过这份文档检查一下,如果没有发现问题,那么证明原理图起码没有引脚分配之外的问题。

除此之外,官网还有一些PCB布局布线的一些推荐文档,原理图库,参考设计等,非常有用。

(2)crosslink开发板

在用户开发之前,如果能够得到一块开发板,那无疑非常有用,这不仅可以帮助我们快速熟悉器件软硬件环境,而且还可以作为一个硬件工程师开发的良好范本。上述链接pdf文档后面,有Crosslink的参考原理图,新用户可以借助它快速绘制原理图。

除了上述官网提供的资料以外,Lattice Crosslink还经常会遇到管脚分配的问题;

该开发板比lattice官方开发板降低了设计难度。把基本上IO引脚做了等长,MIPI引脚引出。板上可以通过选择不同bank的电压。

(1) Crosslink有两个MIPI硬核,如果用户只用一个MIPI硬核,那么软件会把管脚自动分配到DPHY0。Crosslink每个MIPI硬核有四个lane,如果用户只用了一个lane,那么软件会自动把管脚分配到lane0 。根据布线结果看映射什么地方。

也可以用约束语句,约束IP核生产的引脚在对应MIPI通道上。

(2) Crosslink下载方式有两种,分别是IIC下载方式和SPI下载方式。软件默认SPI下载方式,会自动分配引脚,用户不用手动分配。

要注意有配置有两种模式,一个外部spi-flash和内部nvcm。内部ncvm是一次性编程不能再次修改。要注意。

(3) Crosslink有些IP会使用到特殊引脚,用户任意分配引脚会导致软件编译不了,出现错误。

除了上述问题之外,lattice管脚分配可能还会遇到一些问题,所以建议用户在分配完引脚之后,做一下“管脚评估”,这样就可以避免管脚分配错误带来的问题。

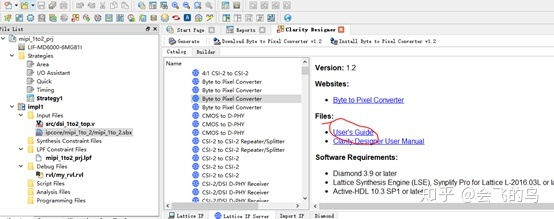

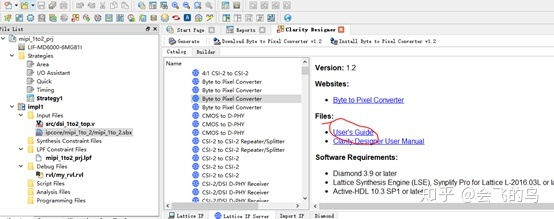

软件设计

Crosslink的代码开发工具是lattice Diamond,关于这个工具如何使用,我已在另一篇文章简单讲过,在这里不再赘述。打开IP核生成界面,里面有很多Crosslink上能够使用的IP核,并且每个IP核都有简单介绍,非常方便。

也可以用约束语句,约束IP核生产的引脚在对应MIPI通道上。

(2) Crosslink下载方式有两种,分别是IIC下载方式和SPI下载方式。软件默认SPI下载方式,会自动分配引脚,用户不用手动分配。

要注意有配置有两种模式,一个外部spi-flash和内部nvcm。内部ncvm是一次性编程不能再次修改。要注意。

(3) Crosslink有些IP会使用到特殊引脚,用户任意分配引脚会导致软件编译不了,出现错误。

除了上述问题之外,lattice管脚分配可能还会遇到一些问题,所以建议用户在分配完引脚之后,做一下“管脚评估”,这样就可以避免管脚分配错误带来的问题。

软件设计

Crosslink的代码开发工具是lattice Diamond,关于这个工具如何使用,我已在另一篇文章简单讲过,在这里不再赘述。打开IP核生成界面,里面有很多Crosslink上能够使用的IP核,并且每个IP核都有简单介绍,非常方便。

关于Crosslink软件部分,建立工程的流程和其他器件基本相同,我就不再展开写了。这一块我比较想让大家知道的是,Crosslink软件调试。

大家知道,Crosslink只有SPI和iic下载口,并没有JTAG调试口。Lattice原意是用户直接用他们生成好的IP,只需要分配好引脚即可完成开发,但是后续Crosslink IP核在使用的过程中有时会遇到问题,而且用户有可能会在Crosslink上开发一些自己的代码,经常会遇到需要调试代码的状况,所以后续lattice建议用户在开发Crosslink过程中,把JTAG口预留出来。

首先我要说一下,我上面说的JTAG是指Crosslink用软件模拟出来的JTAG,这个JTAG口不能用于下载,只能用来调试。

Crosslink 模拟JTAG调试步骤

(1)建立完整的Crosslink工程。

大家知道,Crosslink只有SPI和iic下载口,并没有JTAG调试口。Lattice原意是用户直接用他们生成好的IP,只需要分配好引脚即可完成开发,但是后续Crosslink IP核在使用的过程中有时会遇到问题,而且用户有可能会在Crosslink上开发一些自己的代码,经常会遇到需要调试代码的状况,所以后续lattice建议用户在开发Crosslink过程中,把JTAG口预留出来。

首先我要说一下,我上面说的JTAG是指Crosslink用软件模拟出来的JTAG,这个JTAG口不能用于下载,只能用来调试。

Crosslink 模拟JTAG调试步骤

(1)建立完整的Crosslink工程。

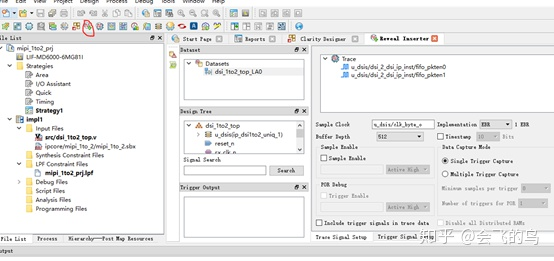

(2)点击reveal insert按钮,在工程中插入reveal analyzer,分配好采样时钟、触发信号、采样信号等,然后保存为.rvl文件。

(3)重新编译工程。编译好之后,打开Reports标签页下的Signal/Pad,查看Diamond软件给JTAG分配的引脚。当然,用户也可以分配好JTAG引脚之后再编译,如果引脚分配不合理,Diamond就会给出错误报告。

(4)将编译好的工程bit文件通过SPI或者IIC口下载到Crosslink,然后连接虚拟JTAG引脚,打开Reveal Analyzer,运行,进行调试分析。

浙公网安备 33010602011771号

浙公网安备 33010602011771号