国产gowin开发板GW1NR-9K的PSRAM使用说明

开发板子采用GW1NNR-LV9LQ144PC6/I5 FPGA器件。具有低功耗,瞬时启动,高安全性,低成本,方便扩展等特点。本开发板价格价格便宜,板子扩张性容易,帮助用户比较快速进入国产FPGA学习能力。

开发板集成多个GPIO接口和多个LVDS接口,电压可以从3.3,2.5,1.8,1.2V选择。用户可以选择不同电压适配不同的IO口。其中每个VCCIO也是独立供电,可以很简单改装成其他的不同bank不同电压要求。

芯片资源GW1NNR-LV9LQFP144的资源有8640的LUT4,并且还有26个18K SRAM快,2个PLL锁相环,内部自带PSRAM 64M空间,

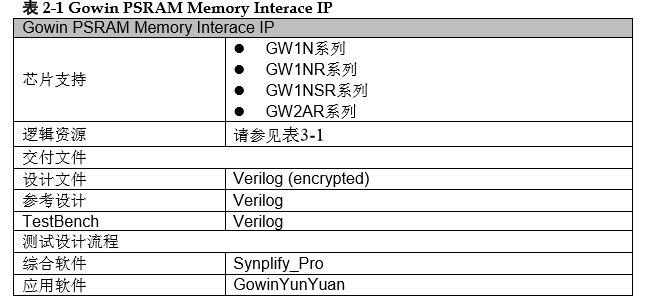

Gowin PSRAM Memory Interface IP是一个通用的PSRAM内存接口IP, 符合PSRAM标准协议。该IP包含PSRAM内存控制逻辑(Memory Controller Logic)与对应的物理层接口(Physical Interface,PHY)设计。Gowin PSRAM Memory Interace IP 为用户提供一个通用的命令接口,使其与 PSRAM 内存 芯片进行互连,完成用户的访存需求。

- 能与标准的 PSRAM 器件接口;

- 支持存储器数据路径宽度为 8、16、24、32、40、48、56 和 64 位;

- 支持 x8 数据宽度的内存芯片;

- 可编程突发长度 16、32、64、128;

- 时钟比例为 1:2

- 支持初始延时为 6;

- 支持固定延时模式;

- 支持电源关闭选项;

- 可配置的驱动强度;

- 可配置的自刷新区域;

- 可配置的刷新速率;

- 单通道双通道两种操作模式 IP 可选。

Gowin PSRAM Memory Interace IP 可支持的数据速率与效率为:

- 最高工作数据速率 333Mbps;

- 突发长度 128,带宽效率为 74%;

- 突发长度 64,带宽效率为 59%;

- 突发长度 32,带宽效率为 42%;

- 突发长度 16,带宽效率为 26%

Gowin PSRAM Memory Interace IP 基本结构如图 4-1 所示,主要包含 Memory Controller Logic、Physical Interface 等模块。。 图 4-1 中的 User Design 是 FPGA 中需要与外部 PSRAM SDRAM 芯片 所连接的用户设计。 图 4-1

Memory Controller Logic 是 Gowin PSRAM Interace IP 的逻辑模块,位 于 User Design 与 PHY 之间。Memory Controller Logic 接收来自用户接口 的命令、地址与数据,并按照一定逻辑顺序进行存储。 用户发送的写、读等命令和地址在 Memory Controller Logic 中进行排序 重组,组合成满足 PSRAM 协议的数据格式。同时,写数据时 Memory Controller Logic 会对数据进行重组和缓存,以满足命令和数据之间的初始延 时值,读数据时,Memory Controller Logic 会对读回的数据进行采样和重组, 恢复成正确数据。 PSRAM Memory Controller 主要由以下几个模块组成:CMD 单元、 WR_Data 单元、RD_Data 单元等,主要结构如图 4-2 所示。

PSRAM 必须经过读校准操作才能进行正常的写、读操作。因此上电后 PHY 会对 PSRAM 进行初始化读校准操作,初始化完成后返回初始化完成标 志 init_calib,单通道 PSRAM IP 会将两颗 psram 颗粒同时初始化,而双通 道 IP 则是两颗 psram 颗粒各自初始化,并将两个初始化完成信号分别送出 给用户使用。

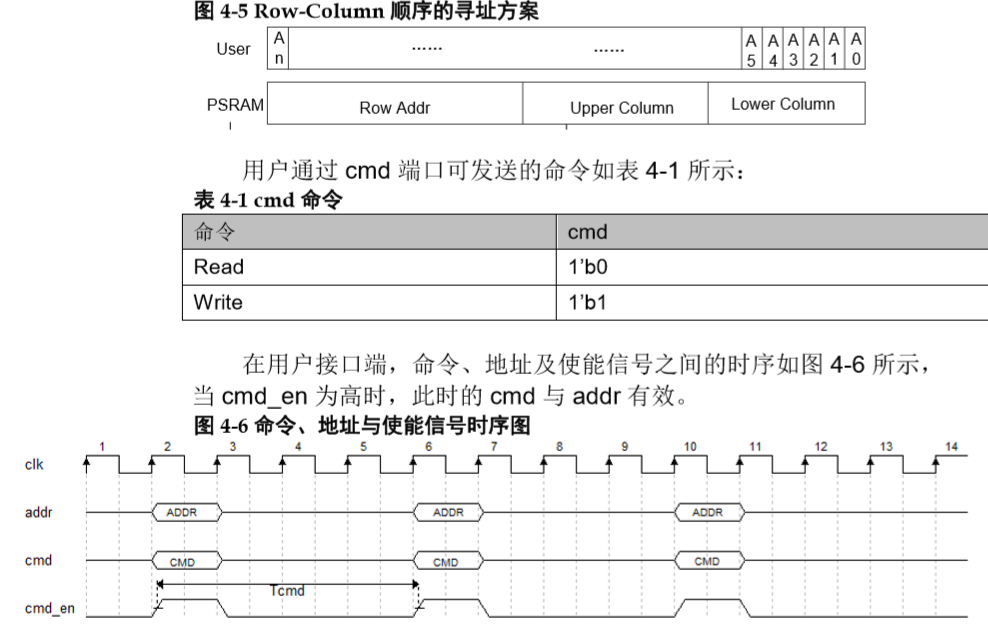

用户可通过 addr、cmd、cmd_en 等用户接口发送操作命令与地址。

addr 为地址数据端口; 连续地址写操作时,相邻两次操作地址自加突发长度/2,连续地址读操作 相同;

cmd 为命令数据端口;

cmd_en 为地址与命令使能信号,高电平有效;

双通道 PSRAM IP 和单通道 PSRAM IP 的操作方式一致,但是双通道

PSRAM IP 两个通道的命令和地址是独立的,需要分别给出控制信号。 在应用中,用户接口的地址总线与物理内存的 ROW、Upper Column、 Lower Column 之间存在一定的映射关系,在本设计中,按照 ROW-Upper Column-Lower Column 的顺序进行依次排列,其寻址方案如图 4-5 所示。用 户在应用中,只需按照需要给出地址,不需要关心映射关系。

用户在使用 PSRAM 时,读写命令间隔需根据颗粒 tRWR 值进行计算, 以 166M 时钟,颗粒使用 W955D8MBY 为例,tRWR 最小值为 36ns,即读 写命令间隔需要大于 6 个时钟周期,在实际使用读写切换中,建议用户在写 数据全部写入后再进行读取操作,在读数据全部读出后,再进行写操作; 在用户端实际使用时两个命令(写-读/读-写/写-写/读-读)间隔需满足最 小间隔周期(图 4-8 中 Tcmd 周期数),即突发长度为 16 时,命令间隔最小 为 15 个时钟周期;突发长度为 32 时,命令间隔最小为 19 个时钟周期;突 发长度为 64 时,命令间隔最小为 27 个时钟周期;突发长度为 128 时,命令 间隔最小为 43 个时钟周期。

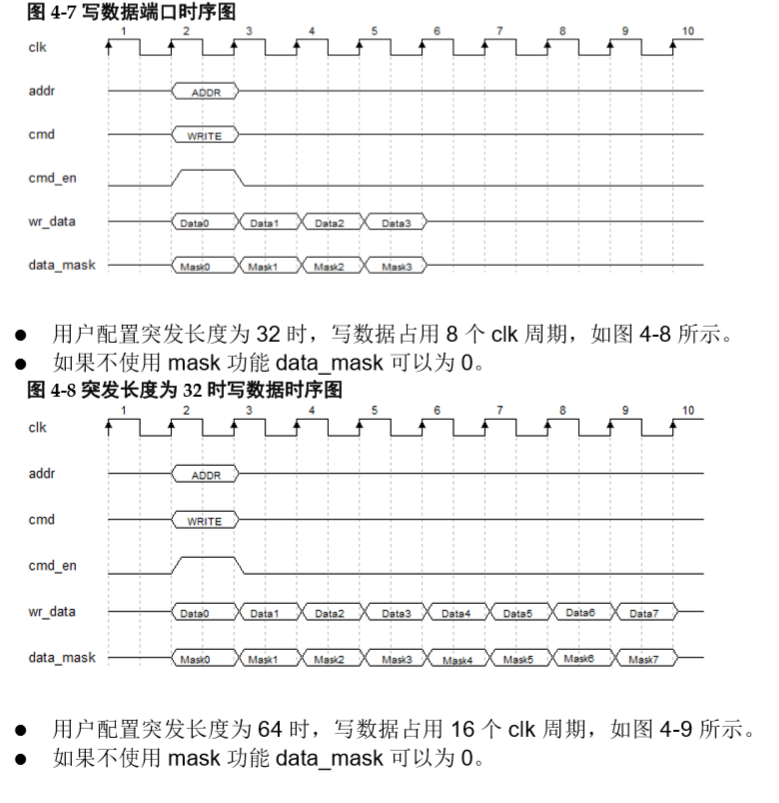

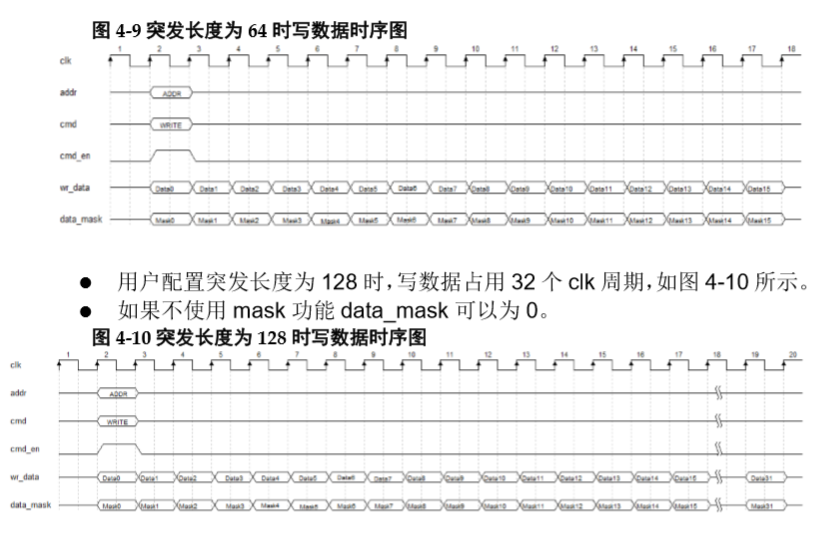

写数据

用户可通过用户接口 wr_data、data_mask 等端口将写数据发送给 Gowin PSRAM Memory Interface IP,写数据经过处理后会发送给 PSRAM 颗粒。

wr_data 为写数据端口;

data_mask 为写遮掩端口;

写数据通道与命令通道之间存在多种时序情况,下图以突发长度为 16 为 例;

双通道 PSRAM IP 与单通道 PSRAM IP 写操作模式一致,但是双通道 PSRAM IP 两个通道的数据端口是独立的,需要分别给出写数据;

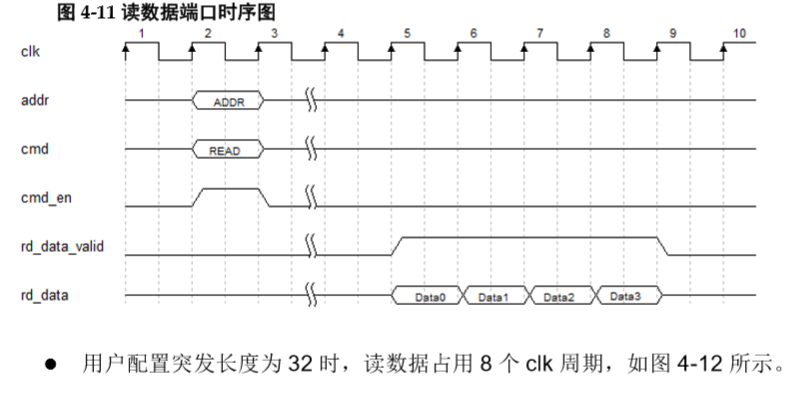

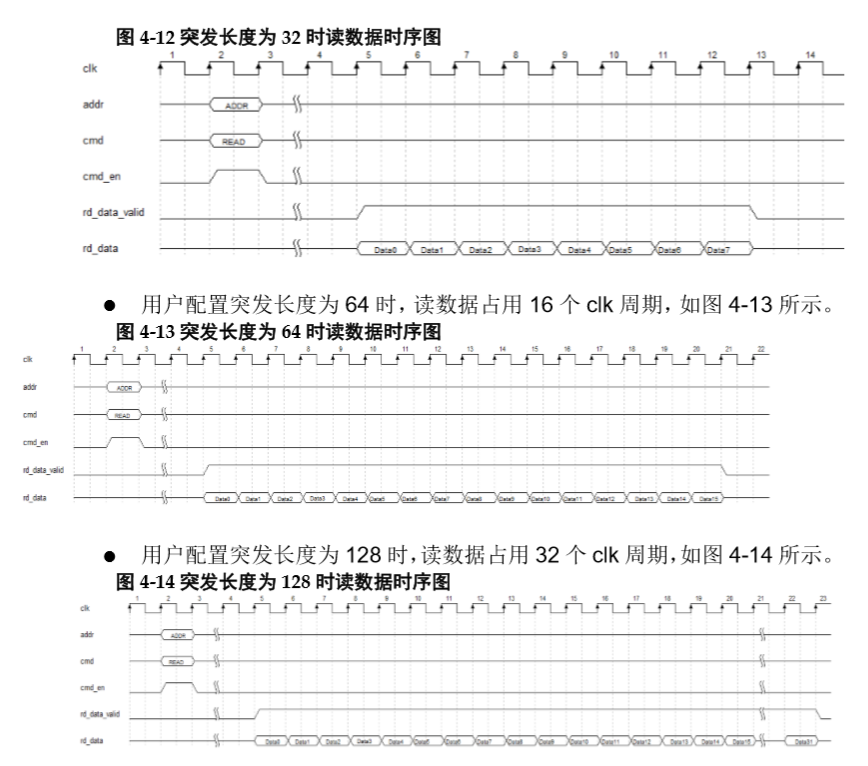

读数据

用户可通过用户接口rd_data、rd_data_valid读取PSRAM返回的数据。

端口 rd_data 为返回的读数据端口;

端口信号 rd_data_valid 为读数据有效端口,当其为高电平时,指示此时 返回的 rd_data 有效;

读数据通道与命令通道之间存在多种时序情况,下图以突发长度为 16 为 例;

双通道 PSRAM IP 与单通道 PSRAM IP 读操作模式一致,但是双通道 PSRAM IP 两个通道的数据端口是独立的,需要分别接收 rd_data_valid 信号和 rd_data 数据

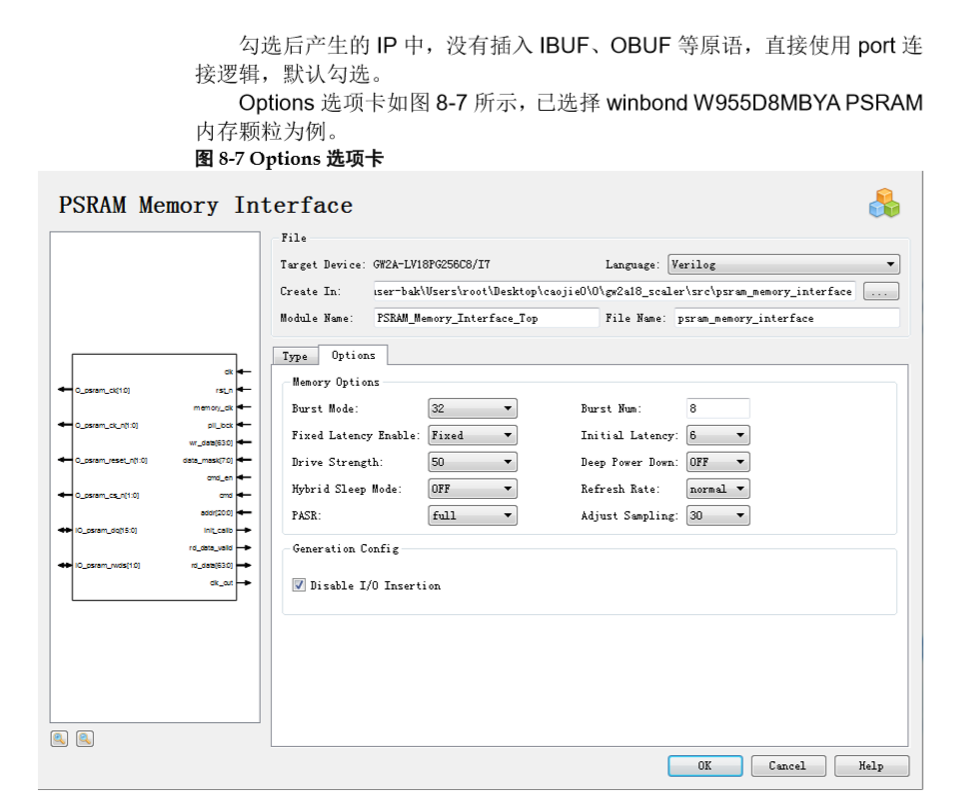

配置选项默认。

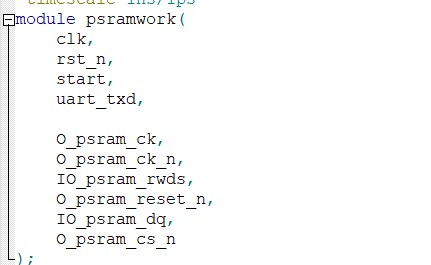

代码要记得顶层必须输出基本的IO口。

用上面的开发板子,执行测试。

按键KEY1的时候,写入psram的数据,并且都psram的数据,输出到串口上面。

十六进制显示,2个停止位,115200波特率,数据位8位,没有校验位。