Verilog HDL(Verilog)

Verilog 的历史

- 1983 年,Gateway Design Automation公司推出了Verilog 语言,开发了仿真与验证工具。

- 1983年,verilog 的仿真器-Verilog-XL被推出,仿真速度快具有交互式调试手段。

- 1987年,synopsys公司的综合软件开始接受Verilog输入

- 1989年,Cadence公司收购了GDA公司,进一步扩大了Verilog的影响。

- 1990年,创立了Open Verilog International成立,推广了Verilog HDL

- 1993年,OVI 推出了Verilog2.0,作为IEEE提案提出申请

- 1995年,Verilog HDL标准IEEE1364-1995(95标准)

- 2001年,IEEE发布了Verilog HDL标准IEEE1364-2001(01标准)

Verilog 现状

- 目前Verilog HDL是最广泛使用的,具有国际标准支持的硬件描述语言,绝大多数的EDA厂家都支持Verilog HDL语言。

- 在工业界和ASIC设计领域,Verilog HDL 应用广泛。

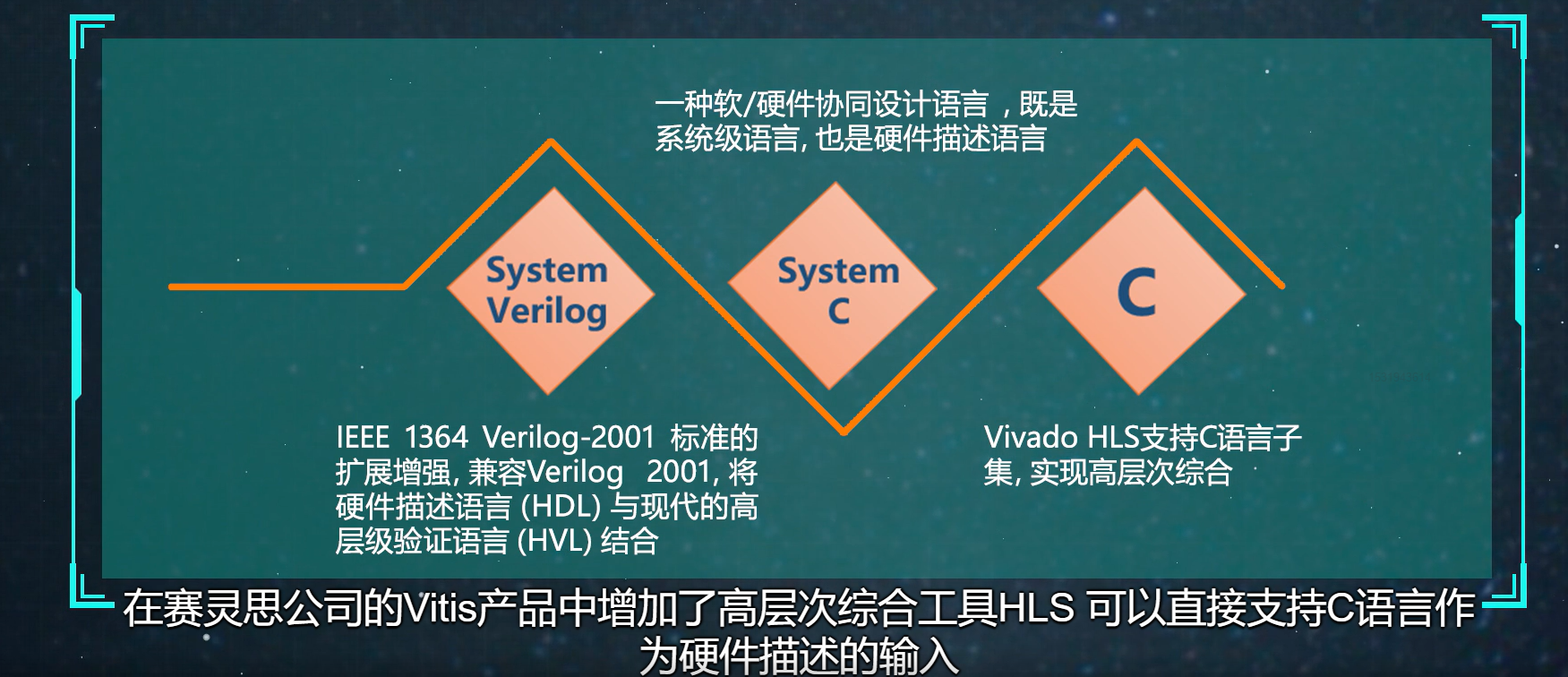

Verilog语言的新发展:

![]()

Very-heigh-Speed Integrated circuit HardWare Description Language(VHDL)

历史

- 诞生于1982年

- 1987年底被美国国防部认定为硬件标准描述语言

HDL hardware description language

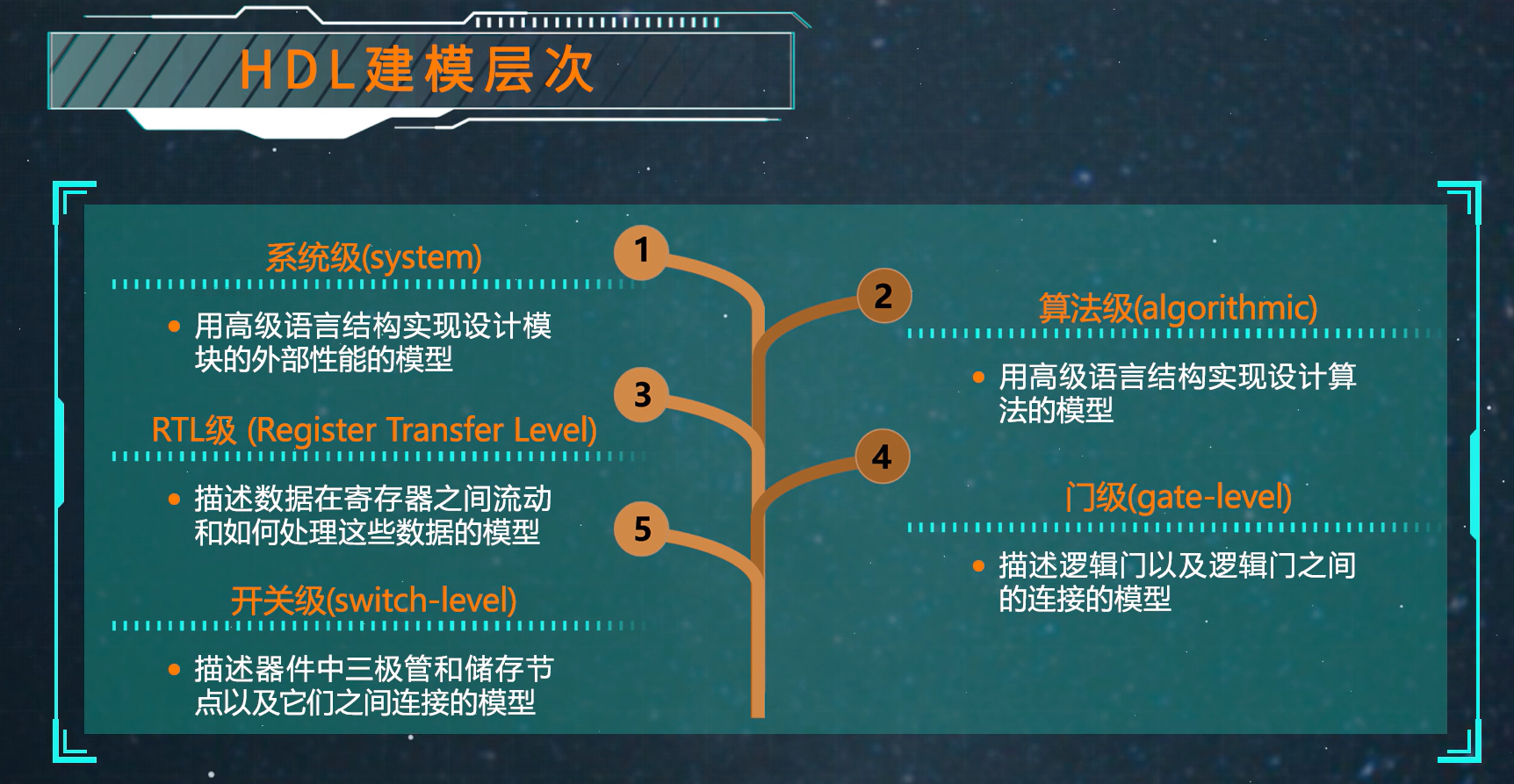

建模层次

![]()

- 系统级:用高级语言结构实现设计模块的外部性能的模型

- 算法级:用高级语言结构实现设计算法的模型

- RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型

- 门级:描述逻辑门以及逻辑门之间的连接的模型

- 开关级:描述器件中三极管和储存节点以及它们之间连接的模型

Verilog 语言和 VHDL语言的建模能力的区别:

![]()

- 目前Verilog HDL语言在2001标准之后拓展了系统级的描述能力(工业界主流语言)

共同点:

- 都能形式化抽象表示电路行为和结构

- 都能支持逻辑设计中层次与范围的描述

- 具有电路仿真和验证的机制

- 于工艺无关,不专门面向于FPGA

不同点:

- Verilog 于C语言更相似,语法灵活

- VHDL源于Ada语言,语法严格

- Verilog更适合ASIC设计

posted on

2024-09-18 22:32

For_CC

阅读(

344)

评论()

收藏

举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号