深入理解计算机系统笔记5:虚拟内存

为了更加有效地管理存储器且少出错,现代系统提供了一种对主存的抽象概念,叫做虚拟存储器(VM)。虚拟内存是硬件异常,硬件地址翻译,主存,磁盘文件和内核软件的完美交互。它为每个进程提供一个大的,一致的和私有的地址空间。它提供了3个重要能力。

- 将主存看成磁盘上的地址空间的高速缓存,在主存中只保留了活动区域,并根据需要在磁盘和主存间来回传送数据,高效使用主存。

- 为每个进程提供一致的地址空间,简化内存管理

- 保护了每个进程的地址空间不被其他进程破坏。

逻辑地址(Logical Address):程序中指令所用地址(进程所在地址空间),也称为虚拟地址(Virtual Address,简称VA)

物理地址(Physical Address,简称PA):存放指令或数据的实际内存地址,也称为实地址、主存地址。物理地址(Physical Address,PA):计算机系统的主存被组织为M个连续的字节大小的单元组成的数组。每个字节的地址叫物理地址.

CPU访问存储器的最自然的方式使用物理地址,这种方式称为物理寻址。早期的PC,数字信号处理器,嵌入式微控制器以及Cray超级计算机使用物理寻址。

现代处理器使用的是虚拟寻址(virtual addressing)的寻址形式。CPU通过生成一个虚拟地址(Virtual address,VA)来访问主存。将虚拟地址转换为物理地址叫做地址翻译(address translation)。地址翻译需要CPU硬件和操作系统之间的紧密结合。CPU芯片上有叫做内存管理单元(Memory Management Unit,MMU)的专用硬件,利用存储在主存中的查询表来动态翻译虚拟地址,查询表由操作系统管理。

虚拟内存/虚拟存储系统

虚拟存储技术的引入用来解决一对矛盾

• 一方面,由于技术和成本等原因,主存容量受到限制

• 另一方面,系统程序和应用程序要求主存容量越来越大

虚拟存储技术的实质

• 程序员在比实际主存空间大得多的逻辑地址空间中编写程序

• 程序执行时,把当前需要的程序段和相应的数据块调入主存,其他暂不用的部分存放在磁盘上

• 指令执行时,通过硬件将逻辑地址(也称虚拟地址或虚地址)转化为物理地址(也称主存地址或实地址)

• 在发生程序或数据访问失效(缺页)时,由操作系统进行主存和磁盘之间的信息交换

虚拟存储器机制由硬件与操作系统共同协作实现,涉及到操作系统中的许多概念,如进程、进程的上下文切换、存储器分配、虚拟地址空间、缺页处理等。

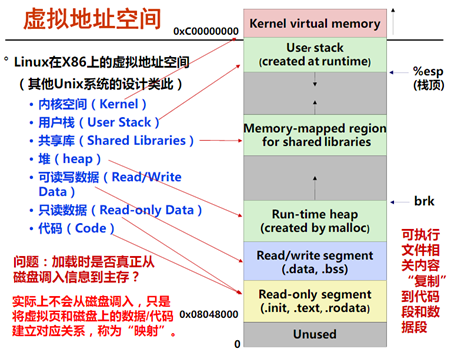

虚拟地址空间

地址空间(address space)是一个非负整数地址的有序集合。如果地址空间中整数是连续的,我们说它是线性地址空间(linear address space)。为了简化讨论,我们总是假设使用线性地址空间。在一个带虚拟存储器的系统中,CPU从一个有N=2^n个地址的地址空间中生成虚拟地址,这个地址空间称为虚拟地址空间(virtual address space)。一个地址空间大小是由表示最大地址所需要的位数来描述的。如N=2^n个地址的虚拟地址空间叫做n位地址空间。现在操作系统支持32位或64位。一个系统还有物理地址空间,它与系统中物理存储器的M=2^m(假设为2的幂)个字节相对应。

地址空间的概念很重要,因为它区分了数据对象(字节)和它们的属性(地址)。每个字节(数据对象)可以有多个 独立的地址(属性),每个地址都选自不同的地址空间。主存中的每个字节都有一个在虚拟地址空间的虚拟地址,还有一个在物理地址空间的 物理地址。

虚拟存储机制为程序提供了一个极大的虚拟地址空间也称为逻辑地址空间.它是主存和磁盘存储器的抽象。虛存机制带来了一个假象.使得每个进程好像都独占使用主存.并且主存空间极大。这有三个好处

①每个进程具有一致的虚拟地址空间.从而可以简化存储管理;

②它把主存看成是磁盘存储器的一个缓存,在主存中仅保存当的活动的程序段和数据区.并且根据需要在磁盘和主存之间进行信息交换,通过这种方式.使有限的主存空间得到了有效利用;

③每个进程的虚拟地址空间是私有的.因此,可以保护各自进程不被其他进程破坏。

|

|

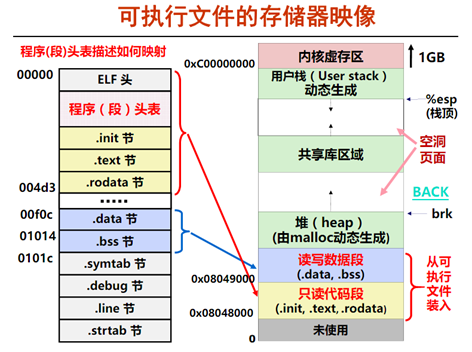

分页基本思想:

• 内存被分成固定长且比较小的存储块(页框、实页、物理页)

• 每个进程也被划分成固定长的程序块(页、虚页、逻辑页)

• 程序块可装到存储器中可用的存储块中

• 无需用连续页框来存放一个进程

• 操作系统为每个进程生成一个页表

• 通过页表(page table)实现逻辑地址向物理地址转换(Address Mapping )

实现虚拟存储器管理,需考虑:

块大小(在虚拟存储器中“块”被称为“页 / Page”)应多大?

主存与辅存的空间如何分区管理?

程序块 / 存储块之间如何映像?

逻辑地址和物理地址如何转换,转换速度如何提高?

主存与辅存之间如何进行替换(与Cache所用策略相似)?

页表如何实现,页表项中要记录哪些信息?

如何加快访问页表的速度?

如果要找的内容不在主存,怎么办?

如何保护进程各自的存储区不被其他进程访问?

这些问题是由硬件和OS共同协调解决的!

有三种虚拟存储器实现方式:分页式、分段式、段页式

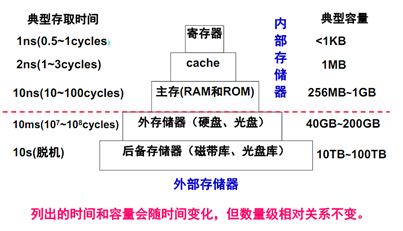

存储器的层次结构

与“Cache--主存”层次相比:

页大小(2KB~64KB)比Cache中的Block大得多! Why?

采用全相联映射!Why?

因为缺页的开销比Cache缺失开销大的多!缺页时需要访问磁盘(约几百万个时钟周期),而cache缺失时,访问主存仅需几十到几百个时钟周期!因此,页命中率比cache命中率更重要!“大页面”和“全相联”可提高页命中率。

通过软件来处理“缺页”!Why?

缺页时需要访问磁盘(约几百万个时钟周期),慢!不能用硬件实现。

采用Write Back写策略! Why?

避免频繁的慢速磁盘访问操作。

地址转换用硬件实现!Why?

加快指令执行

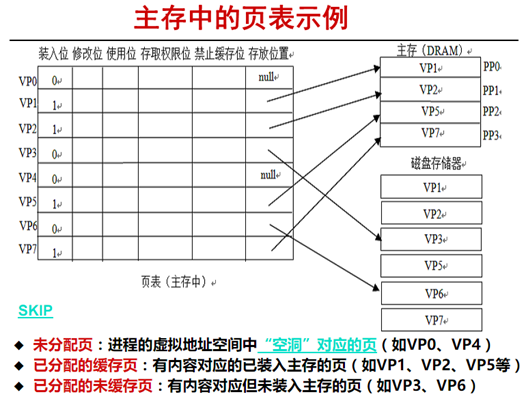

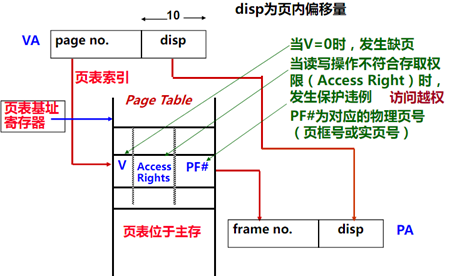

页表

每个进程有一个页表,其中有装入位、修改(Dirt)位、替换控制位、访问权限位、禁止缓存位、实页号。页表首址记录在页表基址寄存器中。页表就是一个页表条目(Page Table Entry,PTE)的数组.虚拟地址空间中每个页在页表的固定偏移量处都有一个PTE.每个PTE由一个有效位和n位地址字段。有效位表明虚拟页是否被缓存。如果有效位存在,那么地址字段指向对应的物理存储器。如果有效位不存在,地址字段要么为NULL,要么指向虚拟页在磁盘所在的位置。

逻辑地址转换为物理地址的过程

问题:虚拟页与主存页框之间采用全相联方式进行映射,为何不像全相联Caceh那样(高位地址是Tag),而高位地址是索引呢?

上图中,VA:虚拟地址,PTEA:页表条目地址,PTE:页表条目,PA:物理地址

图(a)展示页面命中,CPU硬件执行过程

- 第一步:处理器生成虚拟地址,把它传送给

MMU。 - 第二步:

MMU生成PTE地址(PTEA),并从高速缓存/主存请求中得到它。 - 第三步: 高速缓存/主存向MMU返回

PTE。 - 第四步:

MMU构造物理地址(PA),并把它传送给高速缓存/主存。 - 第五步: 高速缓存/主存返回所请求的数据字给处理器。

页面命中完全由硬件处理,与之不同的是,处理缺页需要 硬件和操作系统内核协作完成。

- 第一到三步: 与命中时的一样

- 第四步:

PTE有效位是零,所以MMU触发异常,传递CPU中的控制到操作系统内核中的 缺页异常处理程序。 - 第五步:缺页异常处理程序确定出物理存储页中的牺牲页,如果这个页面已经被修改,则把它换出到磁盘。

- 第六步:缺页异常处理程序调入新的页面,并更新存储器中的

PTE。 - 第七部:缺页异常处理程序返回到原来的进程,再次执行导致缺页的指令,之后就是页面命中一样的步骤。

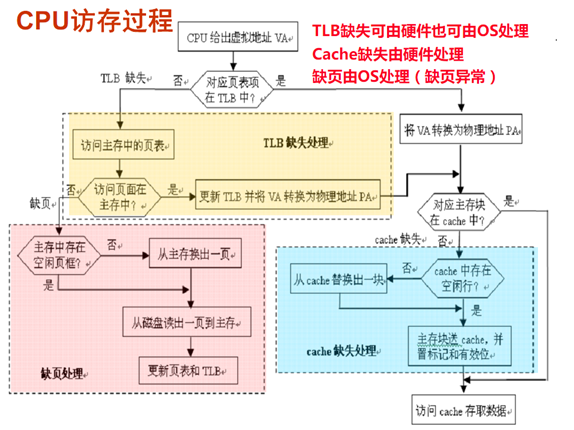

信息访问中可能出现的异常情况

1)缺页( page fault)

产生条件:当Valid(有效位 / 装入位)为 0 时

相应处理:从磁盘读到内存,若内存没有空间,则还要从内存选择一页替换到磁盘上,替换算法类似于Cache,采用回写法,淘汰时,根据“dirty”位确定是否要写磁盘当前指令执行被阻塞,当前进程被挂起,处理结束回到原指令继续执行

2)保护违例( protection_violation_fault )或访问违例

产生条件: 当Access Rights (存取权限)与所指定的具体操作不相符时

相应处理:在屏幕上显示“内存保护错”或“访问违例”信息,当前指令的执行被阻塞,当前进程被终止

Access Rights (存取权限)可能的取值有哪些? R = Read-only, R/W = read/write, X = execute only

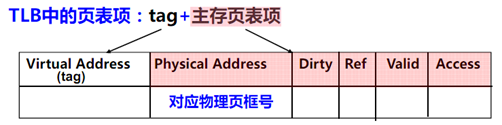

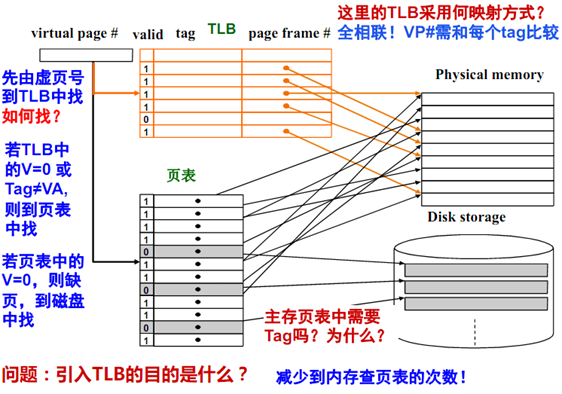

利用TLB加速地址翻译

每次CPU产生一个虚拟地址,MMU就必须查阅一个PTE,以便将虚拟地址翻译为 物理地址。在最糟糕的情况下,会从内存中多取一次数据,代价是几十 到几百个周期 ,如果PTE碰巧缓存在L1中,那么开销就下降到一到两个周期。许多系统都试图消除这样的开销,他们在MMU中包含了一个关于PTE的小缓存,称为翻译后备缓冲器(Translation Lookaside Buffer,TLB),(把经常要查的页表项放到Cache中,这种在Cache中的页表项组成的页表称为Translation Lookaside Buffer )。

TLB是一个小的,虚拟寻址的缓存,一行都保存着一个由单个PTE组成的块。

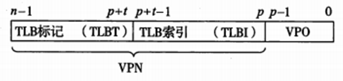

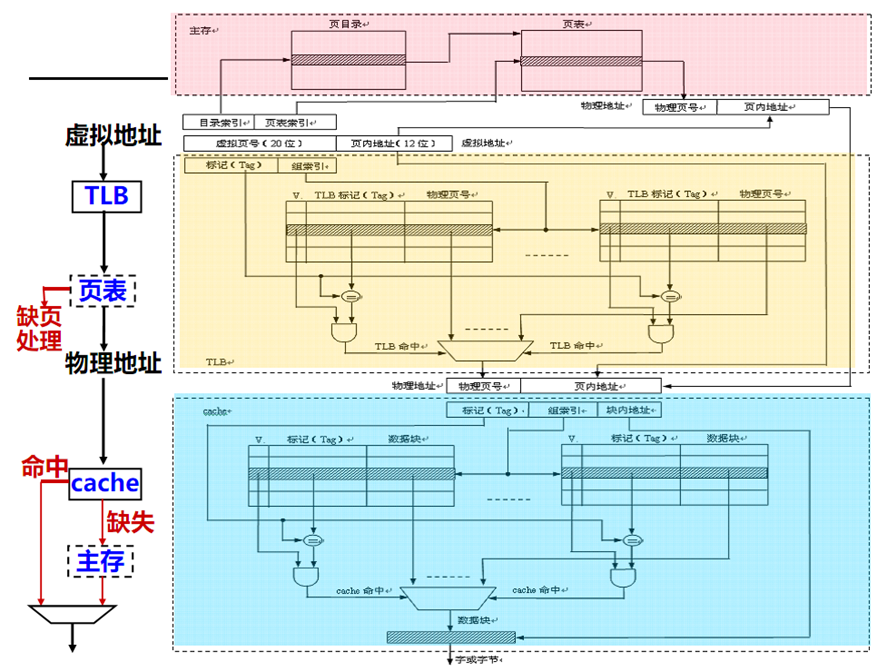

CPU访存时,地址中虚页号被分成tag+index,tag用于和TLB页表项中的tag比较,index用于定位需要比较的表项。

TLB全相联时,没有index,只有Tag,虚页号需与每个Tag比较;TLB组相联时,则虚页号高位为Tag,低位为index,用作组索引。

TLB采用全相联

TLB和cache的访问过程

TLB采用组相联

用于组选择和行匹配的索引和标记字段是从虚拟地址中的虚拟页号中提取出来的。如果TLB有T=2^t个组,那么TLB索引(TLBI)是由VPN的t个最低位组成,(对应于VPO)。TLB标记(TLBT)是由VPN中剩余位组成(对应于VPN)。

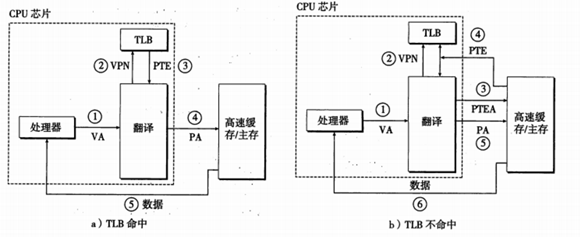

下图展示了当TLB命中时的步骤,关键点:所有的地址翻译步骤都是在芯片上的MMU中执行的,因此非常快。

TLB命中- 第一步:CPU产生虚拟地址。

- 第二步和第三部:

MMU从TLB取出对应的PTE。 - 第四步:

MMU将这个虚拟地址翻译成一个物理地址,发送到高速缓存/主存 - 第五步:

高速缓存/主存所请求的数据字返回给CPU

- 当

TLB不命中的时候,MMU必须从L1缓存或内存中取出相应的PTE,并进行类似缺页处理过程。

浙公网安备 33010602011771号

浙公网安备 33010602011771号