I2C总线之(一)---概述

-

概述:

I²C 是Inter-Integrated Circuit的缩写,发音为"eye-squared cee" or "eye-two-cee" , 它是一种两线接口。

I²C 只是用两条双向的线,一条 Serial Data Line (SDA) ,另一条Serial Clock (SCL)。

SCL:上升沿将数据输入到每个EEPROM器件中;下降沿驱动EEPROM器件输出数据。(边沿触发)

SDA:双向数据线,为OD门,与其它任意数量的OD与OC门成"线与"关系。

-

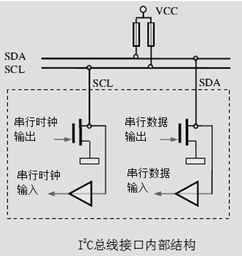

输出级

![]()

每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管,输入缓冲为一只高输入阻抗的同相器,这种电路具有两个特点:

1)由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小常为 1k8, 4k7 and 10k ,但1k8 时性能最好;当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线"与"关系。

2)引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致,为"时钟同步"和"总线仲裁"提供了硬件基础。

-

主设备与从设备

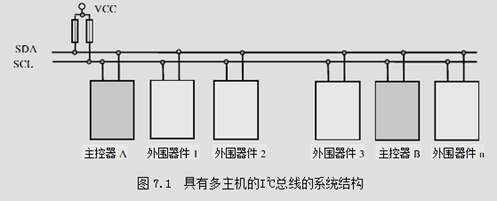

系统中的所有外围器件都具有一个7位的"从器件专用地址码",其中高4位为器件类型,由生产厂家制定,低3位为器件引脚定义地址,由使用者定义。主控器件通过地址码建立多机通信的机制,因此I2C总线省去了外围器件的片选线,这样无论总线上挂接多少个器件,其系统仍然为简约的二线结构。终端挂载在总线上,有主端和从端之分,主端必须是带有CPU的逻辑模块,在同一总线上同一时刻使能有一个主端,可以有多个从端,从端的数量受地址空间和总线的最大电容 400pF的限制。

-

- 主端主要用来驱动SCL line;

- 从设备对主设备产生响应;

二者都可以传输数据,但是从设备不能发起传输,且传输是受到主设备控制的。

4.速率:

普通模式:100kHz;

快速模式:400kHz;

高速模式:3.4MHz;

没有任何必要使用高速SCL,将SCL保持在100k或以下,然后忘了它吧。

来自:http://www.cnblogs.com/BitArt/archive/2013/05/27/3101037.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号