【从零开始自制CPU之学习篇05】总线

总线定义:总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束, 按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。总线是一种内部结构,它是cpu、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路再与总线相连接,从而形成了计算机硬件系统。

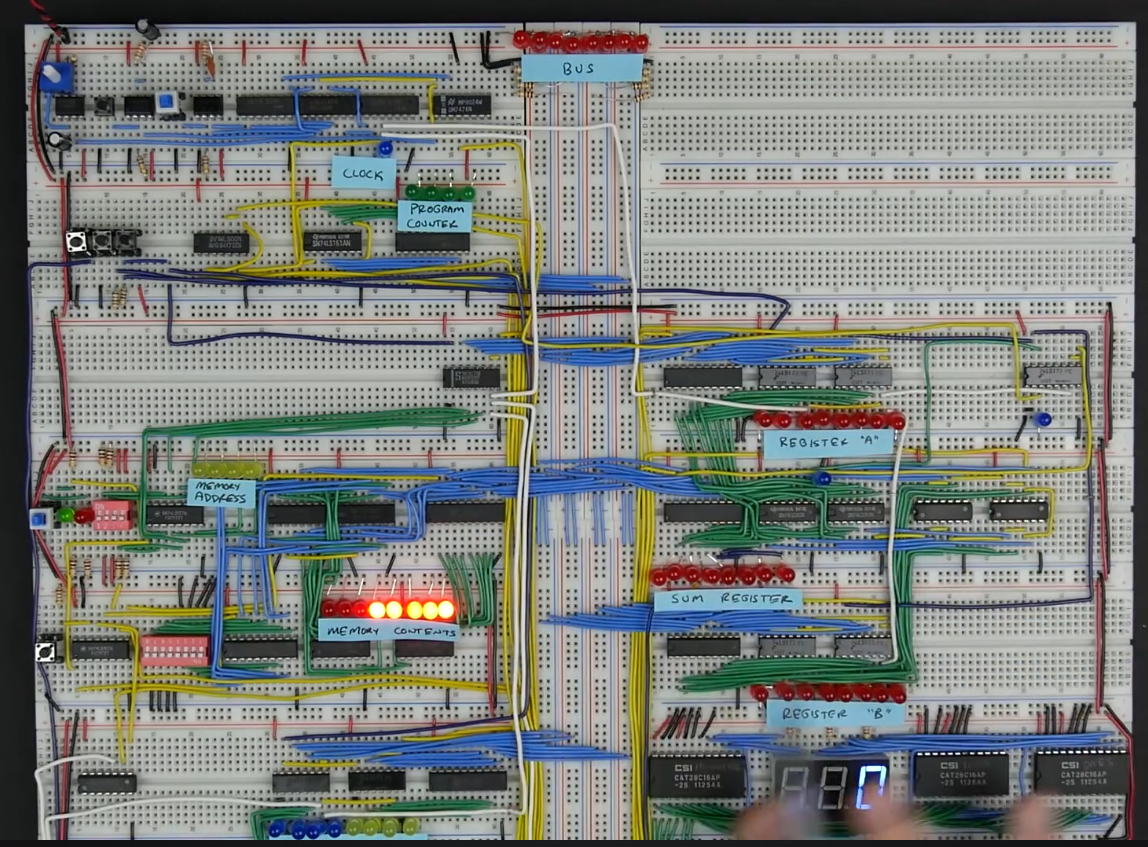

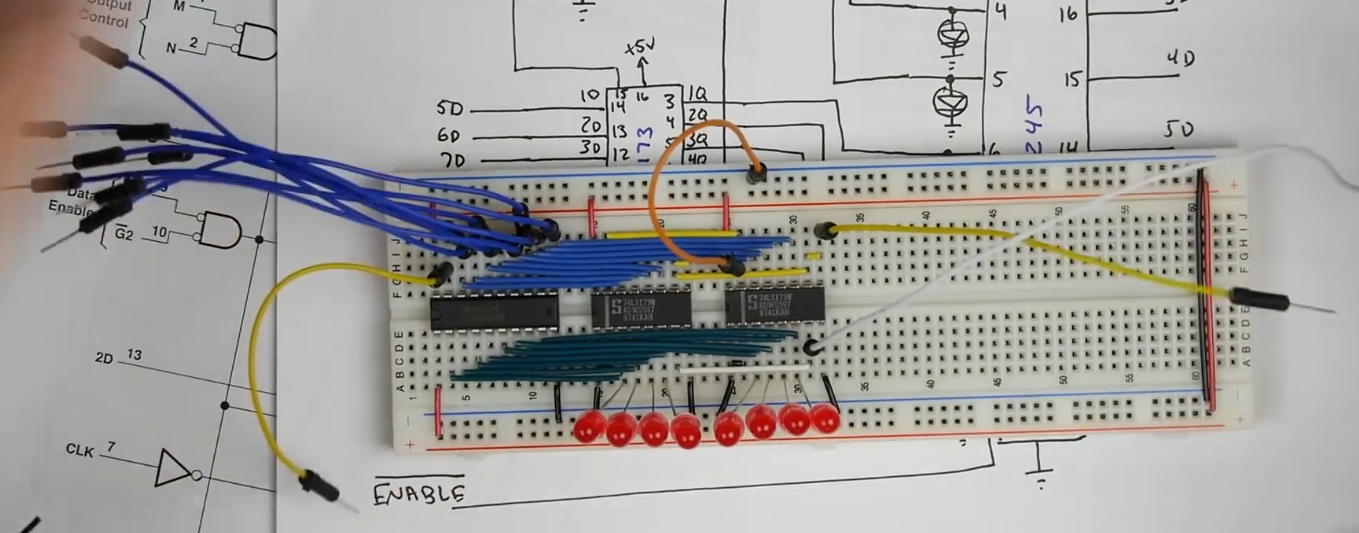

借着说总线,顺便看看成品图(截自教学视频)。中间那四列8孔的就是总线,连接了所有需要往总线写入或者读出的组件,其实总线本质也就是各个组件导线相连的一个中间媒介。

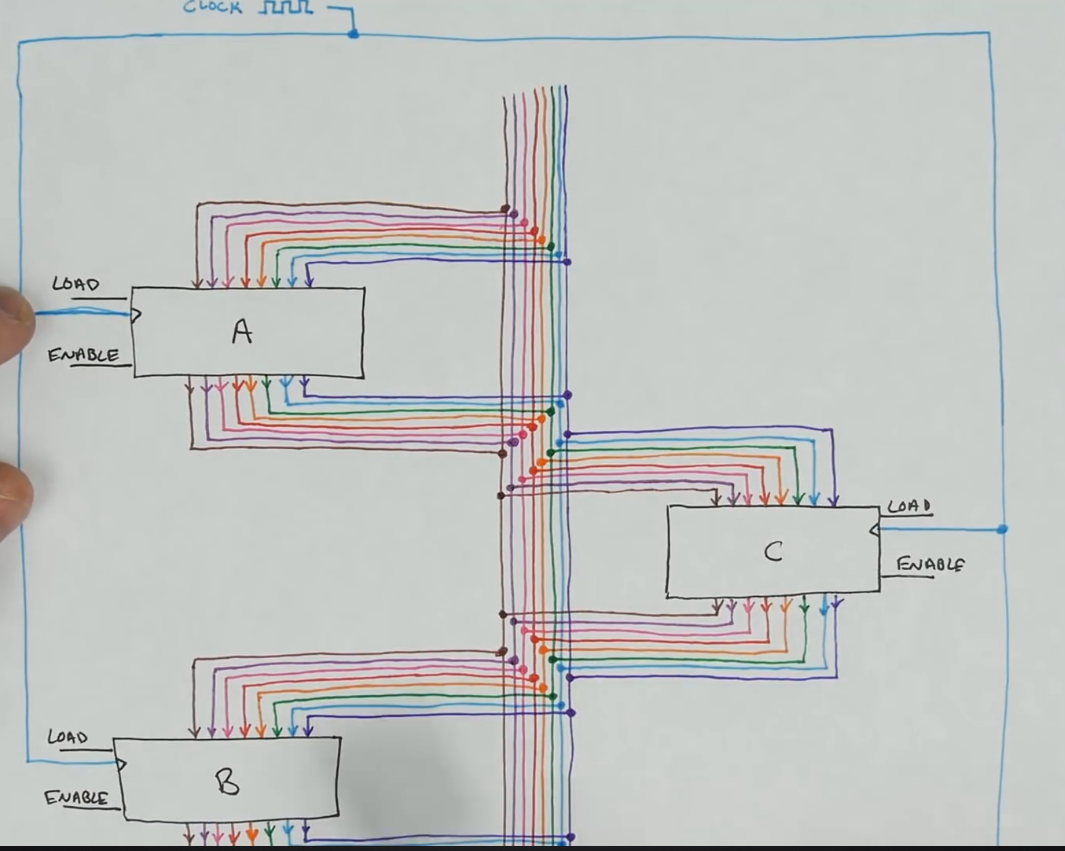

抽象出来之后大概长这个样子,其中ABC分别是各个不同组件,可能是寄存器等等。每个组件有输入和输出端(8位),还有load,时钟,enable信号。

- load即是否存入,同之前的锁存器的en信号类似。

- 时钟不用说了。

- 这里enable信号与之前有所不同,指的是是否输出到总线,如果关闭则不输出,实际上是断开输出端的意思。保证每一个时钟周期只有一个组件到总线是enable状态,不然就乱了。

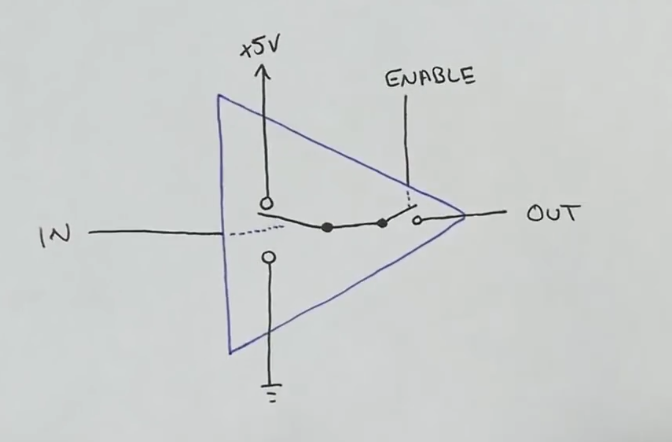

使输出端有上述效果,即可以表示0,1,断开。需要一个下图所示的装置:

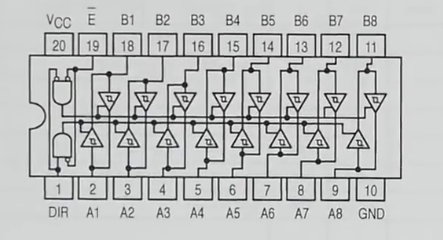

对应的74LS系列为74LS245,是一个8位的三态双向总线收发器,其针脚图如下:

- DIR=“0”,信号由B向A传输;(接收);DIR=“1”,信号由A向B传输;(发送)

- 当E为高电平时,A、B均为高阻态,就是不通的。

将寄存器与该数字电路相连,输出端接到总线(bus)上即完成了该需求。下图中右侧两个数字电路为两个4位的寄存器(之后再说用什么电路),左一为74LS245,哪些接出来的蓝线即为输出端,准备接到总线上。

参考视频:eater.net

公众号 - 低并发编程

浙公网安备 33010602011771号

浙公网安备 33010602011771号