编译预处理命令--define和ifdef的使用

这里将对常用的预处理命令进行学习。

一、宏定义 ·defined

格式:`defined 宏名 数值

或者 `define 宏名

注意:后面没有‘;‘,和单片机不一样;

二、文件包含处理 ·include

include 的格式在不同的编译器里是不一样的:

在quartus 中为:·include "defien.v"

在Primace中为: `include "../src/define.v"

另外,一个include只可以指定一个被包含的文件;被包含文件名可以是相对的路径也可以是绝对的路径,如:·include"scr/define.v";

多个include可以出现在同一行,可以出现空格和注释行;

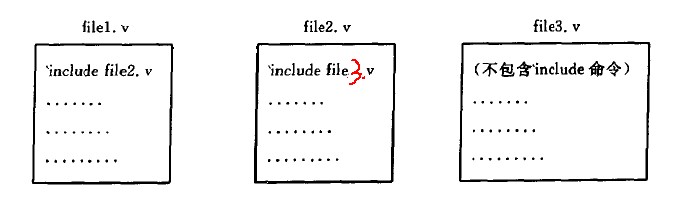

重要:如果文件1包含文件2,文件2要用文件3的部分内用,(方法一)则在文件1中可以用两个include命令分别包含文件2,和文件3,并且文件3出现在文件2之前。这样还有利用文件的包含可以嵌套的特性(方法二)。

图形表示为:

方法一:

方法二:

三、时间尺度 ·timescal

命令格式为: ·timescal 时间单位/时间精度

四、条件编译命令 ·ifdef、`elsif、`else `endif

条件编译命令指只有满足条件的时候才能编译,也就是选择性对指定的一部分的内容进行编译。

分为两种形式:

(1)’ifdef 宏名 (标识符)

程序1

·endif

(2) `ifdef 宏名 (标识符)

程序段1

·elsif 宏名 (标识符) (注意:没有e,不是elseif)

程序段2

.............

`else

程序段3

`endif

条件编译命令配合·define 使用,用·define 来定义宏名。注意:·define定义的宏名要在条件声明之前,否则默认为没有声明。

例程:通过·ifdef来改变 cnt_top的值来改变led闪烁的频率。

程序:

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :ifdef_test.v

** CreateDate :2015.05

** Funtions : 测试`ifdef 的用法

** Operate on :M5C06N3L114C7

** Copyright :All rights reserved.

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data :

** Modify Content:

*******************************************************************************/

`include "../src/define.v"

module ifdef_test(

clk,

rst_n,

led

);

input clk;

input rst_n;

output led;

reg led ;

//---------------------------------------------//

// `define div_6

reg [7:0] cnt;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= 0;

end

else if(cnt >= `cnt_top)

begin

cnt <= 0;

end

else cnt <= cnt + 1;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

led <= 0;

end

else if(cnt == `cnt_top)

begin

led = ~led ;

end

end

wire [7:0] a;

assign a = `cnt_top; //寄存`cnt_top的值更直接

endmodule

用define.v来设置·ifdef

/********************************Copyright**************************************

**----------------------------File information--------------------------

** File name :define.v

** CreateDate :2015.

** Funtions : ifdef 的声明文件

** Operate on :M5C06N3L114C7

** Copyright :All rights reserved.

** Version :V1.0

**---------------------------Modify the file information----------------

** Modified by :

** Modified data :

** Modify Content:

*******************************************************************************/

`define div_3 //要放在ifdef 的前面,佛则变异的时候判断为没有声明

`ifdef div_6

`define cnt_top 2

`elsif div_3 //elsif 没有'e '

`define cnt_top 4

`else

`define cnt_top 1

`endif

仿真程序:

module testbench; reg clk; reg rst_n; wire led; ifdef_test ifdef_test( .clk, .rst_n, .led ); parameter tck = 24; parameter t = 1000/tck; always #(t/2) clk = ~clk; initial begin clk = 0; rst_n = 0; #(15*t) rst_n = 1; end

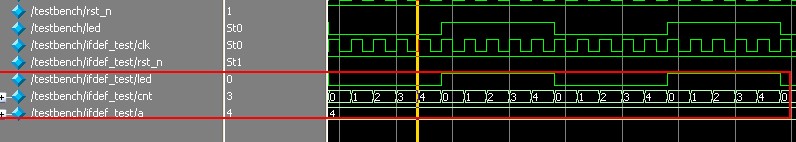

仿真图:

复合预期效果。

浙公网安备 33010602011771号

浙公网安备 33010602011771号