FPGA实现神经网络加速

FPGA实现神经网络加速

1整体思路

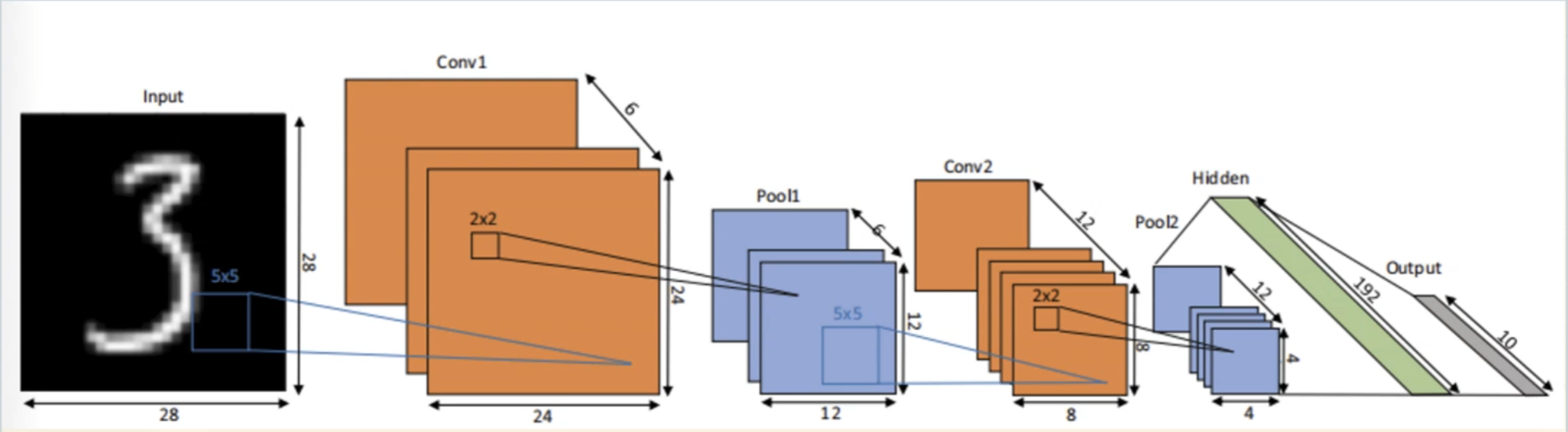

采用LeNet-5作为手写数字识别的神经网络,原因:LeNet网络结构比较简单。

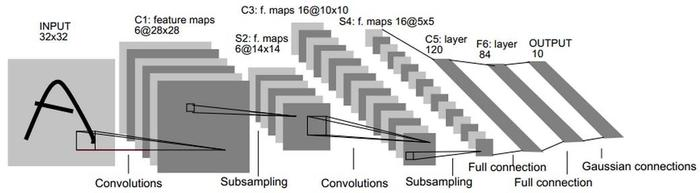

1.1 LeNet结构

enter description here

enter description here

LeNet共分为7层,分别是:

C1,卷积层

S2,池化层

C3,卷积层

S4,池化层

C5,卷积层

F6,全连接层

OUTPUT,全连接层

输入图片为尺寸32 × 32,也可以输入灰度处理后的数值即可。

卷积核大小为 5× 5

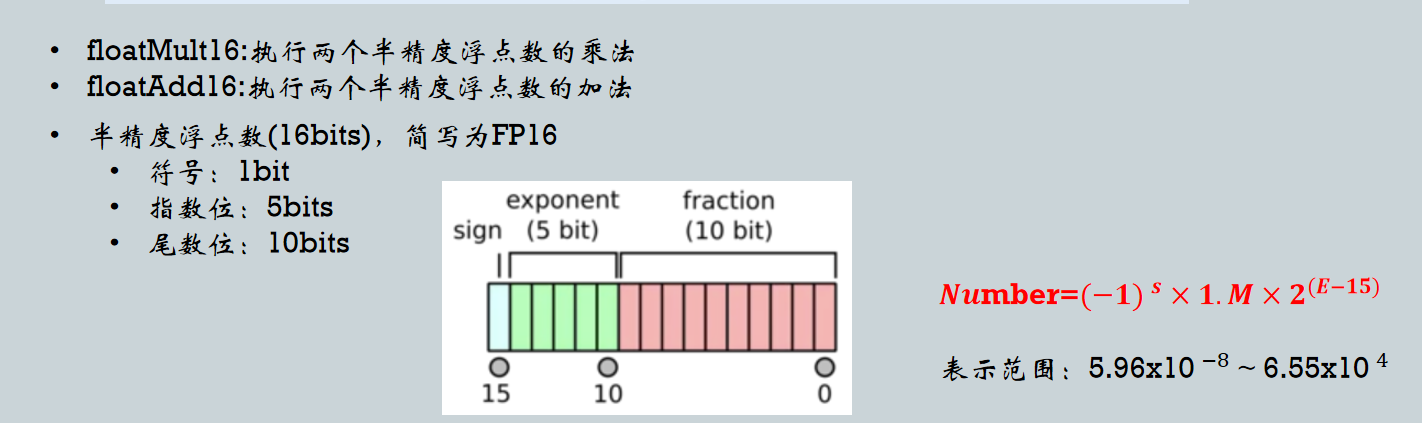

所有数据为float16类型,

2 卷积层

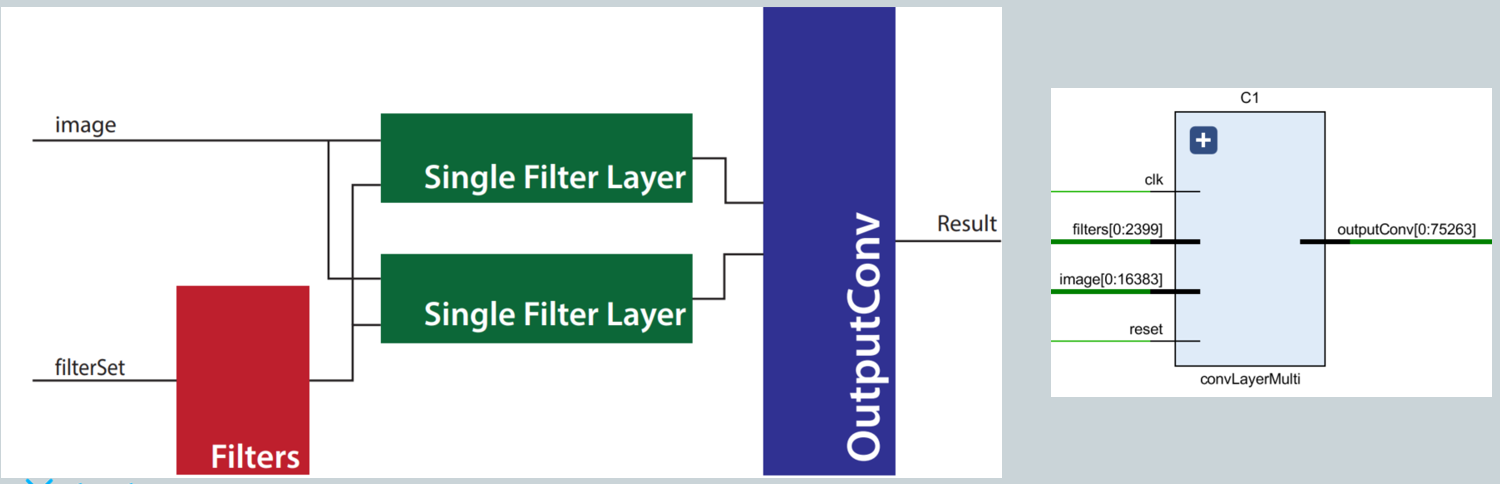

(1)Multi Filter Layer

一个卷积层,有多个Filter,也可以称为卷积核,image与不同的Filter卷积,得到包含不同特征的feature map。

enter description here

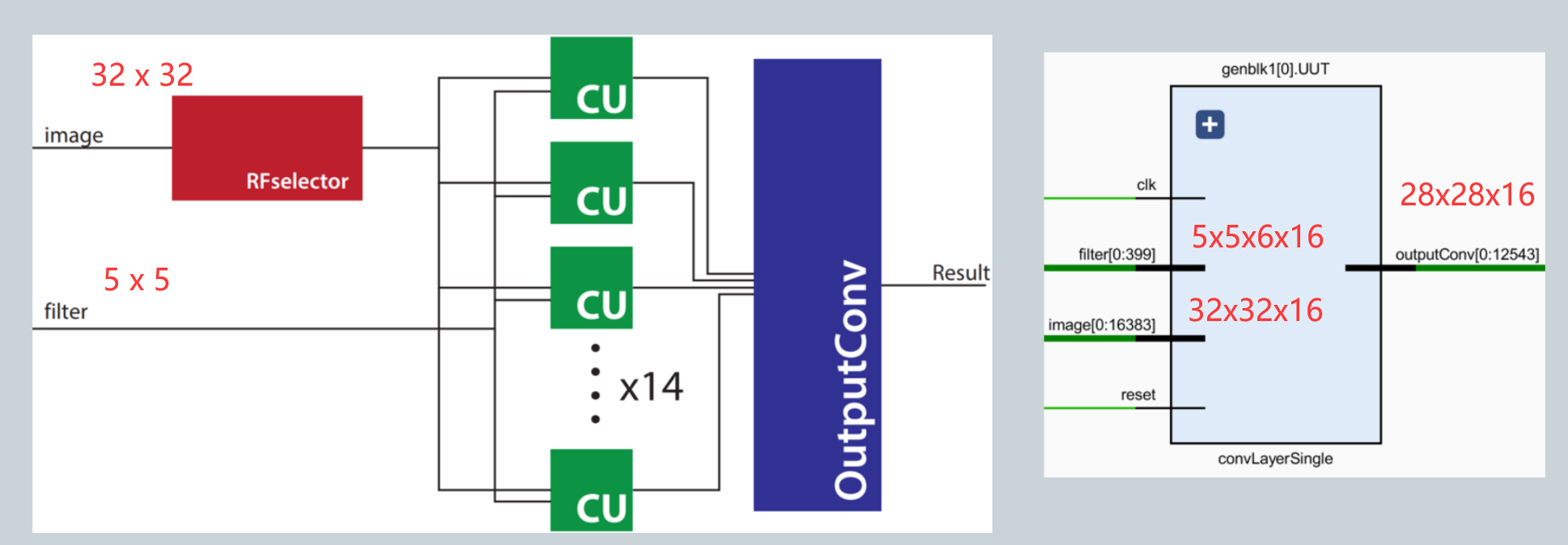

(2)Single Filter Layer

单个Filter,输入image,输出feature map。

(1)Multi Filter Layerenter description here

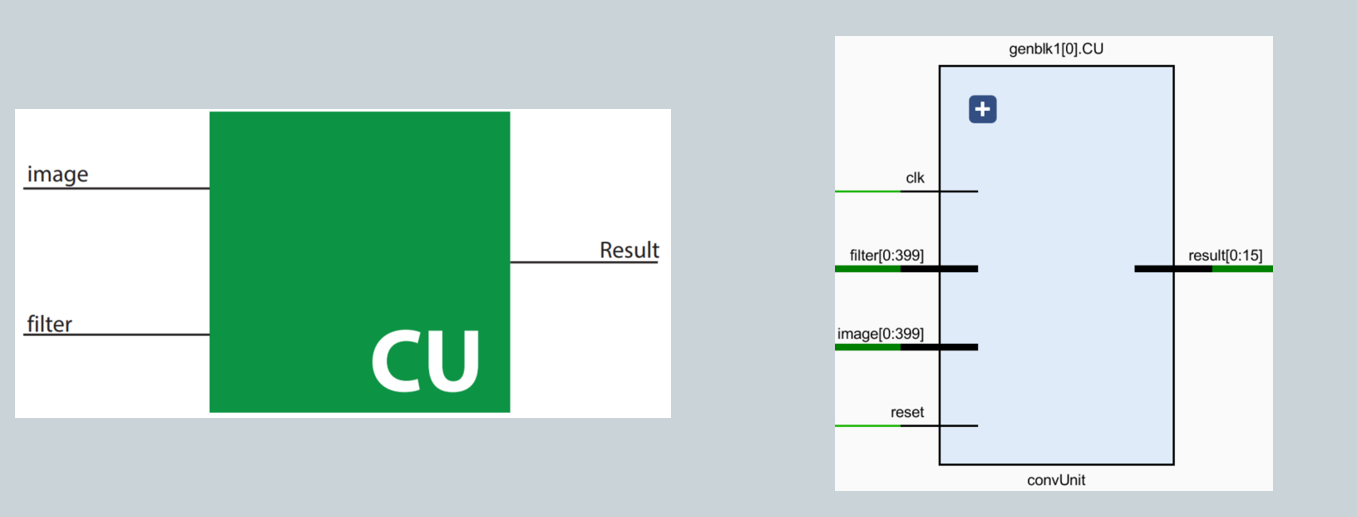

(3)Convolution Unit

每个卷积核与输入图像进行卷积,得到特征图

enter description here

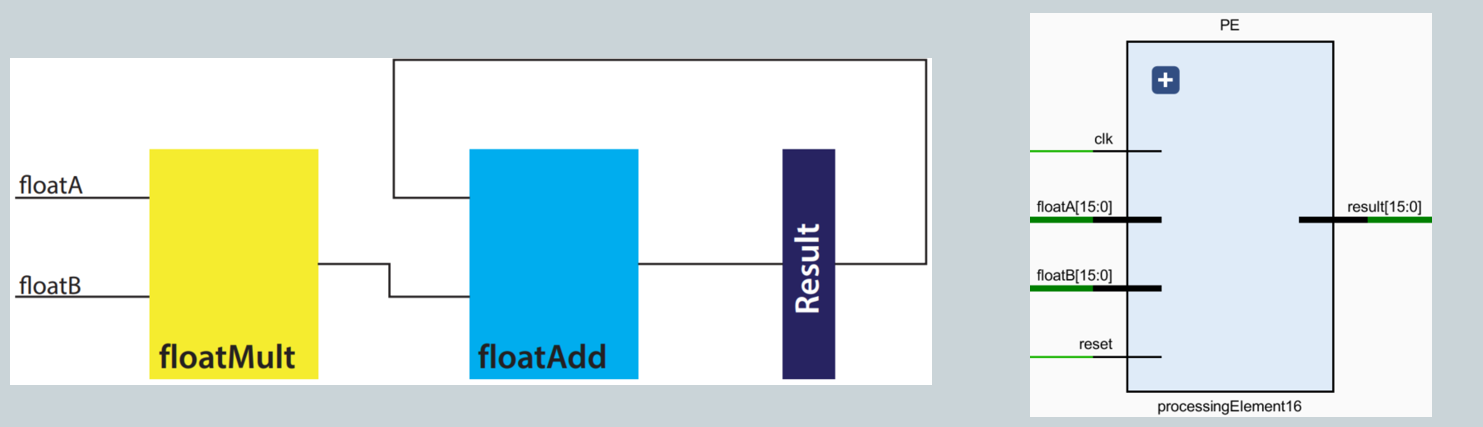

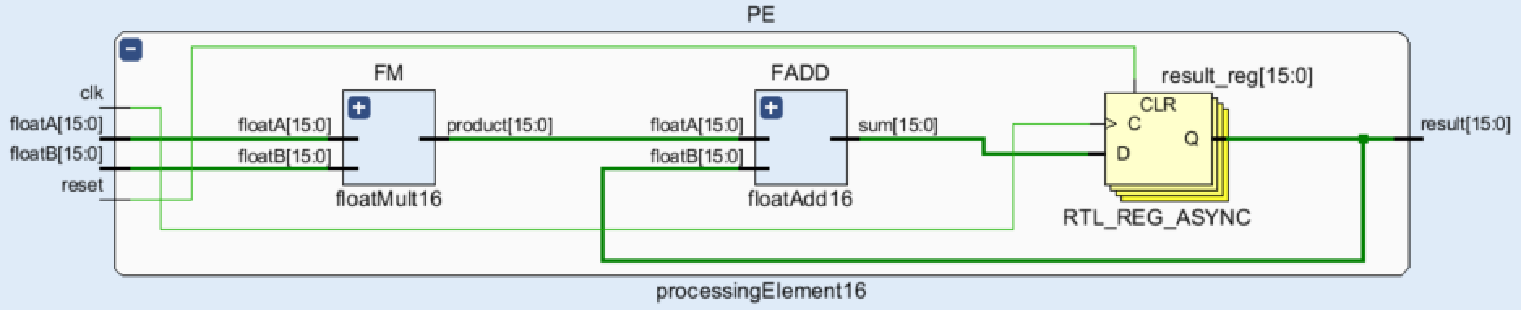

(4)Processing Element

卷积所进行的具体操作就是点乘,本质是乘法和加法。这里输入是float类型,硬件实现也就是定点数。

enter description here

硬件设计图

enter description here

enter description here

浙公网安备 33010602011771号

浙公网安备 33010602011771号