电类综合实验操作记录:Quartus进行多功能数字钟的设计

课程设计可参考:http://www.doc88.com/p-8931275491532.html

1.计时电路

秒位,分位

秒位,分位

1.1 接时钟:控制数值显示的频率

1.2 个位满10进位,个位清零:

①Nand2接LDN

Nand2 用于个位满10进1,接入芯片的LDN,LDN作用:LDN为1时,芯片不输出QD,QC,QB,QA二进制转化成的十进制,而换成输出DCBA二进制转化成的十进制数字,可用于秒位满10置0,和分位满6置0

②GND:始终输出低电平0

①Nand2接LDN

Nand2 用于个位满10进1,接入芯片的LDN,LDN作用:LDN为1时,芯片不输出QD,QC,QB,QA二进制转化成的十进制,而换成输出DCBA二进制转化成的十进制数字,可用于秒位满10置0,和分位满6置0

②GND:始终输出低电平0

1.3 个位满10进位,分位加1

个位使能端的作用:控制计数器开始计数,连接外部电路箱开关

分位使能端的作用:如果使能端变为1,则表示时钟来了计数芯片开始计数。可以用非门连接到个位的…与非门(条件判断),个位每次满足使en1为1的条件,则时钟信号来了就加1

个位使能端的作用:控制计数器开始计数,连接外部电路箱开关

分位使能端的作用:如果使能端变为1,则表示时钟来了计数芯片开始计数。可以用非门连接到个位的…与非门(条件判断),个位每次满足使en1为1的条件,则时钟信号来了就加1

1.4 个位满10,分位满6,分位清零

①Nand3接LDN

Nand3 用于个位满10,分位满6,时位进1,接入芯片的LDN,

LDN作用:LDN为1时,芯片不输出QD,QC,QB,QA二进制转化成的十进制,而换成输出DCBA二进制转化成的十进制数字,可用于秒位满10置0,和分位满6置0

①Nand3接LDN

Nand3 用于个位满10,分位满6,时位进1,接入芯片的LDN,

LDN作用:LDN为1时,芯片不输出QD,QC,QB,QA二进制转化成的十进制,而换成输出DCBA二进制转化成的十进制数字,可用于秒位满10置0,和分位满6置0

②GND:始终输出低电平0

1.5 个位满10,分位满6,时位进1

分位使能端的作用:如果使能端变为1,则表示时钟来了计数芯片开始计数。可以用非门连接到个位的…与非门(条件判断),个位每次满足使en1为1的条件,则时钟信号来了就加1

1.6.输出模块:

三个输出:总线形式:ql[3..0], qh[3..0],qhh[3..0]

三个输出:总线形式:ql[3..0], qh[3..0],qhh[3..0]

2.编译:黑色三角形

3.simulator 检查运行结果【目的:为了在直接连到外部电路前,先在电脑上进行仿真,检查clock, clear, en信号对芯片的控制是不是成功(成功即达到你想要的效果)】

3.1 实际操作:

①创建一个仿真文件:new-verification-waveform文件 => 右键 insert => finder => all => list => '=>' =>

②修改仿真时间:默认仿真时间是1us(从头到尾的仿真时间), 可以在edit-end Time中修改为 3us

③逐一检查clock, cr, en信号的输出效果和 控制效果!

i)设置时钟信号:选中clk行,在左侧菜单栏中找到overwrite clock

3.1 实际操作:

①创建一个仿真文件:new-verification-waveform文件 => 右键 insert => finder => all => list => '=>' =>

②修改仿真时间:默认仿真时间是1us(从头到尾的仿真时间), 可以在edit-end Time中修改为 3us

③逐一检查clock, cr, en信号的输出效果和 控制效果!

i)设置时钟信号:选中clk行,在左侧菜单栏中找到overwrite clock

点击左侧菜单栏,放大,箭头,选中要清零的区域,设置为0

Iii) 设置使能信号:使能信号为0是保持,为1是遇到时钟计数(因为84161遇到clock的功能就是计数)

所以可以通过将en置0,看输出是否保持不变,如果保持不变,则电路控制正确。

所以可以通过将en置0,看输出是否保持不变,如果保持不变,则电路控制正确。

Iv) 剩下的为输出端,不用编辑,只需要运行程序,用来检查所设计的电路是否实现想要的功能

v)保存文件

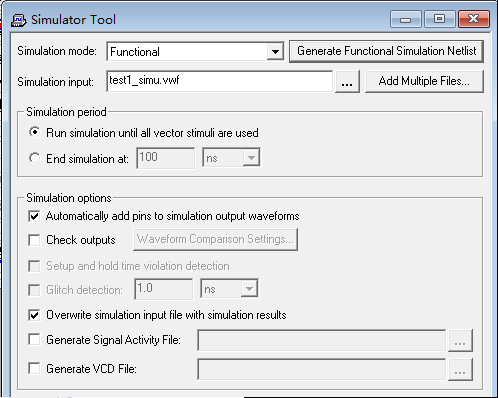

④进行仿真

Processing-simulator

【可以尝试以下两种仿真形式,查看效果

Timing形式:实时仿真

functional形式:只从数学理论角度进行仿真】

先尝试functional,

点击省略号,选中刚刚创建的waveform文件

记住选中overwrite simulation input file… results;

然后点击第一行:generate functional simulation netlist

Processing-simulator

【可以尝试以下两种仿真形式,查看效果

Timing形式:实时仿真

functional形式:只从数学理论角度进行仿真】

先尝试functional,

点击省略号,选中刚刚创建的waveform文件

记住选中overwrite simulation input file… results;

然后点击第一行:generate functional simulation netlist

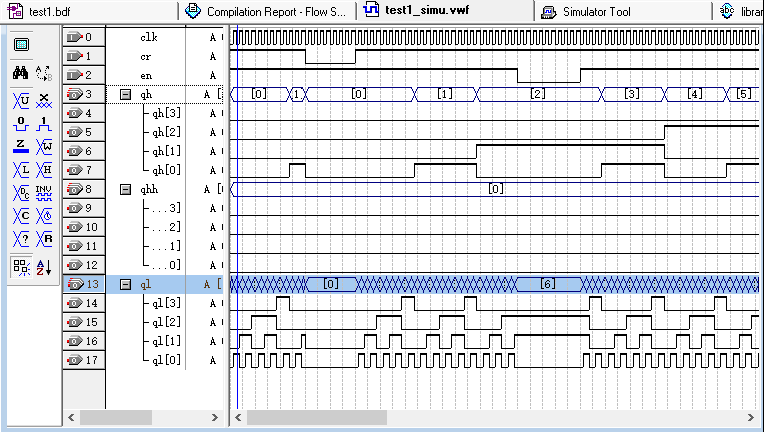

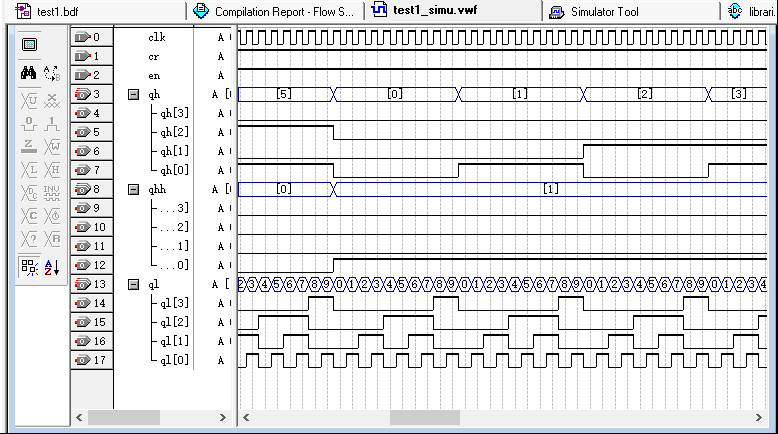

然后往下拉,点击start,运行后点击open

显示以下结果:

对结果进行分析:

1)ql[0]和ql[3]同时达到1,之后ql[3..0]全部清零,qh[0]变为高电平1,实现秒位满10清零和分位进1功能

2)之后cr信号起作用,qh,qhh,ql在cr=0期间全部为0

3)cr信号结束,秒位从0开始重新计数,满10进1,qh为分位,进到[2]时,遇到en置0,实现保持功能,所以en置0期间,ql,qhh,qhh均保持为当前数字。ql位显示为6表示此时ql[3..0]的二进制转化为十进制后为6。保持信号结束,en重新为1,在当前信号的基础上,继续计数。

4)分位由5变0表示分位满6清零,同时十位+1,表示分位满6进1,说明实现了想要的功能。

5)观察发现

如果是functional仿真的话:各个信号和时钟信号之间的关系,每个信号如果有累加,则+1发生在时钟脉冲的上升边沿。

如果是Timing实时仿真的话:则+不会发生在时钟脉冲的上升边沿,并且波形不干净,从9到0之间的信号会夹杂一些杂质信号,这是由于由0111转变为1000时,四个二进制数字不能够同时转变,转变肯定会有先后,所以会夹杂其他比如6,4,2等等的数值

=>所以在电路设计中会有采用循环码而不是二进制码的原因。

如果是functional仿真的话:各个信号和时钟信号之间的关系,每个信号如果有累加,则+1发生在时钟脉冲的上升边沿。

如果是Timing实时仿真的话:则+不会发生在时钟脉冲的上升边沿,并且波形不干净,从9到0之间的信号会夹杂一些杂质信号,这是由于由0111转变为1000时,四个二进制数字不能够同时转变,转变肯定会有先后,所以会夹杂其他比如6,4,2等等的数值

=>所以在电路设计中会有采用循环码而不是二进制码的原因。

⑤回到原理图,对所设计的电路进行封装,封装成小模块。

File- create&update - (第二个)create symbol files , 保存为test1.bsf文件(名字可以随便取)

File- create&update - (第二个)create symbol files , 保存为test1.bsf文件(名字可以随便取)

⑥如何找到已封装的模块:

关闭所有文件;

File-new-创建原理图文件- 双击csf文件空白处-出现libraries-project-test1, 得到所封装的模块;用所封装的模块时,注意需要重新接外部输入输出端口,

关闭所有文件;

File-new-创建原理图文件- 双击csf文件空白处-出现libraries-project-test1, 得到所封装的模块;用所封装的模块时,注意需要重新接外部输入输出端口,

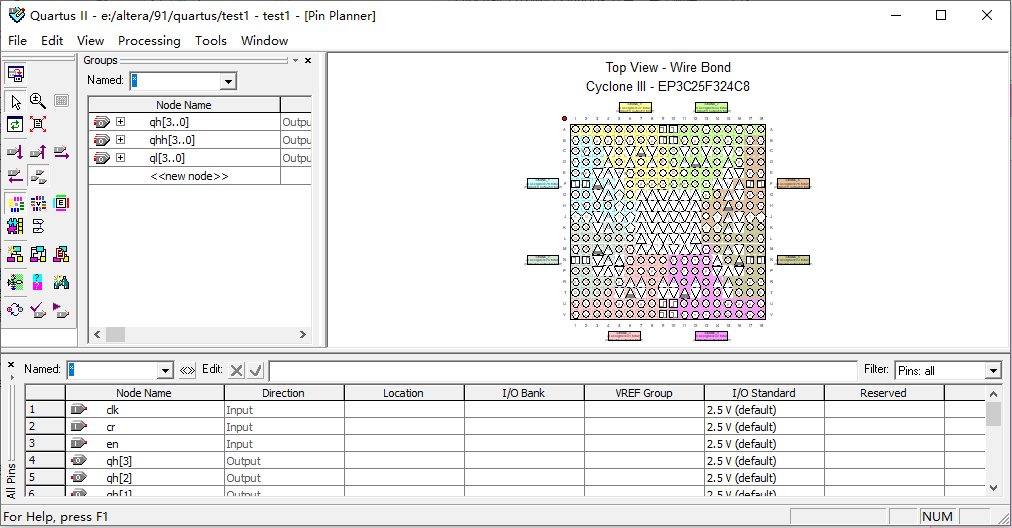

2.分配引脚

菜单栏Assignment-pin,双击location一列对应空格,出现下拉的黑色三角形,对应分配引脚的文件进行分配即可(location是选择FPGA管脚的编号 )

菜单栏Assignment-pin,双击location一列对应空格,出现下拉的黑色三角形,对应分配引脚的文件进行分配即可(location是选择FPGA管脚的编号 )

之后通过操纵外部实验板的开关,信号就可以通过对应的FPGA的管脚输入到内部的程序中,实现程序的功能。【开关往上为0,往下为1】

浙公网安备 33010602011771号

浙公网安备 33010602011771号