主存储器与CPU的链接

1.连接原理

1.主存储器通过数据总线,地址总线,控制主线与CPU连接。

2.数据总线的位数与工作频率的乘积正比于数据传输率

3.地址总线的位数决定了可寻址的最大内存空间。

4.控制总线(读/写)指出总线的周期的类型和本次输入/输出操作完成的时刻。

2.主存容量的扩展:

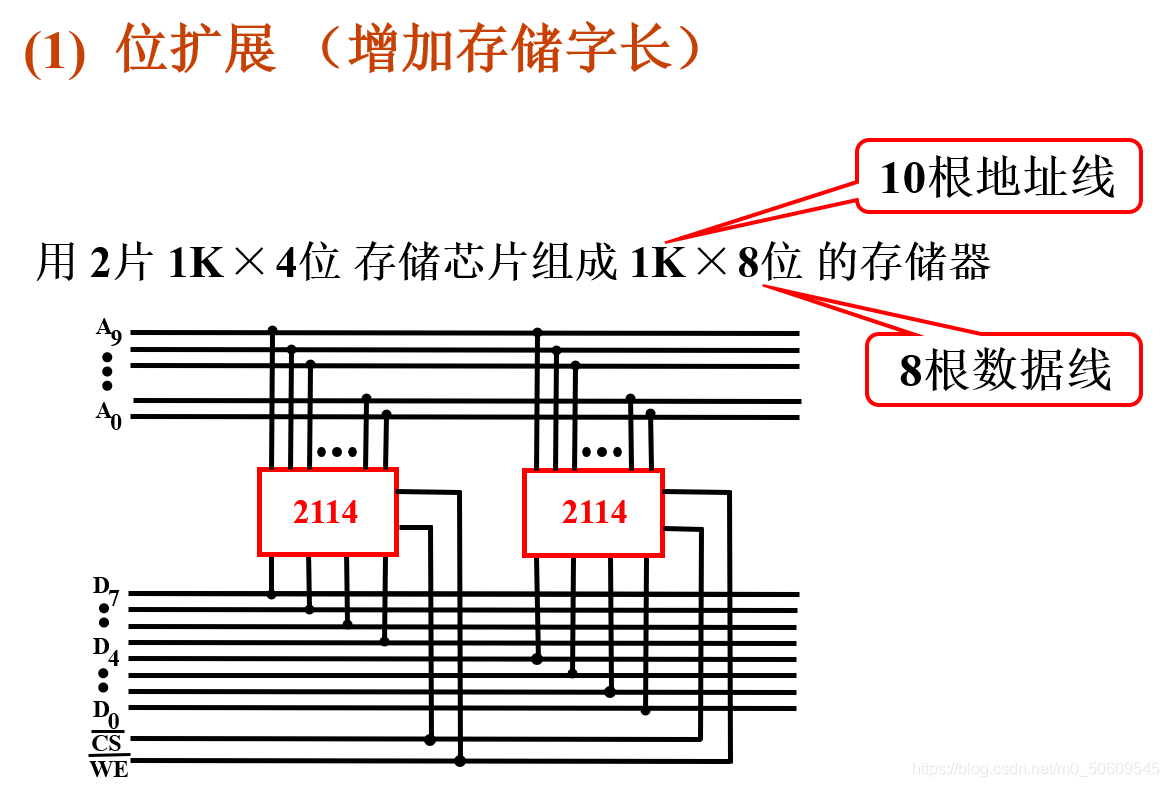

1位扩展法:

cpu的数据线与存储芯片的数据位数不一定相等,这时必须对存储芯片进行扩位,使其数据位数与cpu的数据线数相等。

位扩展的连接方式:将多个存储芯片的地址端,片选端和读写控制端相应并联,数据端分别引出

进行位扩展时,各芯片连接地址线的方式相同,但是连接数据线的方式不同,在某一时刻选中所有芯片,所以片选信号要连接到所有芯片

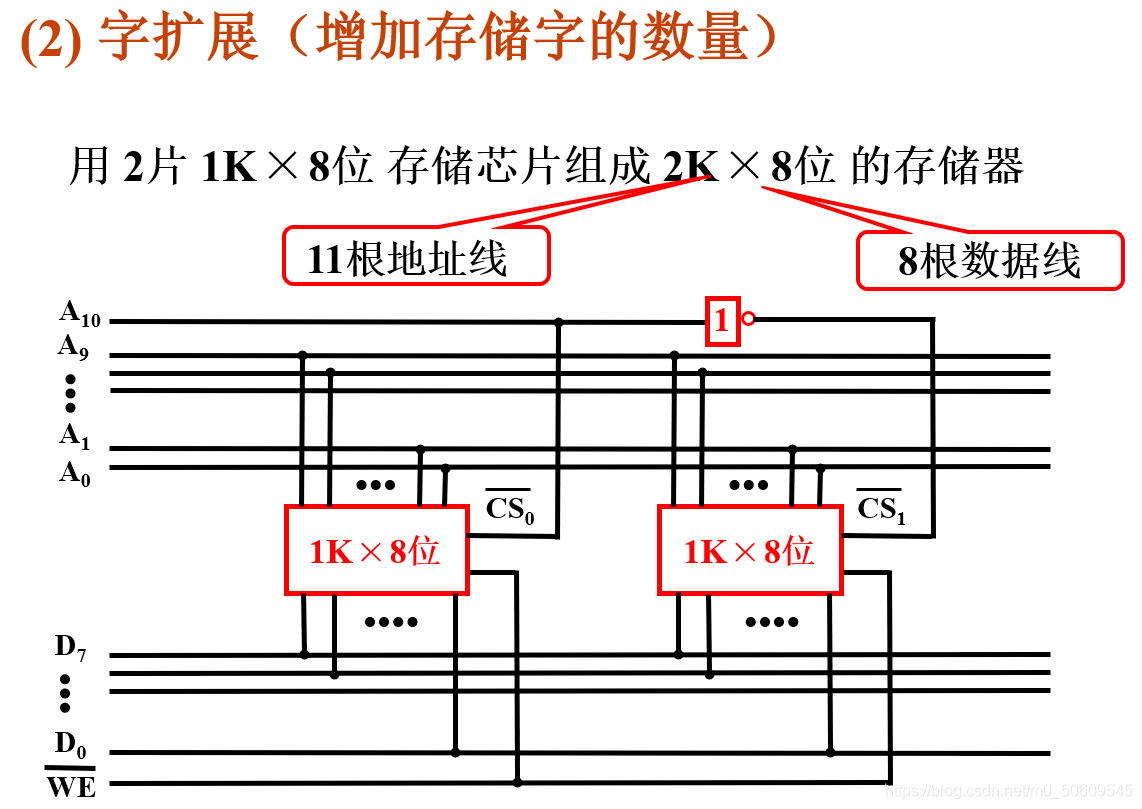

2.字扩展法:

字扩展是指增加存储器中字的数量,而位数不变,字扩展将芯片的地址线,数据线,读写控制线相并联,片选信号来区别各芯片的地址范围

仅采用字扩展时,各芯片连接地址线的方式相同,连接数据线的方式也相同,某一时刻只需要选中部分芯片,所以通过片选信号或采用译码器设计连接到相应的芯片

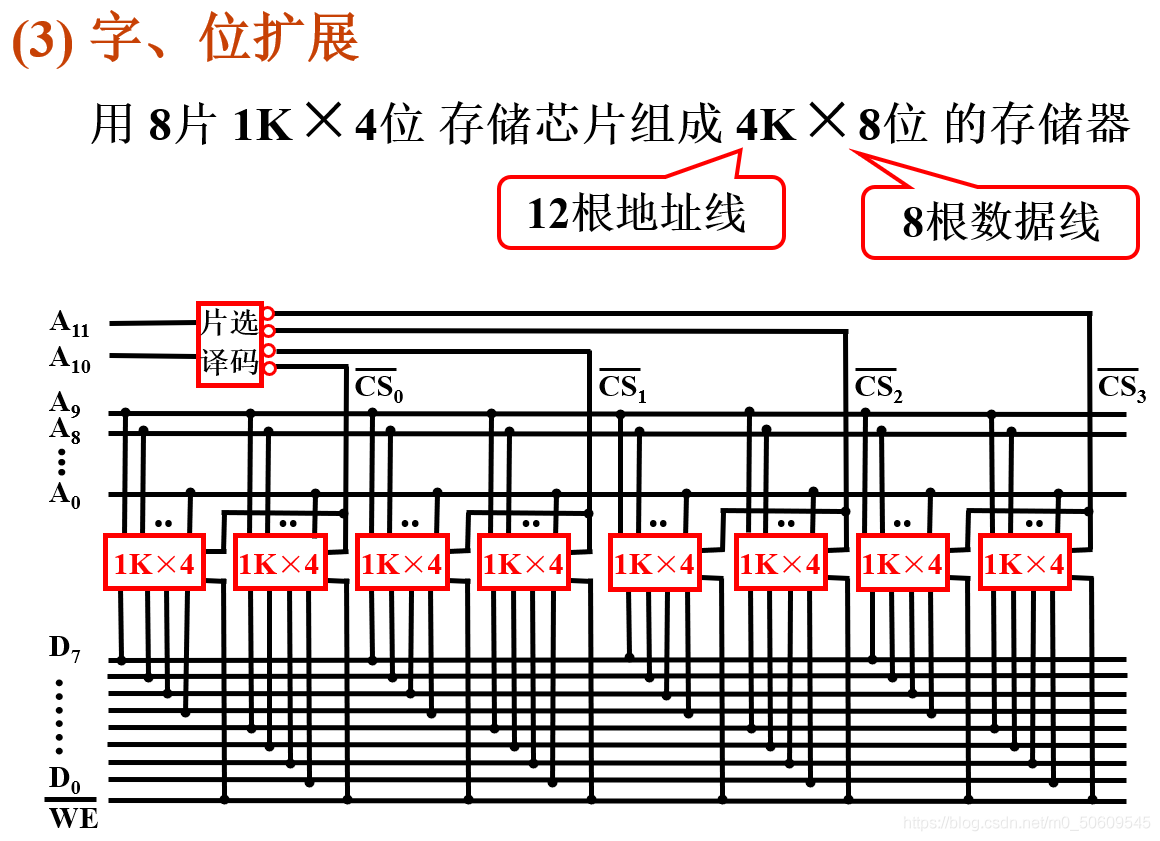

3.字位同时扩展

字位同时扩展指既增加存储字的数量,又增加存储字长。

采用字位同时扩展时,各芯片连接地址线的方式相同,但是连接数据线的方式不同,而且需要通过片选信号或译码器设计连接到相应的芯片

参考博客:https://blog.csdn.net/m0_50609545/article/details/118310334

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· Docker 太简单,K8s 太复杂?w7panel 让容器管理更轻松!

2021-04-15 大二下学期团队项目(讨论)