--File : pc_cpu.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.STD_LOGIC_ARITH.all;

entity gc_cpu is

port(

SCLK: in std_logic; --50M--

QCLK: in std_logic; --133M--

ext_reset : in STD_LOGIC; --not (HRESET and SRESET) active high

CPU_GE_CS : in STD_LOGIC;

CPU_PORTX_A : in STD_LOGIC_VECTOR(21 downto 0);

CPU_PORTX_OE : in STD_LOGIC;

CPU_PORTX_WE : in STD_LOGIC;

CPU_PORTX_D : inout STD_LOGIC_VECTOR(7 downto 0);

CPU_PORTX_INT13 : out STD_LOGIC

);

end gc_cpu;

architecture gc_cpu of gc_cpu is

type array_8bit is array (21 downto 0) of std_logic_vector(7 downto 0);

signal ram : array_8bit;

signal cs : std_logic;

signal oe : std_logic;

signal we : std_logic;

signal addr_in: std_logic_vector(21 downto 0);

signal data_in, data_out: std_logic_vector(7 downto 0);

begin

cs <= CPU_GE_CS;

oe <= CPU_PORTX_OE;

we <= CPU_PORTX_WE;

addr_in <= CPU_PORTX_A;

--write

process(QCLK)

begin

if QCLK'event and QCLK = '1' then

if we = '0' and cs = '0' then

ram(conv_integer(addr_in)) <= data_in;

end if;

end if;

end process;

--read

process(QCLK, ext_reset)

begin

if ext_reset = '1' then

data_out <= (others => '0');

elsif QCLK'event and QCLK = '1' then

if we = '1' and oe = '0' and cs = '0' then

data_out <= ram(conv_integer(addr_in));

end if;

end if;

end process;

data_in <= CPU_PORTX_D;

CPU_PORTX_D <= data_out when oe = '0' and cs = '0' else

(others => 'Z');

end gc_cpu;

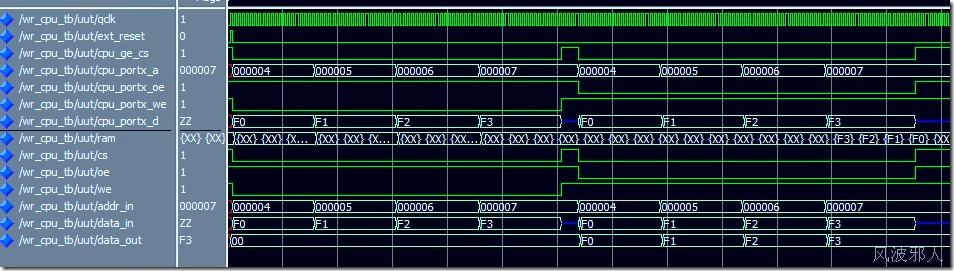

对应modelsim仿真的VHDL程序

--File : cpu_port_tb.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.STD_LOGIC_ARITH.all;

entity wr_cpu_tb is

end wr_cpu_tb;

architecture rtl of wr_cpu_tb is

component gc_cpu

port(

SCLK: in std_logic; --50M--

QCLK: in std_logic; --133M--

ext_reset : in STD_LOGIC; --not (HRESET and SRESET) active high

CPU_GE_CS : in STD_LOGIC;

CPU_PORTX_A : in STD_LOGIC_VECTOR(21 downto 0);

CPU_PORTX_OE : in STD_LOGIC;

CPU_PORTX_WE : in STD_LOGIC;

CPU_PORTX_D : inout STD_LOGIC_VECTOR(7 downto 0);

CPU_PORTX_INT13 : out STD_LOGIC

);

end component;

signal SCLK: std_logic;

signal QCLK: std_logic:= '1';

signal ext_reset : STD_LOGIC;

signal CPU_GE_CS : STD_LOGIC:= '1';

signal CPU_PORTX_A : STD_LOGIC_VECTOR(21 downto 0);

signal CPU_PORTX_OE : STD_LOGIC:= '1';

signal CPU_PORTX_WE : STD_LOGIC:= '1';

signal CPU_PORTX_D: STD_LOGIC_VECTOR(7 downto 0);

signal CPU_PORTX_INT13 : STD_LOGIC;

constant CLK_period : time := 7.5 ns;

begin

uut: gc_cpu port map

(

SCLK => SCLK,

QCLK => QCLK,

ext_reset => ext_reset,

CPU_GE_CS => CPU_GE_CS,

CPU_PORTX_A => CPU_PORTX_A,

CPU_PORTX_OE => CPU_PORTX_OE,

CPU_PORTX_WE => CPU_PORTX_WE,

CPU_PORTX_D => CPU_PORTX_D,

CPU_PORTX_INT13 => CPU_PORTX_INT13

);

CLK_process : process

begin

QCLK <= not QCLK;

wait for CLK_period/2;

end process;

body_process: process

begin

ext_reset <= '0';

wait for CLK_period/2;

ext_reset <= '1';

wait for CLK_period/2;

ext_reset <= '0';

-----write

CPU_GE_CS <= '0';

CPU_PORTX_OE <= '1';

CPU_PORTX_WE <= '0';

CPU_PORTX_A <= b"0000000000000000000100";

CPU_PORTX_D <= X"F0";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

-- wait for 2*CLK_period;

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '0';

CPU_PORTX_A <= b"0000000000000000000101";

CPU_PORTX_D <= X"F1";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

--

-- wait for 2*CLK_period;

--

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '0';

CPU_PORTX_A <= b"0000000000000000000110";

CPU_PORTX_D <= X"F2";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

--

-- wait for 2*CLK_period;

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '0';

CPU_PORTX_A <= b"0000000000000000000111";

CPU_PORTX_D <= X"F3";

wait for 20*CLK_period;

CPU_GE_CS <= '1';

CPU_PORTX_OE <= '1';

CPU_PORTX_WE <= '1';

CPU_PORTX_D <= "ZZZZZZZZ";

-----read

wait for 4*CLK_period;

CPU_GE_CS <= '0';

CPU_PORTX_OE <= '0';

CPU_PORTX_WE <= '1';

CPU_PORTX_A <= b"0000000000000000000100";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

-- wait for 3*CLK_period;

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '0';

-- CPU_PORTX_WE <= '1';

CPU_PORTX_A <= b"0000000000000000000101";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

-- wait for 3*CLK_period;

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '0';

-- CPU_PORTX_WE <= '1';

CPU_PORTX_A <= b"0000000000000000000110";

wait for 20*CLK_period;

-- CPU_GE_CS <= '1';

-- CPU_PORTX_OE <= '1';

-- CPU_PORTX_WE <= '1';

-- wait for 3*CLK_period;

-- CPU_GE_CS <= '0';

-- CPU_PORTX_OE <= '0';

-- CPU_PORTX_WE <= '1';

CPU_PORTX_A <= b"0000000000000000000111";

wait for 22*CLK_period;

CPU_GE_CS <= '1';

CPU_PORTX_OE <= '1';

CPU_PORTX_WE <= '1';

wait;

end process;

end;