--等占空比5分频电路

--div_5.vhd file

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY div_5 IS

PORT(clk_in:IN std_logic;

clk_out:OUT std_logic

);

END div_5;

ARCHITECTURE rtl OF div_5 IS

SIGNAL clk_up,clk_down:std_logic;

SIGNAL count_up,count_down: INTEGER:= 0;

BEGIN

clk_out <= clk_up and clk_down;

PROCESS(clk_in)

BEGIN

IF (clk_in'event and clk_in = '1') THEN

IF(count_up < 4) THEN

count_up <= count_up + 1;

ELSE

count_up <= 0;

END IF;

END IF;

END PROCESS;

PROCESS(clk_in)

BEGIN

IF(clk_in'event and clk_in = '0') THEN

IF(count_down < 4) THEN

count_down <= count_down + 1;

ELSE

count_down <= 0;

END IF;

END IF;

END PROCESS;

PROCESS(count_up)

BEGIN

IF(count_up < 2) THEN

clk_up <= '0';

ELSE

clk_up <= '1';

END IF;

END PROCESS;

PROCESS(count_down)

BEGIN

IF(count_down < 2) THEN

clk_down <= '0';

ELSE

clk_down <= '1';

END IF;

END PROCESS;

END rtl;

--div_testbench.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div_testbench is

end div_testbench;

architecture behavior of div_testbench is

--component declaration

component div_5

port(

clk_in: in std_logic;

clk_out: out std_logic

);

end component;

--input

signal clk_in : std_logic := '0';

--output

signal clk_out : std_logic ;

constant CLK_period : time := 10 ns;

begin

uut: div_5 port map(

clk_in => clk_in,

clk_out => clk_out

);

CLK_process:process

begin

clk_in <= '0';

wait for CLK_period/2;

clk_in <= '1';

wait for CLK_period/2;

end process;

end ;

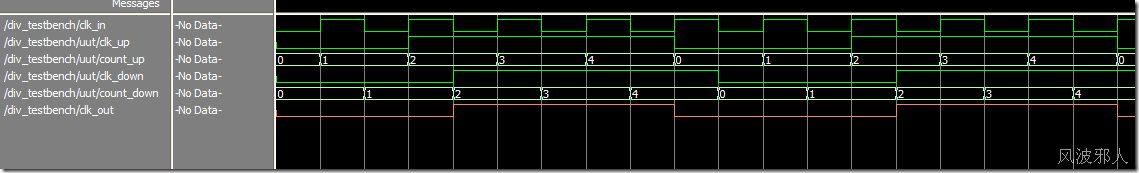

下图为modelsim仿真结果: