Xilinx 7系列FPGA中IDDR的介绍(一)

欢迎各位朋友关注“郝旭帅电子设计团队”,本公众号会定时更新相关技术类资料、软件等等,感兴趣的朋友可以浏览一下本公众号的其他“模块”,希望各位朋友都能在本公众号获得一些自己想要的“东西”。

本篇主要讨论Xilinx 7系列FPGA中IDDR的介绍(一)。

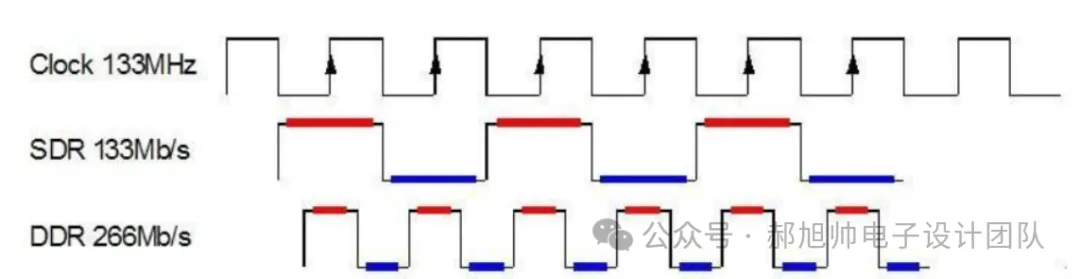

大多数数字电路内部只能处理SDR(单倍的时钟速率)的信号,但是很多的接口要求都是DDR的信号,那么FPGA是如何处理的呢?

SDR:单倍数据速率(一个周期只传输一个bit/只在一个边沿采样)。

DDR:双倍数据速率(一个周期传输两个bit/上下边沿都采样)。

本篇文章只讨论,当输入接口为DDR时,FPGA内部如何处理。

上述中提到,FPGA内部也只能处理SDR的信号,无法处理DDR信号。为了解决这个问题,FPGA厂商在FPGA的接口处放置了一块能够将DDR信号转换为SDR信号的电路功能模块:IDDR。

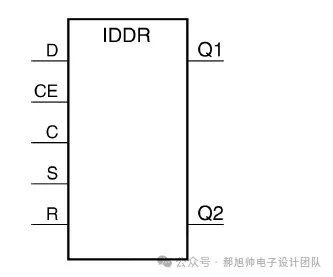

IDDR:在7系列设备的ILOGIC block中有专属的registers来实现input double-data-rate(IDDR) registers,将输入的上下边沿 DDR 信号,转换成两位单边沿 SDR 信号。

在Xilinx 7系列的FPGA开发时,如果想要使用IDDR,可以直接例化IDDR的原语即可。

// IDDR: Input Double Data Rate Input Register with Set, Reset // and Clock Enable. // 7 Series // Xilinx HDL Libraries Guide, version 14.7 IDDR #( .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE" // or "SAME_EDGE_PIPELINED" .INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1 .INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1 .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" ) IDDR_inst ( .Q1(Q1), // 1-bit output for positive edge of clock .Q2(Q2), // 1-bit output for negative edge of clock .C(C), // 1-bit clock input .CE(CE), // 1-bit clock enable input .D(D), // 1-bit DDR data input .R(R), // 1-bit reset .S(S) // 1-bit set ); // End of IDDR_inst instantiation

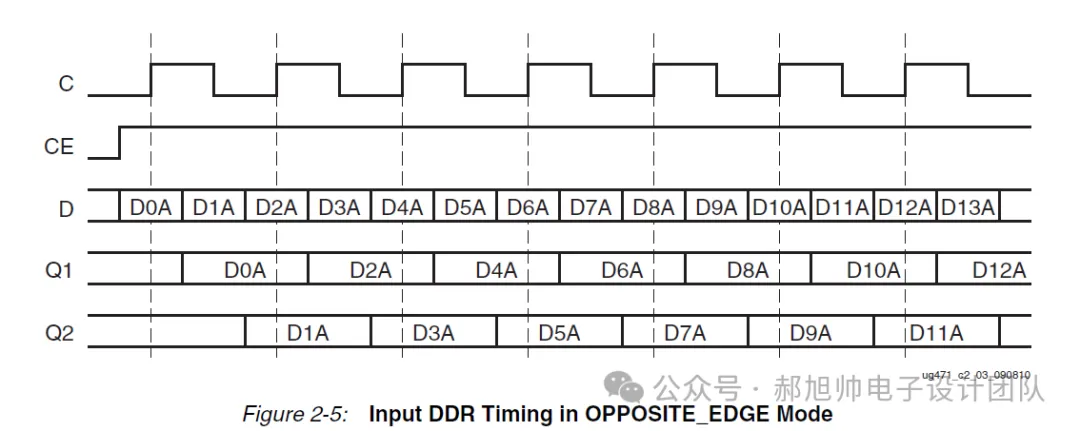

OPPOSITE_EDGE模式对应的波形如下:

上升沿采样后,立刻输出到Q1;下降沿采样后,立刻输出到Q2;

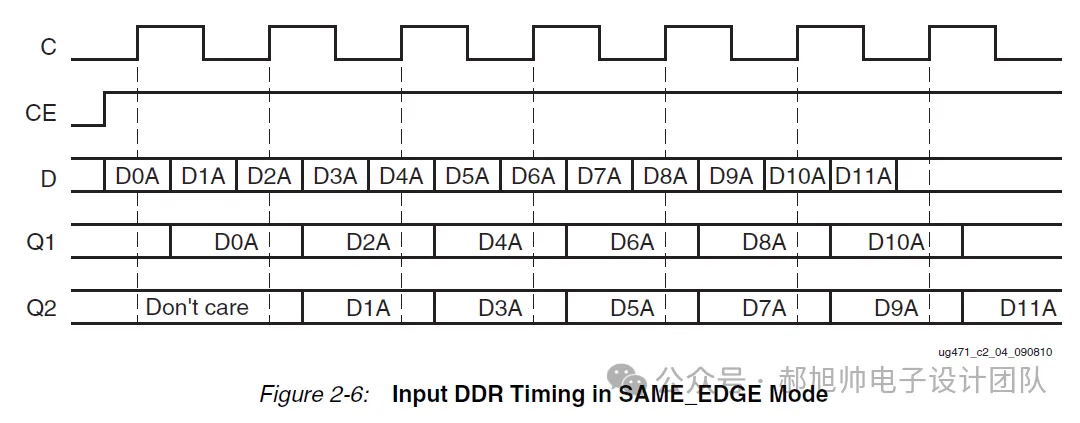

SAME_EDGE模式对应的波形如下:

上升沿采样后,立刻输出到Q1;下降沿采样后,等到下一个上升沿,输出到Q2.

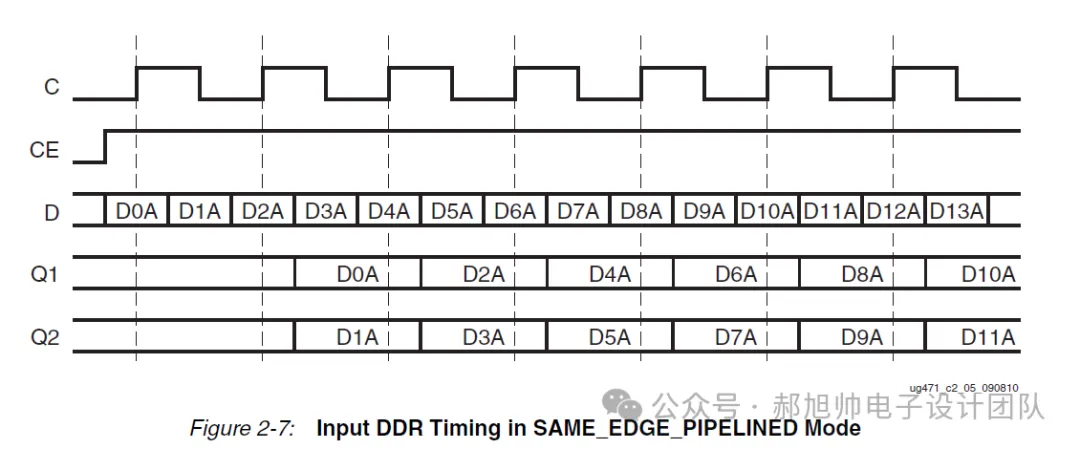

SAME_EDGE_PIPELINED模式对应的波形如下:

上升沿和下降沿采样的数据都等到下一个上升沿输出。

各位小伙伴可以按照自己的需求去配置模式。

本篇内容中有部分资源来源于网络,如有侵权,请联系作者。

如果您觉得本公众号还不错的话,可以推给身边的朋友们,感谢并祝好!