数字电路中的电平标准

欢迎各位朋友关注“郝旭帅电子设计团队”,

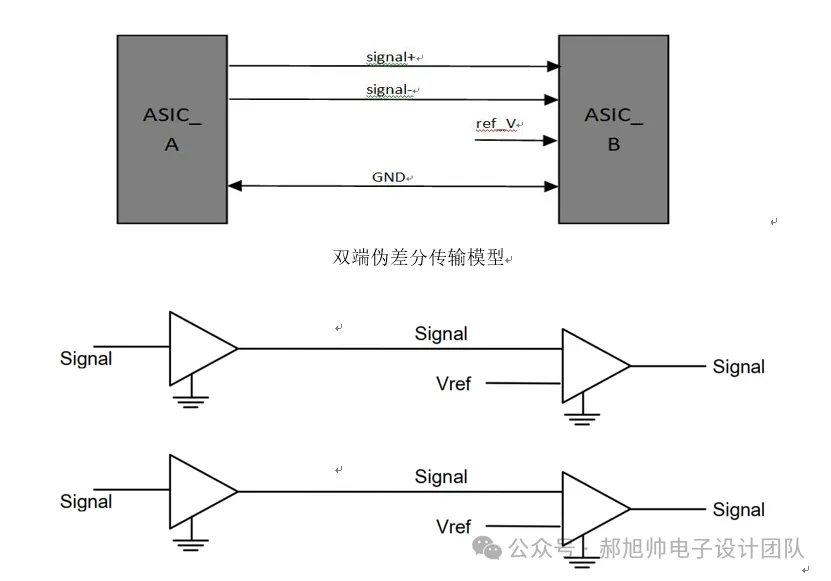

双端伪差分信号传输时,使用两条传输线分别传输信号的“正”、“反”逻辑。ASIC_A发送信号的电平与“反”电平,接收端按照单端伪差分接收标准接收,然后取出其中一路作为输出。

伪差分标准的信号输出幅度较小,电源逻辑比真差分电路简单,噪声容限大而且与JEDEC支持的SDRAM的L-Bank结构相对应,所以被应用于DDR/DDR2/DDR3接口,数据速率可以达到Gbit/s。

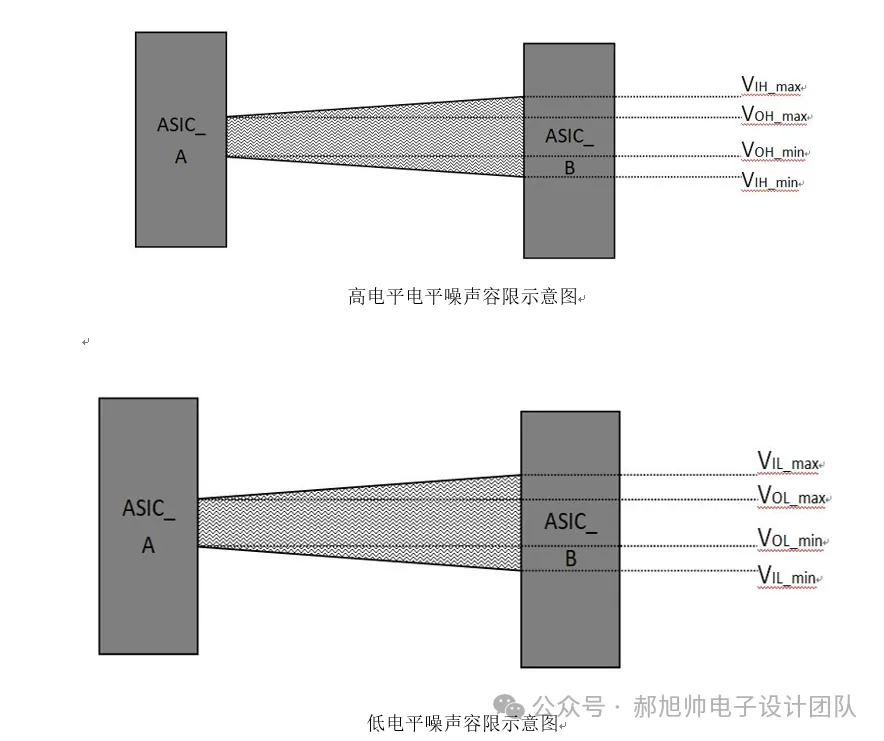

从发送端发出信号,经过线路的干扰影响,其电平可能升高或者降低,因而接收端必须在一个电平范围内判断它的逻辑值。这个电平范围称为噪声容限(Noise Margin, NM)。不同的信号传输方式和I/O标准由不同的噪声容限和逻辑值判断方式。

在单端信号传输高电平中,ASIC_A输出高电平的电压值要在VOH_max和VOH_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIH_max大于VOH_max,VIH_min小于VOH_min。而VIH_max和VOH_max都是受到电源电压的影响,并且越高肯定会判断成为逻辑高,因此VIH_min和VOH_min才是影响传输的关键。所以高电平的噪声容限(NMH)为VOH_min — VIH_min。对于低电平而言,ASIC_A输出高电平的电压值要在VOL_max和VOL_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIL_max大于VOL_max,VIL_min小于VOL_min。而VIL_min和VOL_min都是受到GND的影响,并且越低肯定会判断成为逻辑低,因此VIL_max和VOH_max才是影响传输的关键。所以低电平的噪声容限(NML)为VIL_max — VOL_max。如果发送端和接收端不能满足以上条件,那么通信就会受到影响。

本篇主要讨论数字电路中的电平标准。

信号存在的意义是为了能够进行信息的沟通,所以要求接收方必须能够正确的接收到信号,否则信号将没有任何存在的意义。

为了信息能够正确进行传输,发送和接收要有对信息认定的一直标准(发送方发送高电平,接收方要认为是高电平;发送方发送低电平,接收方要认为是低电平)。

在数字电路中,经常输入或者输出“高”、“低”电平,那么多高的电压标准算作是“高电平”呢?难道只有“0V”才算低电平?这些问题相信是任何一个初学者心中的疑虑。

我们平时所说的电压其实是电压差。例如:家用电压220V(火线)是当对于“零线”来说。

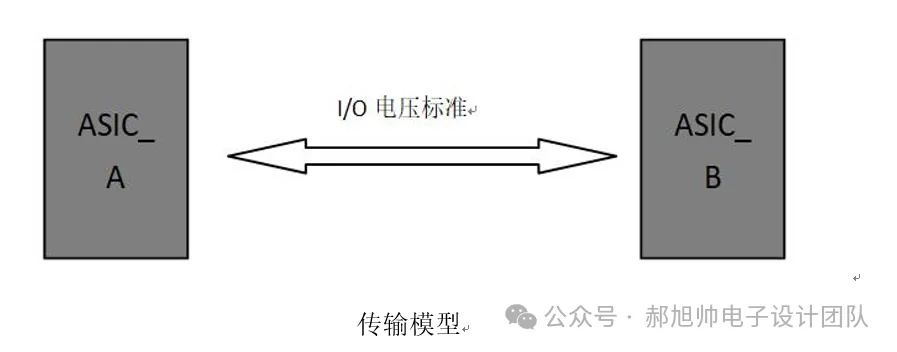

ASIC(Application Specific Integrated Circuit,专用集成电路)之间的相互通信是通过I/O发出高低电平进行通信的,这些电平都要符合相应的电平标准。

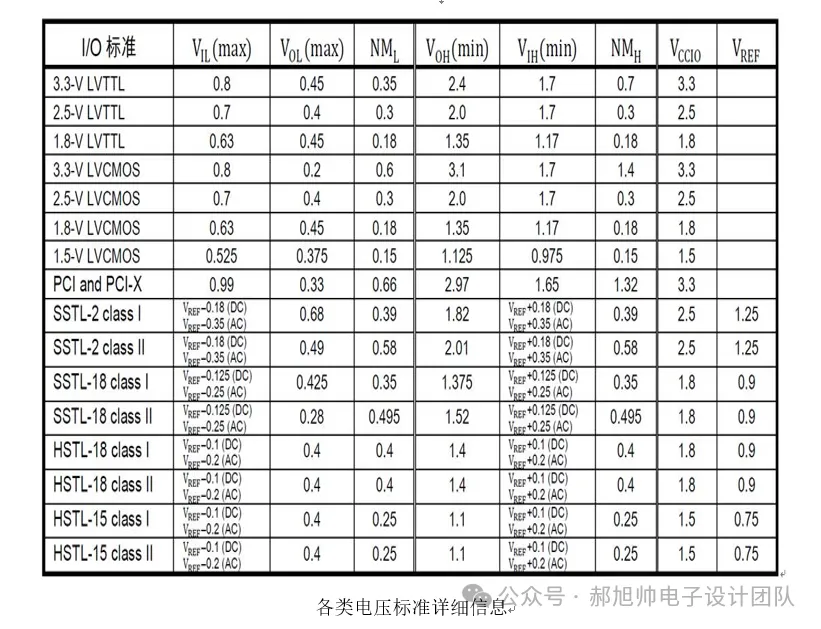

现在数字通信系统中,I/O电压标准包括早期的TTL标准,CMOS标准,LVTTL标准,LVCMOS标准,RS232,RS485标准以及HSTL(High Speed Transceiver Logic)标准和较新的LVDS(Low-Voltage Differential Signal)等标准。不同的标准支持的器件不同,支持的传输速度不同,支持的噪声容限也不同。从另一个方面来看,I/O标准的进步反映了数字系统的进步。

I/O端口标准按照信号的传输方式,分为单端信号,差分信号和伪差分信号。

单端信号传输时,在单独的导线上传输信号,其逻辑电平相对于GND(地)。ASIC_A以相对于GND的逻辑进行驱动,接收端也用相对于地的逻辑进行捕获。LVTTL标准和LVCMOS标准都是单端信号标准。

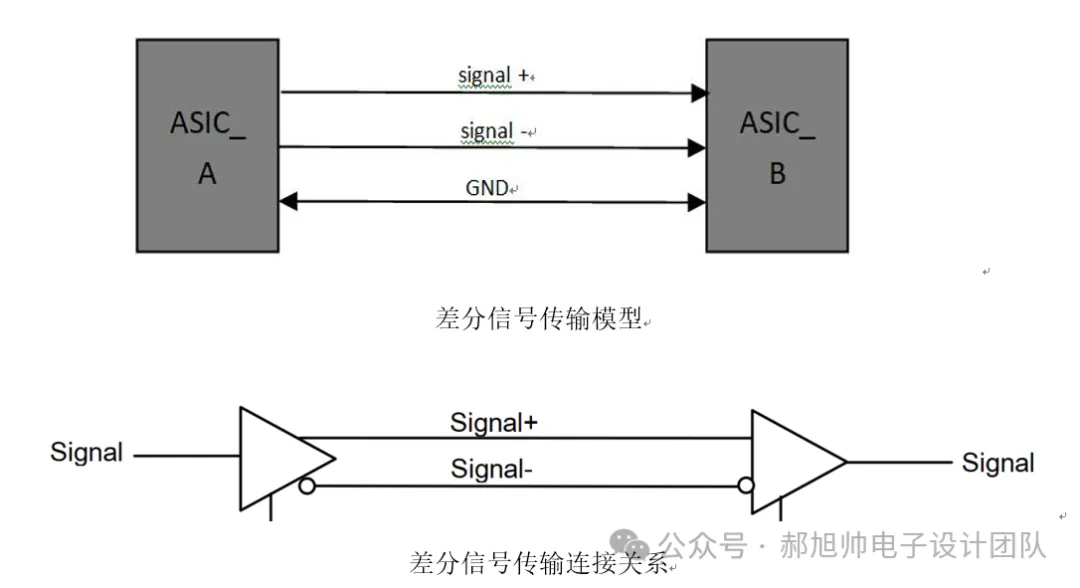

差分信号进行传输时,使用两条传输线传输信号,ASIC_A按照信号的差值进行逻辑驱动,ASIC_B也按照信号的差值进行逻辑捕获。差分信号具有很强的抗共模干扰能力,因此它的速度性能和噪声性能较好,多用于高速数据传输。LVDS标准为I/O差分标准。

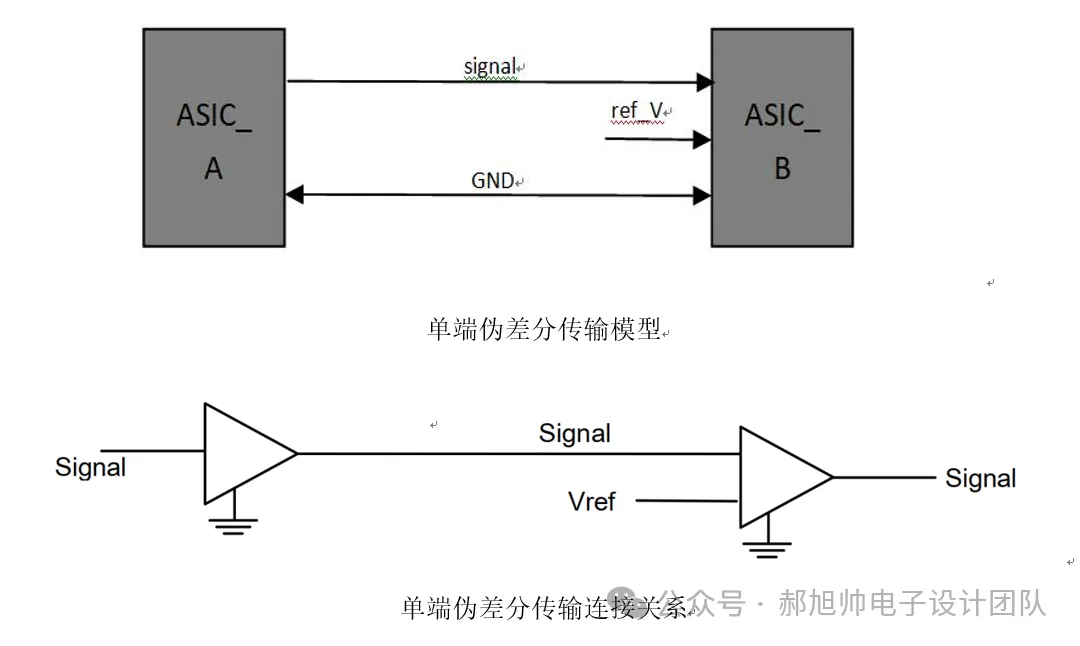

单端伪差分信号进行传输时,使用一条传输线传输信号,ASIC_A正常发送逻辑值,ASIC_B接收是相对于ref_V(参考电压)进行接收。ref_V一般为传输电压的一半。接收端的信号电压低于ref_V当作逻辑“低”,高于ref_V当作逻辑“高”。

双端伪差分信号传输时,使用两条传输线分别传输信号的“正”、“反”逻辑。ASIC_A发送信号的电平与“反”电平,接收端按照单端伪差分接收标准接收,然后取出其中一路作为输出。

伪差分标准的信号输出幅度较小,电源逻辑比真差分电路简单,噪声容限大而且与JEDEC支持的SDRAM的L-Bank结构相对应,所以被应用于DDR/DDR2/DDR3接口,数据速率可以达到Gbit/s。

从发送端发出信号,经过线路的干扰影响,其电平可能升高或者降低,因而接收端必须在一个电平范围内判断它的逻辑值。这个电平范围称为噪声容限(Noise Margin, NM)。不同的信号传输方式和I/O标准由不同的噪声容限和逻辑值判断方式。

在单端信号传输高电平中,ASIC_A输出高电平的电压值要在VOH_max和VOH_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIH_max大于VOH_max,VIH_min小于VOH_min。而VIH_max和VOH_max都是受到电源电压的影响,并且越高肯定会判断成为逻辑高,因此VIH_min和VOH_min才是影响传输的关键。所以高电平的噪声容限(NMH)为VOH_min — VIH_min。对于低电平而言,ASIC_A输出高电平的电压值要在VOL_max和VOL_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIL_max大于VOL_max,VIL_min小于VOL_min。而VIL_min和VOL_min都是受到GND的影响,并且越低肯定会判断成为逻辑低,因此VIL_max和VOH_max才是影响传输的关键。所以低电平的噪声容限(NML)为VIL_max — VOL_max。如果发送端和接收端不能满足以上条件,那么通信就会受到影响。

本篇内容中有部分资源来源于网络,如有侵权,请联系作者。

如果您觉得本公众号还不错的话,可以推给身边的朋友们,感谢并祝好!