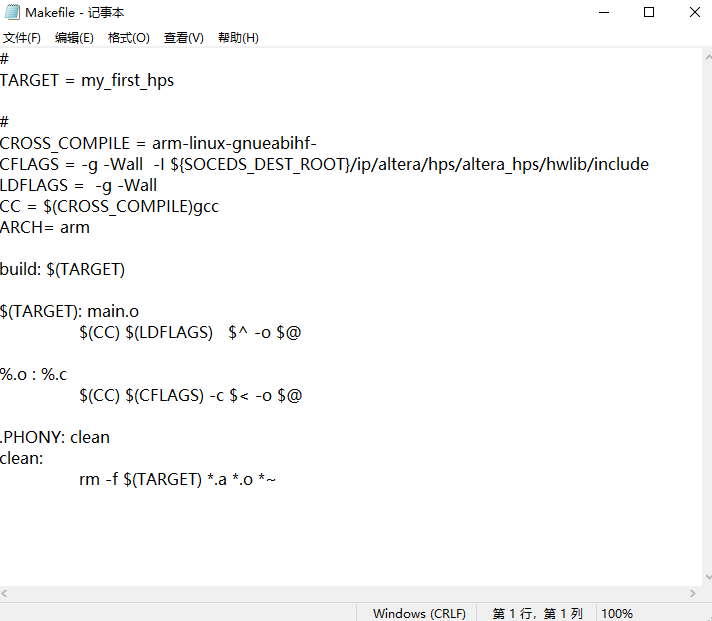

Makefile文件(DE1-soc软件实验”hello_word")

DE1-soc软件实验”hello_word"中,hello_word此程序很好理解,那Makefile文件又如何理解呢?

所要完成的Makefile 文件描述了整个工程的编译、连接等规则。其中包括:工程中的哪些源文件需要编译以及如何编译、需要创建那些库文件以及如何创建这些库文件、如何最后产生我们想要的可执行文件。尽管看起来可能是很复杂的事情,但是为工程编写Makefile 的好处是能够使用一行命令来完成"自动化编译",一旦提供一个(通常对于一个工程来说会是多个)正确的 Makefile。编译整个工程你所要做的唯一的一件事就是在shell 提示符下输入make命令。整个工程完全自动编译,极大提高了效率。

make是一个命令工具,它解释Makefile 中的指令(应该说是规则)。在Makefile文件中描述了整个工程所有文件的编译顺序、编译规则。Makefile 有自己的书写格式、关键字、函数。像C 语言有自己的格式、关键字和函数一样。而且在Makefile 中可以使用系统shell所提供的任何命令来完成想要的工作。Makefile(在其它的系统上可能是另外的文件名)在绝大多数的IDE 开发环境中都在使用,已经成为一种工程的编译方法。(来自360百科)

所以make命令执行时,需要一个 Makefile 文件,以告诉make命令需要怎么样的去编译和链接程序。也就是后面编写完makefile文件后,在Embedded_Command_Shell.bat输入make时会多出一个main.o文件。

Makefile 文件具体的写法和语言格式很复杂,下面简单介绍一下本次书写的程序;

# TARGET = my_first_hps //定义了生成的可执行文件的名字 //arm-linux-gnueadbihf-gcc的交叉编译环境 # CROSS_COMPILE = arm-linux-gnueabihf- CFLAGS = -g -Wall -I ${SOCEDS_DEST_ROOT}/ip/altera/hps/altera_hps/hwlib/include //CFLAGS: 指定头文件(.h文件)的路径 LDFLAGS = -g -Wall //LDFLAGS:gcc 等编译器会用到的一些优化参数,也可以在里面指定库文件的位置。 CC = $(CROSS_COMPILE)gcc ARCH= arm build: $(TARGET) $(TARGET): main.o $(CC) $(LDFLAGS) $^ -o $@ %.o : %.c $(CC) $(CFLAGS) -c $< -o $@ .PHONY: clean clean: rm -f $(TARGET) *.a *.o *~

这里又要引入两个名词:宿主机(Host),和目标机(Target)。开发板由于硬件所限不能直接在本地建立起开发环境,需要在配置高的个人电脑上开发完软件后再移植到开发板上运行。此处的开发板就是Target,个人电脑就是Host。

简单来说,交叉编译就是在一个平台上生成另一个平台上的可执行代码。由于Target和Host的平台不一样(平台包括体系结构,最直观的就是CPU不一样,一个是x86,另一个是ARM,使用的汇编语言都不一样),不能使用Host的编译工具,而需要在Host中安装Target的编译工具链(cross compilation tool chain),来编译得到的运行于Target上的可执行代码。

(来源:CSDN 原文:https://blog.csdn.net/lucykingljj/article/details/40619671 )

浙公网安备 33010602011771号

浙公网安备 33010602011771号