千兆以太网_发送模块设计_udp_rgmii_tx

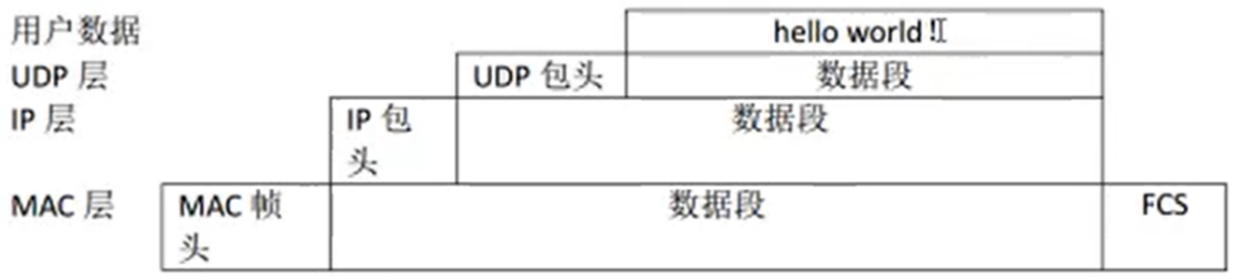

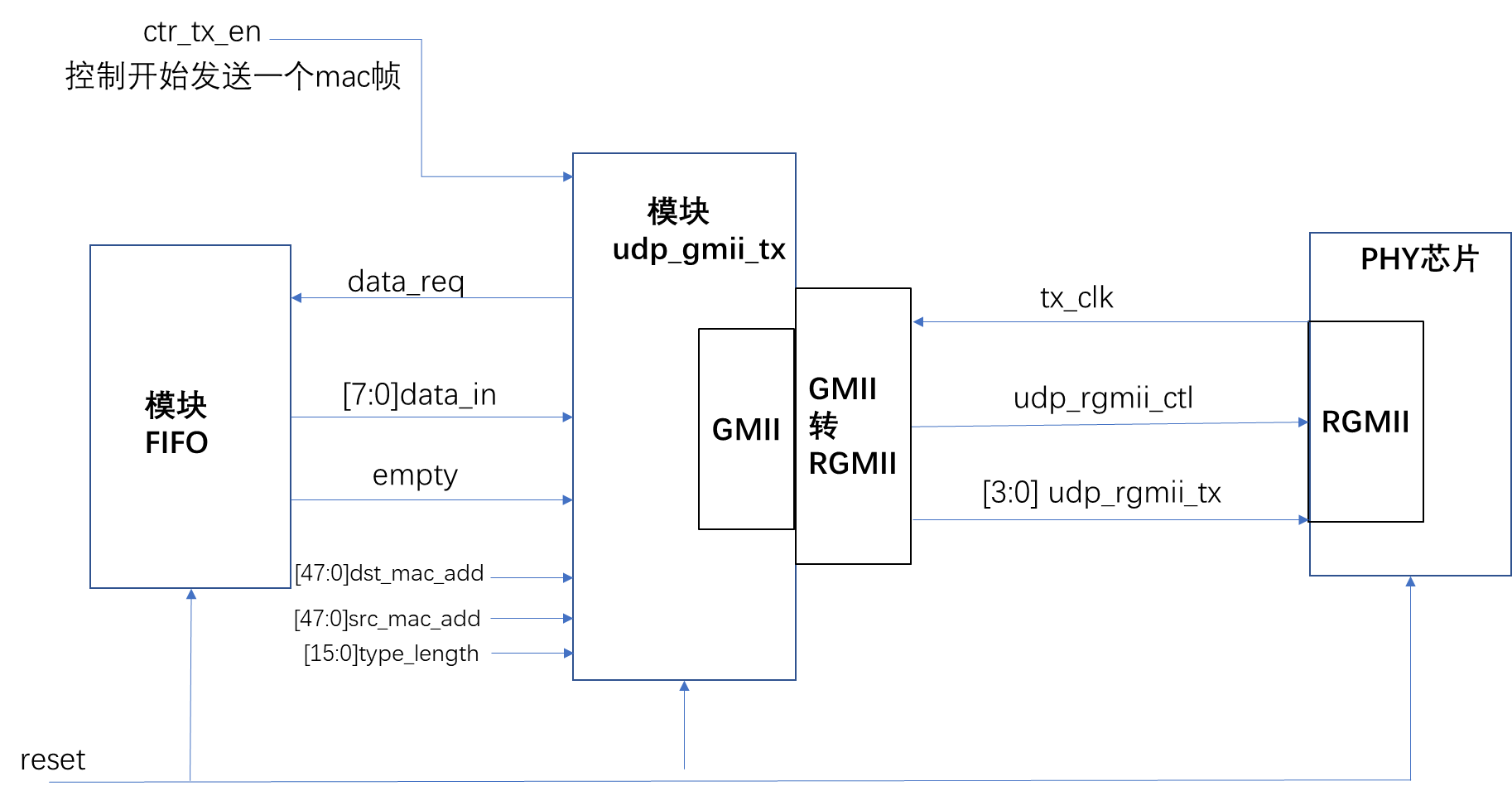

一.功能:在FPGA开发板上,用户数据存于FIFO,经过UDP,IP,MAC封装,通过GMII发出,再经过GMII转RGMII接口发送出去。完整的以太网应该包括收发功能,这里介绍发送模块。

二.实现:序列机

三.过程:发送顺序: MAC帧头——IP包头——UDP包头——用户数据——FCS校验字段

封装顺序: UDP层封装——IP层封装——MAC层封装

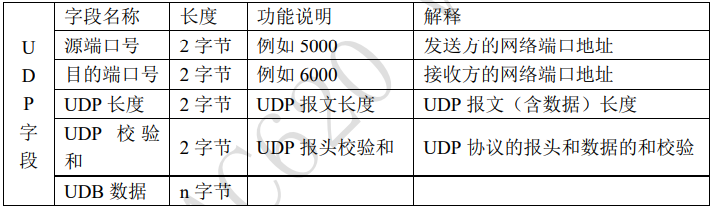

①UDP层封装

源端口号和目的端口号:已知,

UDP长度 = fifo中的data_counter+报头长度

UDP校验计算复杂,可以置零(能成功发送)

UDP数据即用户数据,存于FIFO中。

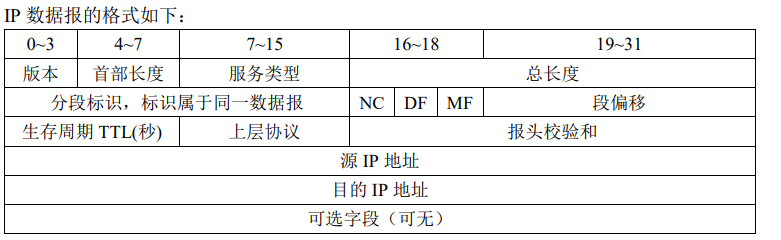

②IP层封装

IP报头校验和:用一个模块来计算即可

可以小兵以太网工具设置数据。

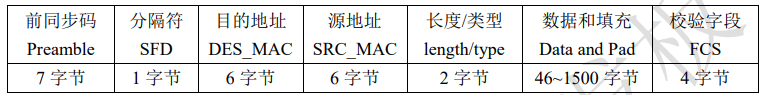

③MAC层封装

难点在于FCS校验:

①4位crc32校验(MII):无论是目的/源mac,长度类型,还是数据段,每个字节都要先输出低4位,再输出高四位,进入crc32模块进行计算。输出的crc32值可能与软件计算结果是翻高低位转的,由计算程序决定。此外,在网站上获得的crc32计算程序,需要修改:输入计算模块后高低位翻转,再计算,结果再翻转。

②8位crc32校验(GMII):直接按顺序输出即可,不用先输出低4位再输出高4位。输入计算模块后高低位翻转,再计算,结果再翻转。

四.系统模型:

模块udp_gmii_tx:使用计数器实现序列机发送帧,在发送用户数据时一直停在一个计数值直到把所有用户数据发送出去,利用fifo中的empty信号跳出这个计数值,继续发送FCS校验值。本模块包括crc32自动计算,IP报头校验自动计算,输入输出数据为8位宽。

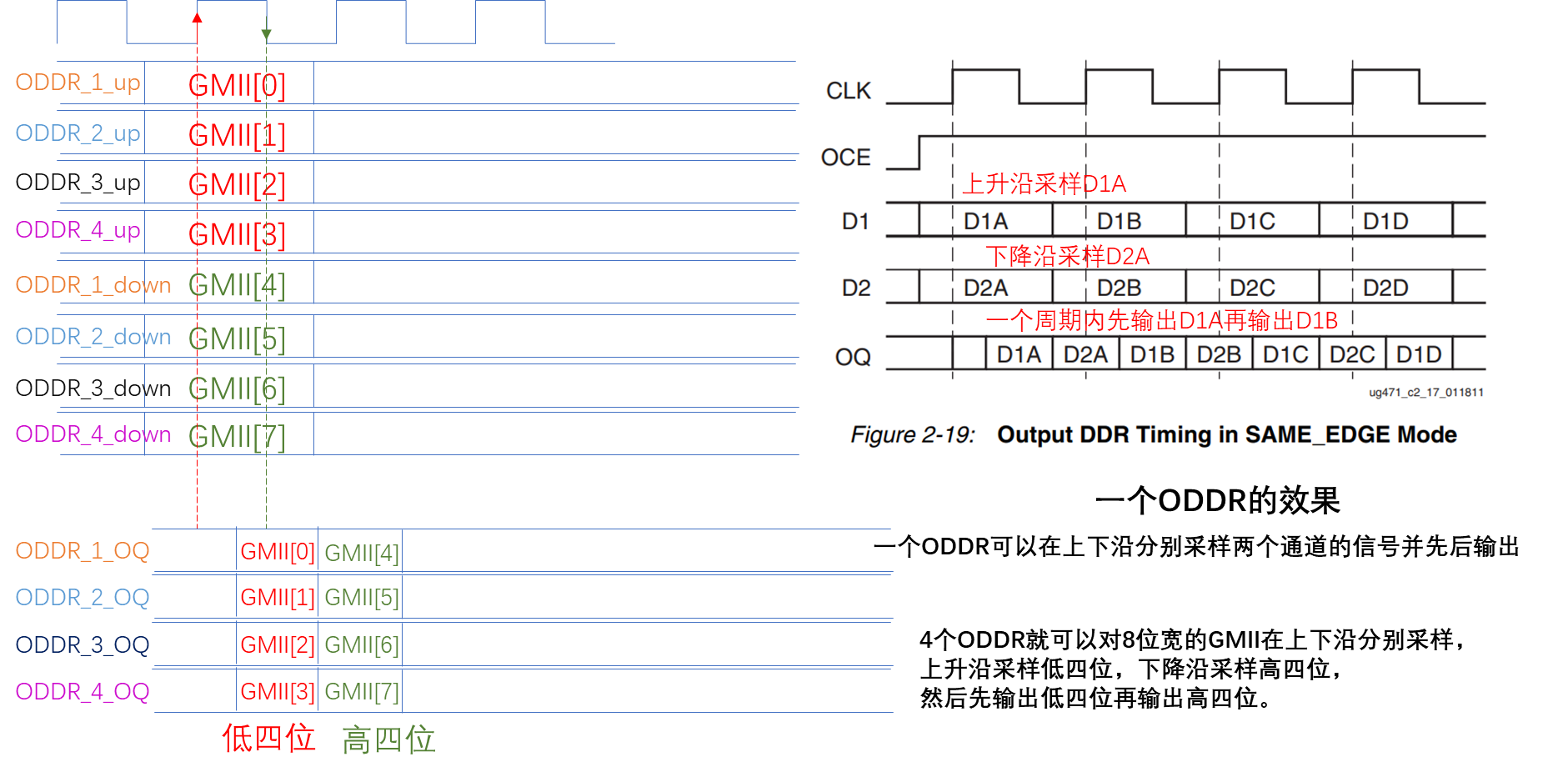

模块GMII转RGMII:这个模块是难点,把8位宽的数据转变为4位宽,利用双沿采样实现,在Xilinx中例化原语和altera例化IP核,可以较快实现。理解如下:(Xilinx原语的介绍见ug471)

原语:器件底层硬件中的功能模块,使用专门的资源来实现功能,可以直接例化,不用定制IP,调用方法更简单,一般只用于实现简单的功能。

转换代码:

module rgmii_tx(

//GMII发送端口

input gmii_tx_clk , //GMII发送时钟

input gmii_tx_en , //GMII输出数据有效信号

input [7:0] gmii_txd , //GMII输出数据

//RGMII发送端口

output rgmii_txc , //RGMII发送数据时钟

output rgmii_tx_ctl, //RGMII输出数据有效信号

output [3:0] rgmii_txd //RGMII输出数据

);

//*****************************************************

//** main code

//*****************************************************

assign rgmii_txc = gmii_tx_clk;

//输出双沿采样寄存器 (rgmii_tx_ctl)

ODDR #(

.DDR_CLK_EDGE ("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT (1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE ("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q (rgmii_tx_ctl), // 1-bit DDR output

.C (gmii_tx_clk), // 1-bit clock input

.CE (1'b1), // 1-bit clock enable input

.D1 (gmii_tx_en), // 1-bit data input (positive edge)

.D2 (gmii_tx_en), // 1-bit data input (negative edge)

.R (1'b0), // 1-bit reset

.S (1'b0) // 1-bit set

);

genvar i;

generate for (i=0; i<4; i=i+1)

begin : txdata_bus

//输出双沿采样寄存器 (rgmii_txd)

ODDR #(

.DDR_CLK_EDGE ("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT (1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE ("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q (rgmii_txd[i]), // 1-bit DDR output

.C (gmii_tx_clk), // 1-bit clock input

.CE (1'b1), // 1-bit clock enable input

.D1 (gmii_txd[i]), // 1-bit data input (positive edge)

.D2 (gmii_txd[4+i]),// 1-bit data input (negative edge)

.R (1'b0), // 1-bit reset

.S (1'b0) // 1-bit set

);

end

endgenerate

endmodule

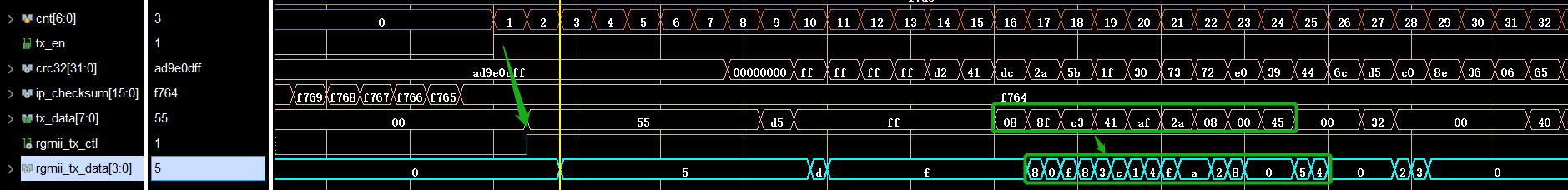

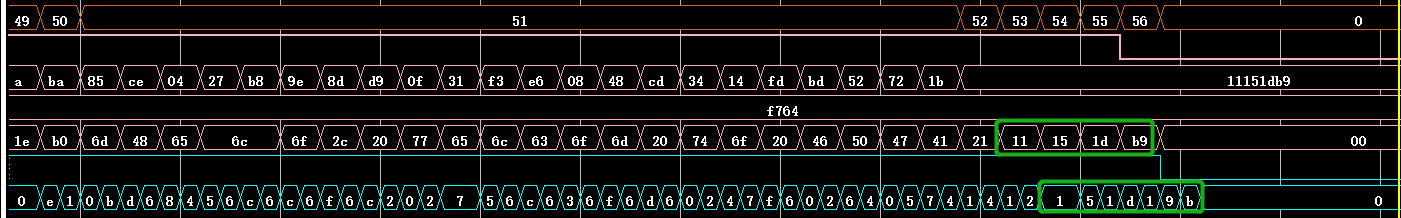

五.仿真结果:gmii_2_rgmii

六.板级验证

发送模块实现从fpga发送数据到上位机,因此只需要知道上位机的MAC地址和IP地址即可,上位机接收到udp帧后会解析出该帧的mac和ip地址与本机是否符合,符合则把数据都解析出来,在这个过程中,fpga的mac和ip帧是不重要的,我们可以随便设置,最后都会被上位机解析出来;而目的mac和ip地址就必须是上位机的,才能被判定成功,准确接收。

理论上来说,接入公共互联网的设备都需要有其唯一的mac和ip地址,才不会冲突。但是这里我们的fpga并不接入公共网络,而是接入与上位机组成的局域网,所以只要不跟上位机地址冲突就可以了。

另:fpga开发板上本来就没有网卡,所以无所谓mac地址。实现以太网模块是外接扩展芯片以太网模块ACM8211,以此来实现数据的串并转换,并没有验证功能。(芯片为RTL8211,高度集成的以太网收发器,属于Realtek(瑞昱半导体)公司).

浙公网安备 33010602011771号

浙公网安备 33010602011771号