摘要:  前情提要 米联客FDMA驱动OV5640摄像头—基于野火Zynq7020开发板 本文在此基础上,实现了双路视频拼接。将ov5640输出的1024600的图像数据缩放为512600,分两路写入ddr3,并且显示在1024*600的RGB屏幕中。 纯FPGA也可以按此方法实现。 总体BLOCK DESI 阅读全文

前情提要 米联客FDMA驱动OV5640摄像头—基于野火Zynq7020开发板 本文在此基础上,实现了双路视频拼接。将ov5640输出的1024600的图像数据缩放为512600,分两路写入ddr3,并且显示在1024*600的RGB屏幕中。 纯FPGA也可以按此方法实现。 总体BLOCK DESI 阅读全文

前情提要 米联客FDMA驱动OV5640摄像头—基于野火Zynq7020开发板 本文在此基础上,实现了双路视频拼接。将ov5640输出的1024600的图像数据缩放为512600,分两路写入ddr3,并且显示在1024*600的RGB屏幕中。 纯FPGA也可以按此方法实现。 总体BLOCK DESI 阅读全文

前情提要 米联客FDMA驱动OV5640摄像头—基于野火Zynq7020开发板 本文在此基础上,实现了双路视频拼接。将ov5640输出的1024600的图像数据缩放为512600,分两路写入ddr3,并且显示在1024*600的RGB屏幕中。 纯FPGA也可以按此方法实现。 总体BLOCK DESI 阅读全文

posted @ 2024-06-28 19:04

carpe--diem

阅读(206)

评论(0)

推荐(0)

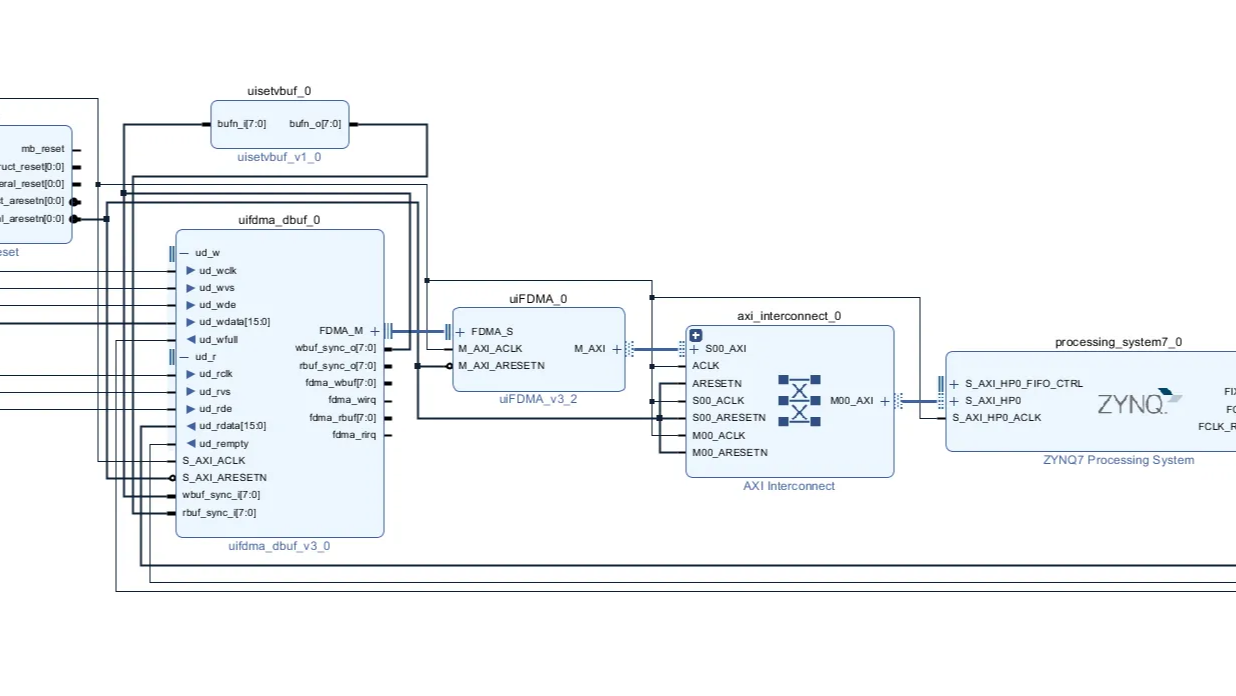

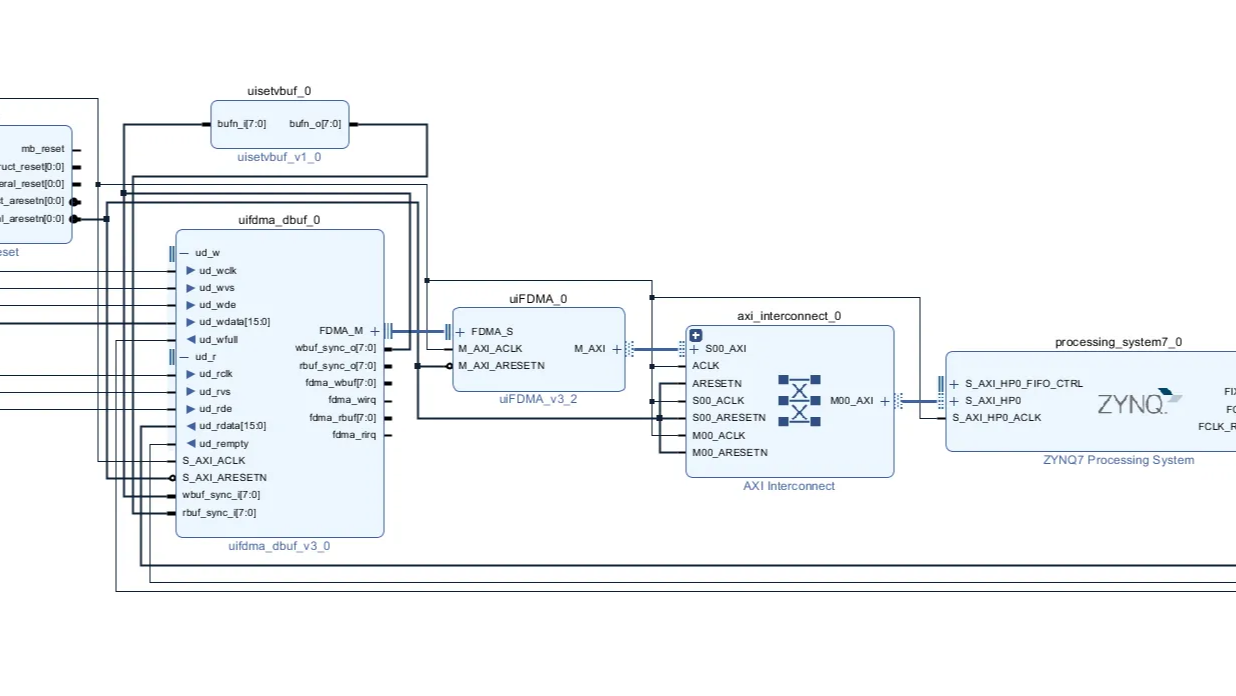

摘要:  使用米联客的ddr3缓存方案 FDMA驱动OV5640摄像头在RGB888屏幕上显示。 总体BLOCK DESIGN框架图 RTC框架图 FDMA设置 FDMA控制器设置 帧选择IP设置 IP核封装及代码在工程文件中 参考 FDMA3.1数据缓存方案全网最细讲解,自创升级版,提供3套视频和音频缓存工 阅读全文

使用米联客的ddr3缓存方案 FDMA驱动OV5640摄像头在RGB888屏幕上显示。 总体BLOCK DESIGN框架图 RTC框架图 FDMA设置 FDMA控制器设置 帧选择IP设置 IP核封装及代码在工程文件中 参考 FDMA3.1数据缓存方案全网最细讲解,自创升级版,提供3套视频和音频缓存工 阅读全文

使用米联客的ddr3缓存方案 FDMA驱动OV5640摄像头在RGB888屏幕上显示。 总体BLOCK DESIGN框架图 RTC框架图 FDMA设置 FDMA控制器设置 帧选择IP设置 IP核封装及代码在工程文件中 参考 FDMA3.1数据缓存方案全网最细讲解,自创升级版,提供3套视频和音频缓存工 阅读全文

使用米联客的ddr3缓存方案 FDMA驱动OV5640摄像头在RGB888屏幕上显示。 总体BLOCK DESIGN框架图 RTC框架图 FDMA设置 FDMA控制器设置 帧选择IP设置 IP核封装及代码在工程文件中 参考 FDMA3.1数据缓存方案全网最细讲解,自创升级版,提供3套视频和音频缓存工 阅读全文

posted @ 2024-06-28 15:04

carpe--diem

阅读(310)

评论(0)

推荐(0)

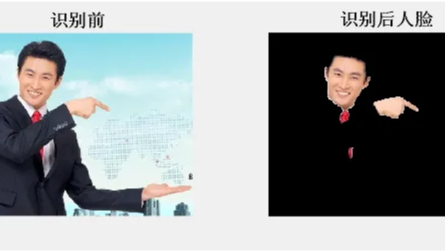

使用芯片为ZYNQ—7020,基于野火FPGA ZYNQ开发板 肤色模型简介 YCrCb也称为YUV,主要用于优化彩色视频信号的传输。与RGB视频信号传输相比,它最大的优点在于只需占用极少的频宽(RGB要求三个独立的视频信号同时传输)。其中“Y”表示明亮度(Luminance或Luma),也就是灰阶

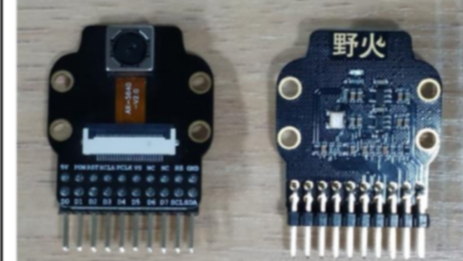

使用芯片为ZYNQ—7020,基于野火FPGA ZYNQ开发板 肤色模型简介 YCrCb也称为YUV,主要用于优化彩色视频信号的传输。与RGB视频信号传输相比,它最大的优点在于只需占用极少的频宽(RGB要求三个独立的视频信号同时传输)。其中“Y”表示明亮度(Luminance或Luma),也就是灰阶  概述 OV5640 是一款 1/4 英寸单芯片图像传感器,其感光阵列达到 25921944(即 500W 像素),能实现最快 15fps QSXVGA(25921944)或者 90fps VGA(640*480)分辨率的图像采集。传感器采用 OmniVision 推出的 OmniBSI(背面照度)技

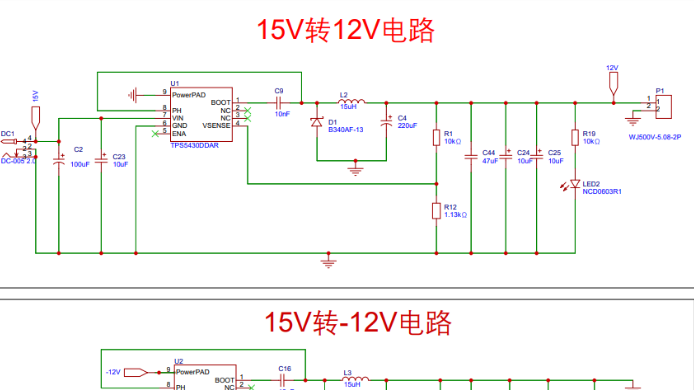

概述 OV5640 是一款 1/4 英寸单芯片图像传感器,其感光阵列达到 25921944(即 500W 像素),能实现最快 15fps QSXVGA(25921944)或者 90fps VGA(640*480)分辨率的图像采集。传感器采用 OmniVision 推出的 OmniBSI(背面照度)技  使用TPS5430将15v电路转换成正负12V,之后使用LM317 LM337将正负12V转换成正负5V电路。 实测 15v电路纹波1.5mv,5V电路空载792uV。 不过需要注意的是PCB板子上,我测试点留错了。 百度网盘: 链接: https://pan.baidu.com/s/1uJYGOb

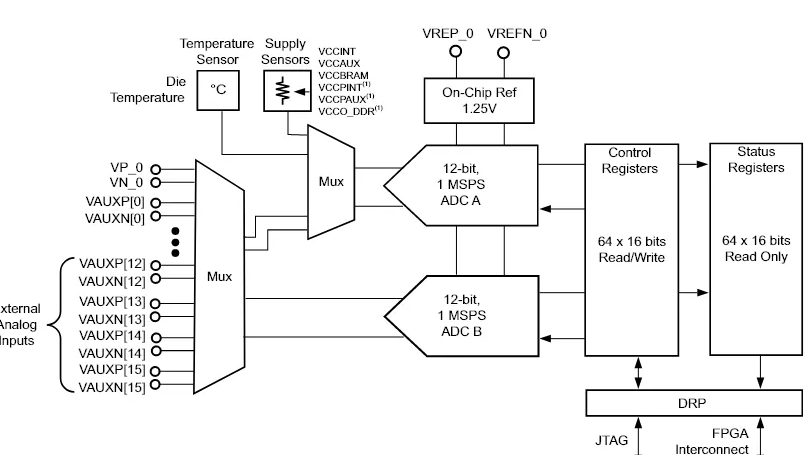

使用TPS5430将15v电路转换成正负12V,之后使用LM317 LM337将正负12V转换成正负5V电路。 实测 15v电路纹波1.5mv,5V电路空载792uV。 不过需要注意的是PCB板子上,我测试点留错了。 百度网盘: 链接: https://pan.baidu.com/s/1uJYGOb  概述 XADC在Xilinx7系列器件上可用。The XADC is available in all Artix-7, Kintex-7, Virte-7, and Zynq-7000 SoC devices. XADC需要例化使用,但是如果使用JTAG访问的话,就不需要例化,直接在Vivado软

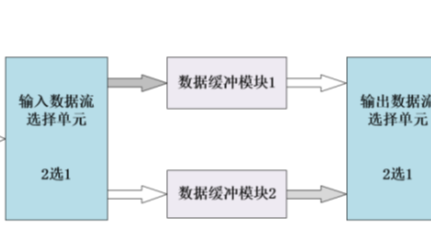

概述 XADC在Xilinx7系列器件上可用。The XADC is available in all Artix-7, Kintex-7, Virte-7, and Zynq-7000 SoC devices. XADC需要例化使用,但是如果使用JTAG访问的话,就不需要例化,直接在Vivado软  乒乓操作常用与对数据流的处理,他可以节约缓存空间,对数据流无缝处理。 理论学习 外部输入数据流通过输入数据流选择单元将数据流输入到数据缓存模块,比较常用的存储单元有双口 RAM, FIFO, SDRAM 等。在第一个缓冲周期,数据流通过“输入数据流选择单元”将数据写入“数据缓冲模块 1”。写完之后进

乒乓操作常用与对数据流的处理,他可以节约缓存空间,对数据流无缝处理。 理论学习 外部输入数据流通过输入数据流选择单元将数据流输入到数据缓存模块,比较常用的存储单元有双口 RAM, FIFO, SDRAM 等。在第一个缓冲周期,数据流通过“输入数据流选择单元”将数据写入“数据缓冲模块 1”。写完之后进  概述 边缘检测, 针对的是灰度图像, 顾名思义,检测图像的边缘, 是针对图像像素点的一种计算, 目的是标识数字图像中灰度变化明显的点。(周围灰度急剧变化的像素的集合,这个突变的就是变化率最大的地方,即一阶导数最大的地方)图像的边缘检测,在保留了图像的重要结构信息的同时,剔除了可以认为不相关的信息,大

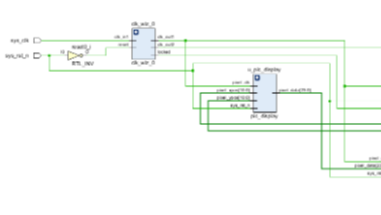

概述 边缘检测, 针对的是灰度图像, 顾名思义,检测图像的边缘, 是针对图像像素点的一种计算, 目的是标识数字图像中灰度变化明显的点。(周围灰度急剧变化的像素的集合,这个突变的就是变化率最大的地方,即一阶导数最大的地方)图像的边缘检测,在保留了图像的重要结构信息的同时,剔除了可以认为不相关的信息,大  前言 如何实现FPGA驱动HDMI显示在之前的文章已经实现了,其参考的代码主要是基于野火FPGA的教程,在正点原子的达芬奇FPGA开发板上实现。 系统框架 这里简单介绍一下各个框架。 1、clk_wiz_0 调用的vivado的PLL生成了两种时钟频率:1280720@60Hz驱动时钟74.25MH

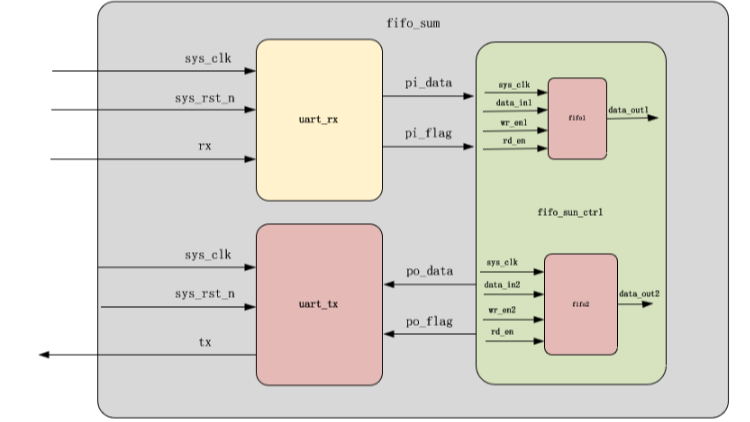

前言 如何实现FPGA驱动HDMI显示在之前的文章已经实现了,其参考的代码主要是基于野火FPGA的教程,在正点原子的达芬奇FPGA开发板上实现。 系统框架 这里简单介绍一下各个框架。 1、clk_wiz_0 调用的vivado的PLL生成了两种时钟频率:1280720@60Hz驱动时钟74.25MH  FIFO三项求和

FIFO三项求和  浙公网安备 33010602011771号

浙公网安备 33010602011771号