04 2022 档案

摘要:Verilog——Vidado中基于ROM IP的sin函数实现 基本原理 使用FPGA的内部ROM记录sin函数数值; 为节省逻辑单元,仅记录步长0.1°,第一象限[0°,90.0°]范围的sin函数数值; 其他象限的函数值由第一象限数值简单计算得到。 具体步骤 一. 生成ROM初始化数据文件(M

阅读全文

摘要:Verilog——数据转换器:1)由宽到窄(32bit到16bit)的数据转换模块 转换目标及基本原理 转换目标 使用FPGA的不同频率和相位的时钟,将低频32bit位宽的数据流转换为倍频16bit位宽的数据流。 时钟 时钟频率:输入时钟频率CLK1X,输出时钟频率CLK2X,f_CLK2X = 2

阅读全文

摘要:Verilog——格雷码与二进制码的相互转换 定义与作用 格雷码是一种相邻数值仅有一个数位发生变化的编码。 格雷码被广泛应用于异步FIFO的数据传输中。当数值从一个时钟域传递到另一个时钟域时,仅有一个比特位的翻转十分重要。 格雷码与二进制码的转换 3bit位宽数据,二进制和格雷码的对应关系 二进制码

阅读全文

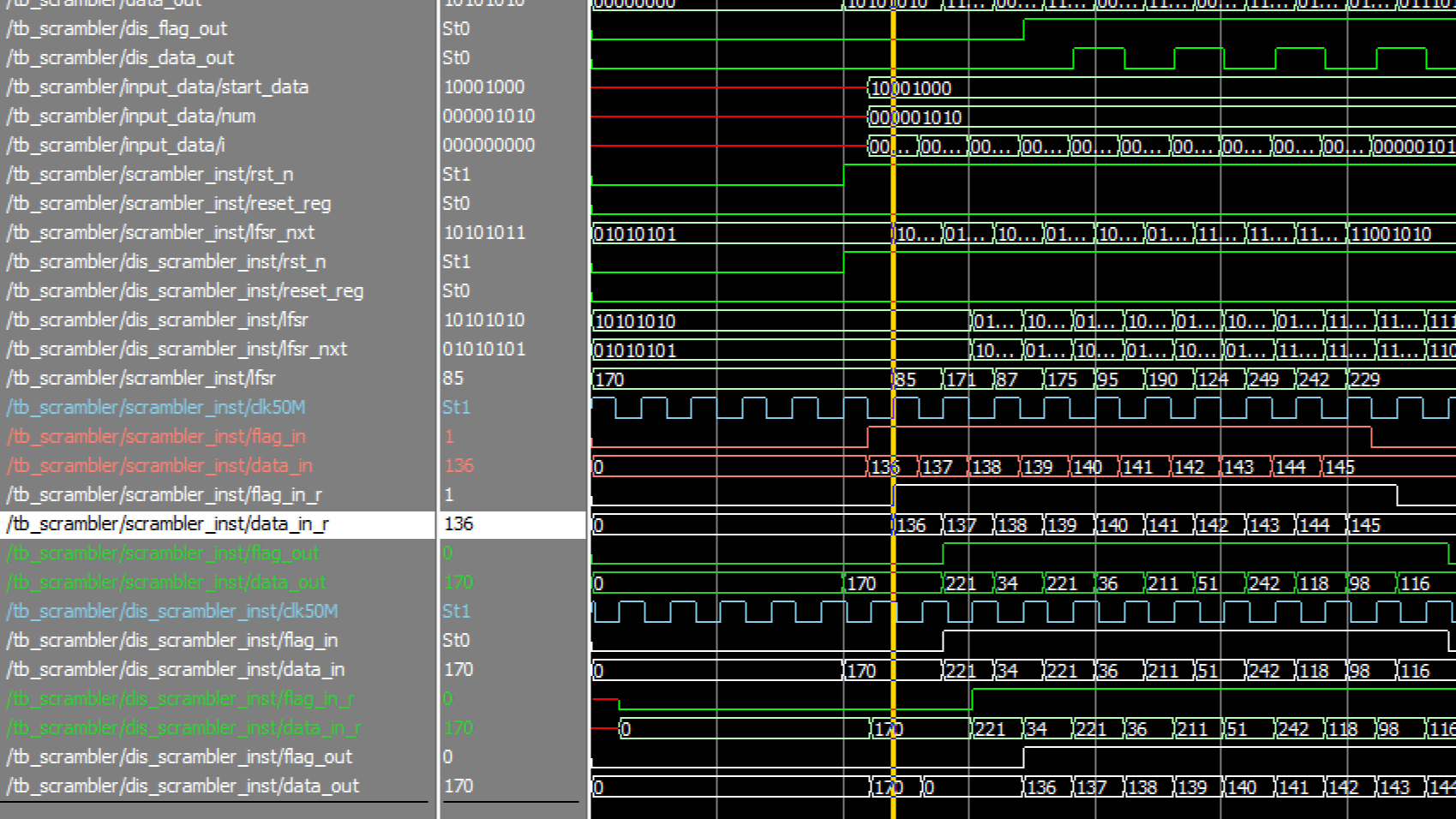

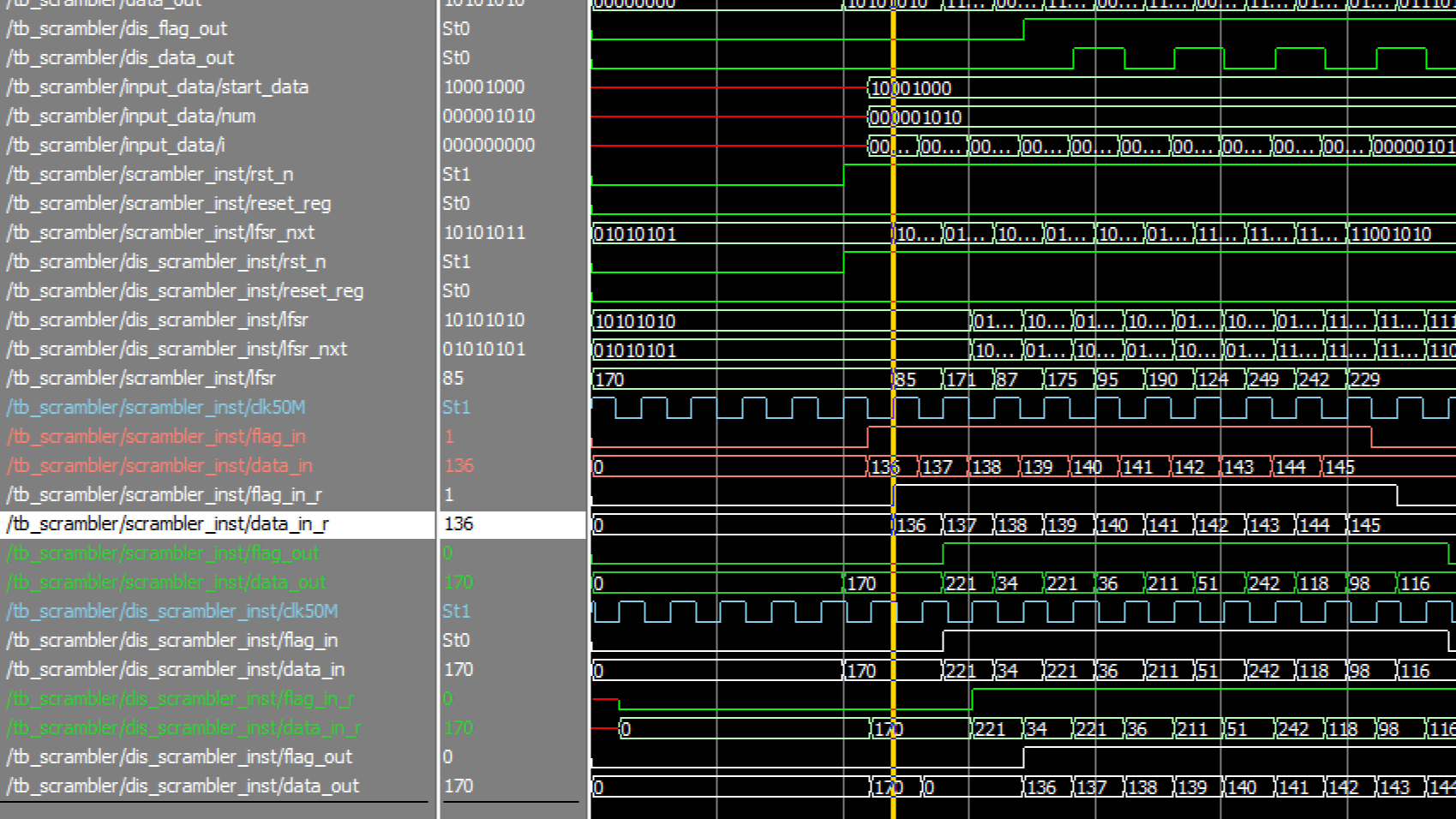

摘要: Verilog 扰码器/解扰器 扰码器 扰码器基于LFSR(线性移位计数器)实现,将输入数据转换为对应的伪随机数据; LFSR(线性移位计数器)将输入数据与内部的寄存器数据反馈异或得到新的寄存器数据输出。 扰码器的优点 基于LFSR,逻辑实现简单,速度快; 可使数据团频谱展宽,减小EMI(电磁干扰)

阅读全文

Verilog 扰码器/解扰器 扰码器 扰码器基于LFSR(线性移位计数器)实现,将输入数据转换为对应的伪随机数据; LFSR(线性移位计数器)将输入数据与内部的寄存器数据反馈异或得到新的寄存器数据输出。 扰码器的优点 基于LFSR,逻辑实现简单,速度快; 可使数据团频谱展宽,减小EMI(电磁干扰)

阅读全文

Verilog 扰码器/解扰器 扰码器 扰码器基于LFSR(线性移位计数器)实现,将输入数据转换为对应的伪随机数据; LFSR(线性移位计数器)将输入数据与内部的寄存器数据反馈异或得到新的寄存器数据输出。 扰码器的优点 基于LFSR,逻辑实现简单,速度快; 可使数据团频谱展宽,减小EMI(电磁干扰)

阅读全文

Verilog 扰码器/解扰器 扰码器 扰码器基于LFSR(线性移位计数器)实现,将输入数据转换为对应的伪随机数据; LFSR(线性移位计数器)将输入数据与内部的寄存器数据反馈异或得到新的寄存器数据输出。 扰码器的优点 基于LFSR,逻辑实现简单,速度快; 可使数据团频谱展宽,减小EMI(电磁干扰)

阅读全文

摘要:Function注意事项 function只能对组合逻辑进行设计,综合得到是组合逻辑单元; function只有一个输出变量,其定义由function名称默认给出; function的名称可以包含位宽,如果没有位宽则输出变量位宽为1bit; function可以有多个输入变量,定义方式与模块(mod

阅读全文