PLL

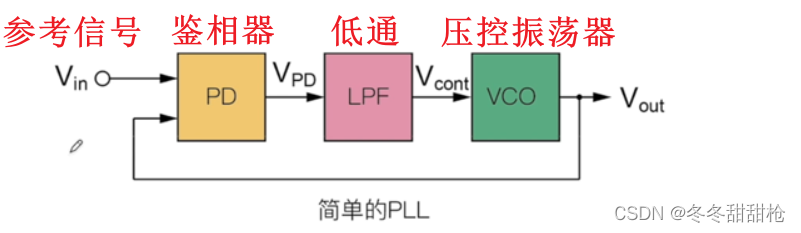

锁相环(Phase-Locked Loop,PLL)是一个能够比较输出与输入相位差的反馈系统,利用外部输入的参考信号控制环路内振荡信号的频率和相位,使振荡信号同步至参考信号。

PLL通常内部集成鉴相器( PFD )、电荷泵(charge pump)、 低通滤波器(LPF )、 压控振荡器( VCO )以及锁定器( LKDT )。

基本原理

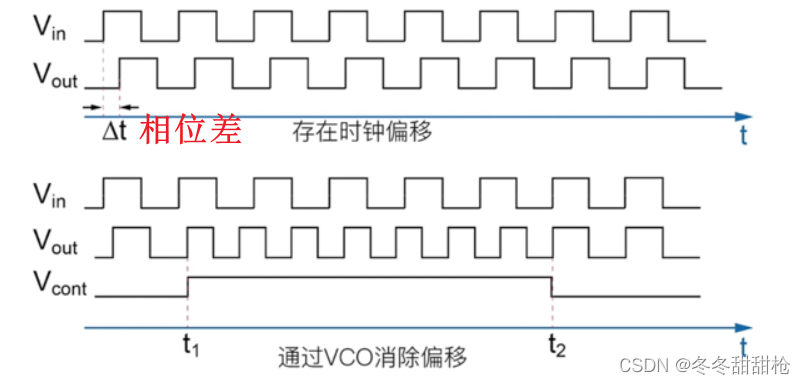

PD检测到Vin和Vout有相位偏移,产生一个检测信号(变化量,包含低频和高频成分),LPF把里面的高频成分滤除,只取低频成分。Vcont上升,让VCO振荡更快一些(Vout相位滞后Vin)使Vout去追赶Vin,减少二者相位差。通过反复的鉴相和调整,最终VCO输出信号和输入参考信号的频率、相位达成一致,这时PLL电路就进入锁定状态。

稳定之后:

即:

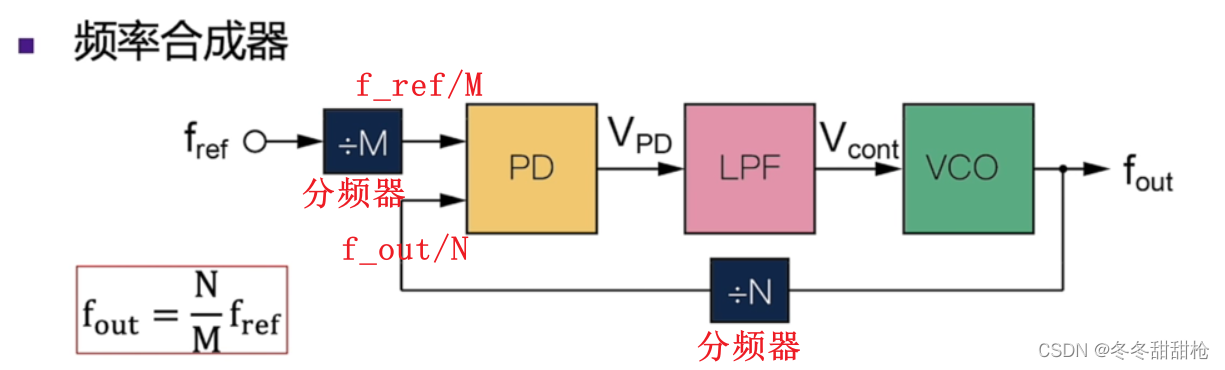

可通过调节N和M来控制输出的频率,其优点是稳定性和信号质量与参考信号等同。

参考:

1. 锁相环基本工作原理

2. 锁相环工作原理

浙公网安备 33010602011771号

浙公网安备 33010602011771号