模型功能

verilog是硬件描述语言的一种,主要用于ASIC和FPGA中,用于实现数字逻辑控制。

相较于VHDL,verilog的语法更加接近C语言,格式也更加宽松,具备更强的灵活性。

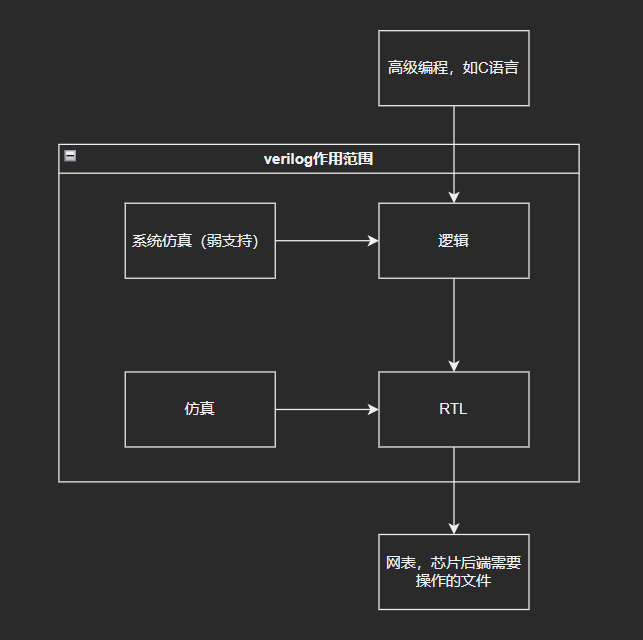

模型框图

- verilog在FPGA内主要用于描述寄存器行为以及连线关系,也可以通过特定的原语实现特殊硬件的调用,比如BRAM、ODDR等。

- 实现层次如下:

实现步骤

- 本合集将以笔者自身常用的一套编写模板进行逐个功能的分析,主要包括以下的内容:

- 文件头的注释及推荐的vscode插件

- module的定义及端口列表的作用

- parameter常数参数及常数函数的应用

- wire和reg类型变量的组合使用

- always和assign的物理含义

- module的引用及TASK的调用

- 调试逻辑及变量声明顺序

- 文件与module的对应关系

- FPGA数字逻辑运行特点及常见方法

最终效果

- 将FPGA中使用到的verilog部分的主要语法和结构进行总结。

- 明确verilog的使用方法,增加设计的规范性,提高设计的一致性。

调用接口

- 无接口

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/18091246,文中资源链接如下:

1. GITHUB开源仓库