Entity: bram_to_vid

- File: bram_to_vid.v

Diagram

Description

Company: Fpga Publish

Engineer: FP

Revision: 0.01

Revision 0.01 - File Created

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| MD_SIM_ABLE | 0 | mode in sim mode enable | |

| NB_BRAM_DLY | 2 | BRAM read delay | |

| WD_BRAM_DAT | 8 | width of bram data | |

| WD_BRAM_ADR | 16 | width of bram address | |

| WD_BRAM_WEN | 1 | width of bram write en | |

| MD_VGA_PARA | "1280_720" | vga mode, 640_480/800_600/1280_720/1920_1080/1024_600 | |

| WD_VID_DATA | 24 | RGB data | |

| WD_VID_INFO | 12 | vid info width | |

| WD_ERR_INFO | 4 | width of error info |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_sys_clk | input | in system clock | |

| i_sys_resetn | input | in system reset_n | |

| i_fram_start_trig | input | frame start and VSYNC high | |

| i_bram_full_trig | input | bram write full and allow read | |

| o_bram_empt_trig | output | bram read empty and req write data | |

| m_err_bram_info1 | output | [WD_ERR_INFO-1:0] | [0]: [1]: |

| bram_master | out | Virtual bus | --read data |

| vid_master | out | Virtual bus | --write RGB data |

Virtual Buses

bram_master

| Port name | Direction | Type | Description |

|---|---|---|---|

| m_bram_rd_addr | output | [WD_BRAM_ADR-1:0] | bram address |

| m_bram_rd_clk | output | bram clock | |

| m_bram_rd_din | output | [WD_BRAM_DAT-1:0] | bram data in |

| m_bram_rd_dout | input | [WD_BRAM_DAT-1:0] | bram data out |

| m_bram_rd_en | output | bram enable | |

| m_bram_rd_rst | output | bram reset high | |

| m_bram_rd_we | output | [WD_BRAM_WEN-1:0] | bram write enable |

vid_master

| Port name | Direction | Type | Description |

|---|---|---|---|

| m_vid_wr_pdata | output | [WD_VID_DATA-1:0] | |

| m_vid_wr_phsync | output | hori sync | |

| m_vid_wr_pvsync | output | vert sync | |

| m_vid_wr_pvde | output | video info |

Signals

| Name | Type | Description |

|---|---|---|

| r_vid_wr_pdata = 0 | reg [WD_VID_DATA-1:0] | RGB data output |

| r_vid_wr_phsync = 0 | reg | hori sync |

| r_vid_wr_pvsync = 0 | reg | vert sync |

| r_vid_wr_pvde = 0 | reg | video info |

| r_vid_wr_hcunt = 0 | reg [WD_VID_INFO-1:0] | vid write hsync count |

| r_vid_wr_vcunt = 0 | reg [WD_VID_INFO-1:0] | vid write vsync count |

| r_bram_rd_addr = 0 | reg [WD_BRAM_ADR-1:0] | bram address |

| r_bram_rd_din = 0 | reg [WD_BRAM_DAT-1:0] | bram data in |

| r_bram_rd_en = 0 | reg | bram enable |

| r_bram_rd_rst = 0 | reg | bram reset high |

| r_bram_rd_we = 0 | reg [WD_BRAM_WEN-1:0] | bram write enable |

| r_bram_empt_trig = 0 | reg | frame sync |

Constants

| Name | Type | Value | Description |

|---|---|---|---|

| H_FRONT | MD_VGA | hsync front | |

| H_SYNC | MD_VGA | hsync time | |

| H_BACK | MD_VGA | hsync back time | |

| H_DISP | MD_VGA_ | hsync disp | |

| H_TOTAL | MD_VGA_ | hsync total time | |

| V_FRONT | MD_VGA | vsync front | |

| V_SYNC | MD_VG | vsync time | |

| V_BACK | MD_VGA | vsync back time | |

| V_DISP | MD_VGA_ | vsync disp | |

| V_TOTAL | MD_VGA_ | vsync total time |

Processes

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

vid interface

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

BRAM interface

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

frame sync

/*

code

*/

// *******************************************************************************

//!Company: Fpga Publish

//!

//!Engineer: FP

//!

//

// Create Date: 2024/01/20 13:03:28

// Design Name:

// Module Name: bram_to_vid

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

//!-----------------

//!Revision: 0.01

//!

//!Revision 0.01 - File Created

//!

// Additional Comments:

//

// *******************************************************************************

`timescale 1ns / 1ps

module bram_to_vid #(

//sim mode

parameter MD_SIM_ABLE = 0,//!mode in sim mode enable

//bram bus

parameter NB_BRAM_DLY = 2, //! BRAM read delay

parameter WD_BRAM_DAT = 8, //! width of bram data

parameter WD_BRAM_ADR = 16, //! width of bram address

parameter WD_BRAM_WEN = 1 , //! width of bram write en

//vid bus

parameter MD_VGA_PARA = "1280_720", //! vga mode, 640_480/800_600/1280_720/1920_1080/1024_600

parameter WD_VID_DATA = 24, //! RGB data

parameter WD_VID_INFO = 12, //! vid info width

//error info

parameter WD_ERR_INFO = 4 //!width of error info

)(

//sy stem signals

input i_sys_clk , //!in system clock

input i_sys_resetn, //!in system reset_n

//data full trig

input i_fram_start_trig, //! frame start and VSYNC high

input i_bram_full_trig, //! bram write full and allow read

output o_bram_empt_trig, //! bram read empty and req write data

//! @virtualbus bram_master @dir out --read data

output [WD_BRAM_ADR-1:0] m_bram_rd_addr, //! bram address

output m_bram_rd_clk , //! bram clock

output [WD_BRAM_DAT-1:0] m_bram_rd_din , //! bram data in

input [WD_BRAM_DAT-1:0] m_bram_rd_dout, //! bram data out

output m_bram_rd_en , //! bram enable

output m_bram_rd_rst , //! bram reset high

output [WD_BRAM_WEN-1:0] m_bram_rd_we , //! bram write enable

//! @end

//! @virtualbus vid_master @dir out --write RGB data

output [WD_VID_DATA-1:0] m_vid_wr_pdata , //! RGB data output

output m_vid_wr_phsync, //! hori sync

output m_vid_wr_pvsync, //! vert sync

output m_vid_wr_pvde , //! video info

//! @end

//![0]:

//![1]:

//error info feedback

output [WD_ERR_INFO-1:0] m_err_bram_info1 //!master of error info

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

localparam H_FRONT = MD_VGA_PARA == "640_480" ? 12'd16 : //! hsync front

MD_VGA_PARA == "800_600" ? 12'd40 :

MD_VGA_PARA == "1280_720" ? 12'd110 :

MD_VGA_PARA == "1920_1080" ? 12'd88 :

MD_VGA_PARA == "1024_600" ? 12'd160 :

12'd16 ;

localparam H_SYNC = MD_VGA_PARA == "640_480" ? 12'd96 : //! hsync time

MD_VGA_PARA == "800_600" ? 12'd128 :

MD_VGA_PARA == "1280_720" ? 12'd40 :

MD_VGA_PARA == "1920_1080" ? 12'd44 :

MD_VGA_PARA == "1024_600" ? 12'd40 :

12'd96 ;

localparam H_BACK = MD_VGA_PARA == "640_480" ? 12'd48 : //! hsync back time

MD_VGA_PARA == "800_600" ? 12'd88 :

MD_VGA_PARA == "1280_720" ? 12'd220 :

MD_VGA_PARA == "1920_1080" ? 12'd148 :

MD_VGA_PARA == "1024_600" ? 12'd120 :

12'd48 ;

localparam H_DISP = MD_VGA_PARA == "640_480" ? 12'd640 : //! hsync disp

MD_VGA_PARA == "800_600" ? 12'd800 :

MD_VGA_PARA == "1280_720" ? 12'd1280:

MD_VGA_PARA == "1920_1080" ? 12'd1920:

MD_VGA_PARA == "1024_600" ? 12'd1024:

12'd640;

localparam H_TOTAL = MD_VGA_PARA == "640_480" ? 12'd800 : //! hsync total time

MD_VGA_PARA == "800_600" ? 12'd1056:

MD_VGA_PARA == "1280_720" ? 12'd1650:

MD_VGA_PARA == "1920_1080" ? 12'd2200:

MD_VGA_PARA == "1024_600" ? 12'd1344:

12'd800;

localparam V_FRONT = MD_VGA_PARA == "640_480" ? 12'd10 : //! vsync front

MD_VGA_PARA == "800_600" ? 12'd1 :

MD_VGA_PARA == "1280_720" ? 12'd5 :

MD_VGA_PARA == "1920_1080" ? 12'd4 :

MD_VGA_PARA == "1024_600" ? 12'd12 :

12'd10 ;

localparam V_SYNC = MD_VGA_PARA == "640_480" ? 12'd2 : //! vsync time

MD_VGA_PARA == "800_600" ? 12'd4 :

MD_VGA_PARA == "1280_720" ? 12'd5 :

MD_VGA_PARA == "1920_1080" ? 12'd5 :

MD_VGA_PARA == "1024_600" ? 12'd3 :

12'd2 ;

localparam V_BACK = MD_VGA_PARA == "640_480" ? 12'd33 : //! vsync back time

MD_VGA_PARA == "800_600" ? 12'd23 :

MD_VGA_PARA == "1280_720" ? 12'd20 :

MD_VGA_PARA == "1920_1080" ? 12'd36 :

MD_VGA_PARA == "1024_600" ? 12'd20 :

12'd33 ;

localparam V_DISP = MD_VGA_PARA == "640_480" ? 12'd480 : //! vsync disp

MD_VGA_PARA == "800_600" ? 12'd600 :

MD_VGA_PARA == "1280_720" ? 12'd720 :

MD_VGA_PARA == "1920_1080" ? 12'd1080:

MD_VGA_PARA == "1024_600" ? 12'd600 :

12'd480;

localparam V_TOTAL = MD_VGA_PARA == "640_480" ? 12'd525 : //! vsync total time

MD_VGA_PARA == "800_600" ? 12'd628 :

MD_VGA_PARA == "1280_720" ? 12'd750 :

MD_VGA_PARA == "1920_1080" ? 12'd1125:

MD_VGA_PARA == "1024_600" ? 12'd635 :

12'd525;

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

//! vid interface

reg [WD_VID_DATA-1:0] r_vid_wr_pdata = 0; //! RGB data output

reg r_vid_wr_phsync = 0; //! hori sync

reg r_vid_wr_pvsync = 0; //! vert sync

reg r_vid_wr_pvde = 0; //! video info

assign m_vid_wr_pdata = r_vid_wr_pdata ;

assign m_vid_wr_phsync = r_vid_wr_phsync ;

assign m_vid_wr_pvsync = r_vid_wr_pvsync ;

assign m_vid_wr_pvde = r_vid_wr_pvde ;

//write count

reg r_frame_wr_flag = 0; //! only when frame start then send data

reg [WD_VID_INFO-1:0] r_vid_wr_hcunt = 0; //! vid write hsync count

reg [WD_VID_INFO-1:0] r_vid_wr_vcunt = 0; //! vid write vsync count

// ----------------------------------------------------------

//! BRAM interface

reg [WD_BRAM_ADR-1:0] r_bram_rd_addr = 0;//! bram address

// reg r_bram_rd_clk ; //! bram clock

reg [WD_BRAM_DAT-1:0] r_bram_rd_din = 0;//! bram data in

// reg [WD_BRAM_DAT-1:0] r_bram_rd_dout; //! bram data out

reg r_bram_rd_en = 0;//! bram enable

reg r_bram_rd_rst = 0;//! bram reset high

reg [WD_BRAM_WEN-1:0] r_bram_rd_we = 0;//! bram write enable

assign m_bram_rd_addr = r_bram_rd_addr;

assign m_bram_rd_clk = i_sys_clk;

assign m_bram_rd_din = r_bram_rd_din;

assign m_bram_rd_en = r_bram_rd_en;

assign m_bram_rd_rst = r_bram_rd_rst;

assign m_bram_rd_we = r_bram_rd_we;

// ----------------------------------------------------------

//! frame sync

reg r_bram_empt_trig = 0;

assign o_bram_empt_trig = r_bram_empt_trig;

//========================================================

//always and assign to drive logic and connect

// ----------------------------------------------------------

//! vid interface

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_frame_wr_flag <= 1'b0; //

end

else if(i_fram_start_trig) //

begin

r_frame_wr_flag <= 1'b1;//

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1

&& r_vid_wr_vcunt >= V_TOTAL - 1'b1)

begin

r_frame_wr_flag <= 1'b0;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_hcunt <= 1'b0; //

end

else if(!r_frame_wr_flag)

begin

r_vid_wr_hcunt <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

r_vid_wr_hcunt <= 1'b0; //

end

else

begin

r_vid_wr_hcunt <= r_vid_wr_hcunt + 1'b1;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_vcunt <= 1'b0; //

end

else if(!r_frame_wr_flag) //frame sync

begin

r_vid_wr_vcunt <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

if(r_vid_wr_vcunt >= V_TOTAL - 1'b1) //

begin

r_vid_wr_vcunt <= 1'b0;

end

else

begin

r_vid_wr_vcunt <= r_vid_wr_vcunt + 1'b1;

end

end

end

//vid signal

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pvde <= 1'b0; //

end

else if(r_vid_wr_hcunt >= H_SYNC + H_BACK - 1'b1

&& r_vid_wr_hcunt < H_SYNC + H_BACK + H_DISP - 1'b1

&& r_vid_wr_vcunt >= V_SYNC + V_BACK - 1'b1

&& r_vid_wr_vcunt < V_SYNC + V_BACK + V_DISP - 1'b1) //

begin

r_vid_wr_pvde <= 1'b1; //

end

else

begin

r_vid_wr_pvde <= 1'b0;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pvsync <= 1'b0; //

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

if(r_vid_wr_vcunt >= V_SYNC - 1'b1

&& r_vid_wr_vcunt < V_TOTAL - 1'b1) //when count last then set it low

begin

r_vid_wr_pvsync <= 1'b1;

end

else

begin

r_vid_wr_pvsync <= 1'b0; //

end

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_phsync <= 1'b0; //

end

else if(r_vid_wr_hcunt <= V_SYNC - 1'b1 - 1'b1) //prepare vsync valid

begin

r_vid_wr_phsync <= 1'b0; //

end

else

begin

r_vid_wr_phsync <= 1'b1;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pdata <= 1'b0; //

end

else if(1) //

begin

r_vid_wr_pdata <= {3{m_bram_rd_dout}}; //

end

end

// ----------------------------------------------------------

//! BRAM interface

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_rd_en <= 1'b0; //

end

else if(1) //

begin

r_bram_rd_en <= r_vid_wr_phsync;//

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_rd_addr <= 1'b0;//

end

else if(r_vid_wr_hcunt == 0)

begin

r_bram_rd_addr <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_SYNC + H_BACK - 1 - NB_BRAM_DLY) //bram write addr add

begin

r_bram_rd_addr <= r_bram_rd_addr + 1'b1; //

end

end

// ----------------------------------------------------------

//! frame sync

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_empt_trig <= 1'b0; //

end

else if(r_vid_wr_hcunt == H_SYNC + H_BACK + H_DISP - 2'd2

&& r_vid_wr_pvde) //video enable

begin

r_bram_empt_trig <= 1'b1; //

end

else

begin

r_bram_empt_trig <= 1'b0;

end

end

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

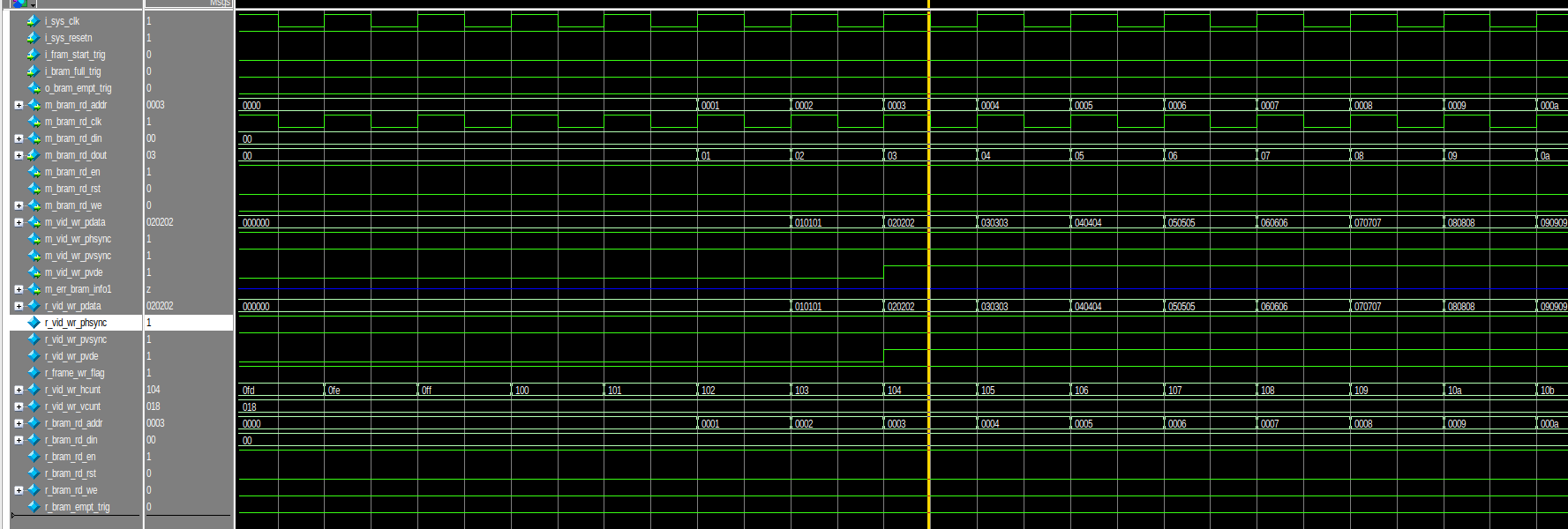

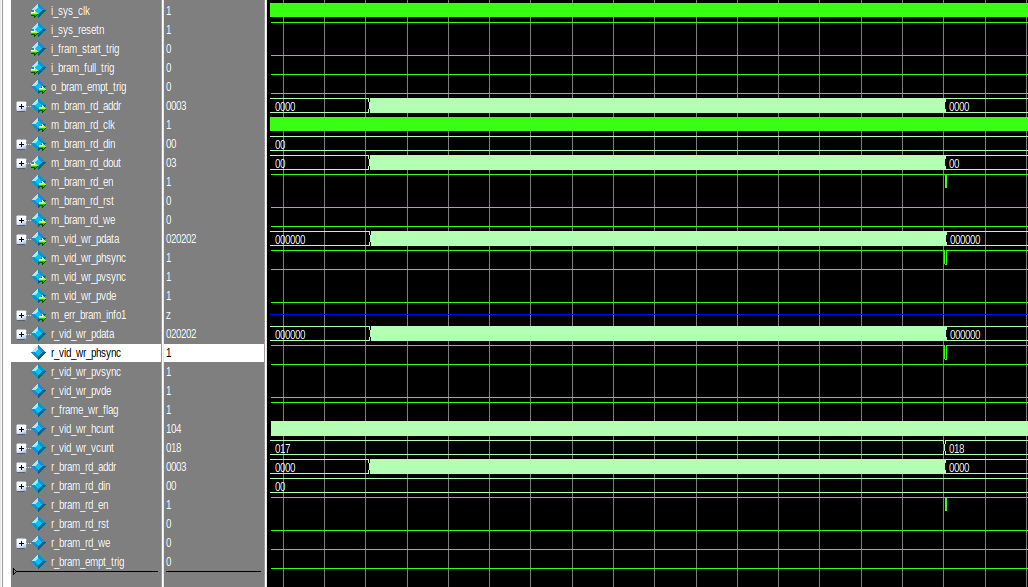

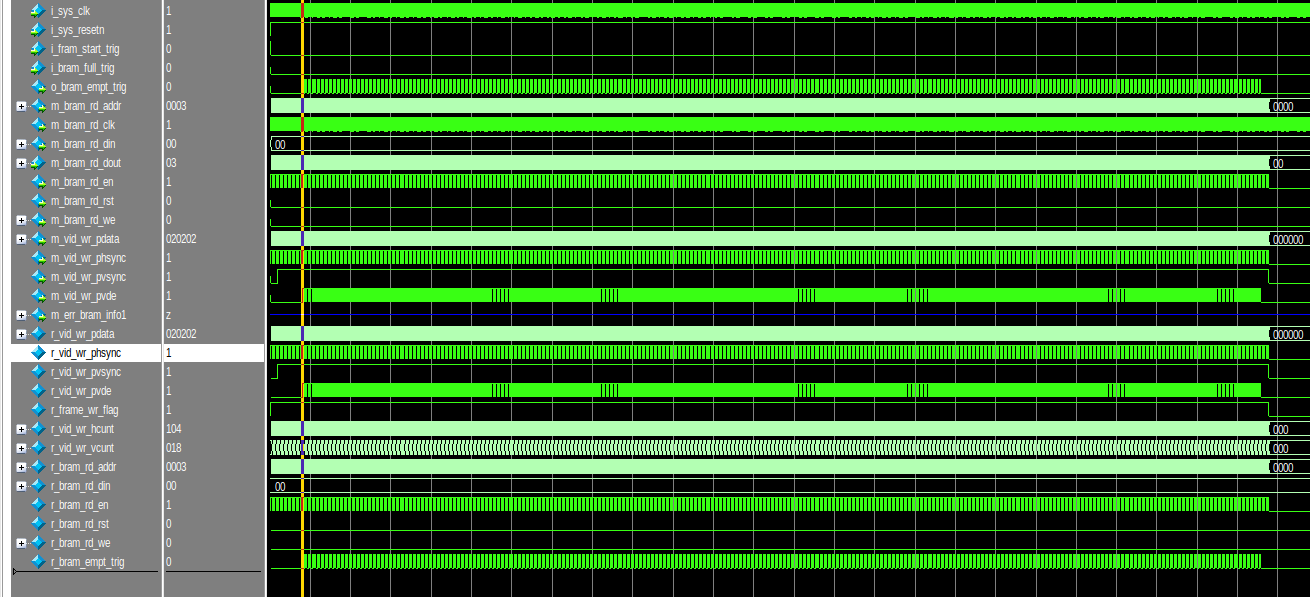

/* end verilog

sim

- BRAM read delay

- video horizontal data

- video vertical data

*/

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/17978302,文中资源链接如下:

1. GITHUB开源仓库