Entity: cyc_to_led

- File: cyc_to_led.v

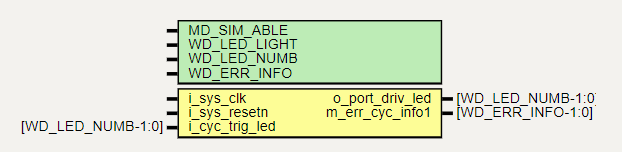

Diagram

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| MD_SIM_ABLE | 0 | sim mode enable | |

| WD_LED_LIGHT | 27 | LED light span wdith | |

| WD_LED_NUMB | 3 | led width to true LED | |

| WD_ERR_INFO | 4 | error info note |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_sys_clk | input | system signals | |

| i_sys_resetn | input | ||

| i_cyc_trig_led | input | [WD_LED_NUMB-1:0] | trig signal |

| o_port_driv_led | output | [WD_LED_NUMB-1:0] | led port |

| m_err_cyc_info1 | output | [WD_ERR_INFO-1:0] | error info feedback |

Signals

| Name | Type | Description |

|---|---|---|

| r_cyc_trig_led | reg [WD_LED_NUMB-1:0] | cycle signal temp one clock |

| w_cyc_trig_led_pos | wire [WD_LED_NUMB-1:0] | detect cycle signal pos edge |

| r_led_light_cnt | reg [WD_LED_LIGHT-1:0] | counter for every LED driver |

Processes

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

`timescale 1ns / 1ps

/*

Src Code

*/

// *******************************************************************************

// Company: Fpga Publish

// Engineer: FP

//

// Create Date: 2024/01/09 22:54:18

// Design Name:

// Module Name: cyc_to_led

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

// Revision: 0.01

// Revision 0.01 - File Created

// Additional Comments:

//

// *******************************************************************************

module cyc_to_led #(

//mode

parameter MD_SIM_ABLE = 0, //!sim mode enable

//number

parameter WD_LED_LIGHT = 27, //!LED light span wdith

parameter WD_LED_NUMB = 3, //!led width to true LED

//width

parameter WD_ERR_INFO = 4 //!error info note

)(

//!system signals

input i_sys_clk ,

input i_sys_resetn,

//!trig signal

input [WD_LED_NUMB-1:0] i_cyc_trig_led,

//!led port

output [WD_LED_NUMB-1:0] o_port_driv_led,

//!error info feedback

output [WD_ERR_INFO-1:0] m_err_cyc_info1

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

// src signal solve

reg [WD_LED_NUMB-1:0] r_cyc_trig_led; //!cycle signal temp one clock

wire [WD_LED_NUMB-1:0] w_cyc_trig_led_pos;//!detect cycle signal pos edge

// ----------------------------------------------------------

// led cnt

reg [WD_LED_LIGHT-1:0] r_led_light_cnt [0:WD_LED_NUMB-1]; //!counter for every LED driver

//========================================================

//always and assign to drive logic and connect

// ----------------------------------------------------------

// src signal solve

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_cyc_trig_led <= 1'b0; //

end

else if(1) //

begin

r_cyc_trig_led <= i_cyc_trig_led; //

end

end

assign w_cyc_trig_led_pos = i_cyc_trig_led & (~r_cyc_trig_led);

// ----------------------------------------------------------

// led cnt

generate genvar i;

for(i = 0; i < WD_LED_NUMB; i = i + 1)

begin:FOR_WD_LED_NUMB

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(w_cyc_trig_led_pos[i]) //every trig will reset counter

begin

r_led_light_cnt[i] <= 1'b0; //

end

else if(r_led_light_cnt[i][WD_LED_LIGHT-1])

begin

r_led_light_cnt[i] <= r_led_light_cnt[i];

end

else

begin

r_led_light_cnt[i] <= r_led_light_cnt[i] + 1'b1;

end

end

assign o_port_driv_led[i] = r_led_light_cnt[i][WD_LED_LIGHT-1];

end

endgenerate

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

/*

补充说明(UTF-8)

- 基于LED监测周期信号

- 主要用于监测周期在ms级别的中断等物理信号

- 本模块暂时进行到源码设计阶段

*/

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/17955569,文中资源链接如下:

1. GITHUB开源仓库