verilog自动对齐脚本

简介

- vscode中的verilog-utils可以自动例化

- 但是没有保留注释

- 导致注释丢失比较严重

- 这个为后期的维护带来了巨大的工作量

- 基于此,使用TCL脚本完成同样的工作

bat脚本启动

- 文件 verilog_utils_expand.bat

rem get script path

set pns_own=%0

set p_own=%~dp0%

set pns_own_tcl="%p_own%verilog_utils_expand.tcl"

cd %p_own%

rem call tcl

call %SF_P_WISH% %pns_own_tcl%

rem pause

- 其中SF_P_WISH时tcl wish的安装路径下的exe

TCL/TK下载

TCL/TK脚本例化

# get script own path

variable v_own [file normalize [info script]]

set pns_own [file nativename $v_own]

set p_own [file dirname $pns_own]

set n_own [file tail [file rootname $pns_own]]

set s_own [file extension $pns_own]

# get param

# set pns_param "$p_own/param.ini"

# set f_path [open $pns_param r]

# set v_param [read $f_path]

# close $f_path

set v_param [clipboard get]

puts $v_param

# regsub module

set v_param2 ""

set l_module_name [regexp -all -inline {[\n]*[\s]*module[\s]*([\w]+)[\s]*\#[\s]*\(} $v_param]

if {[llength $l_module_name] == 0} {

puts {no parameter like module xx #() }

set l_module_name [regexp -all -inline {[\n]*[\s]*module[\s]*([\w]+)[\s]*\(} $v_param]

if {[llength $l_module_name] == 0} {

puts {no parameter like module xx( }

} else {

set m_module [lindex $l_module_name 1]

regsub {[\n]*[\s]*module[\s]+} $v_param "" v_param1

regsub {[\s]*\([\s]*} $v_param1 "u_$m_module\(\n " v_param2

}

} else {

set m_module [lindex $l_module_name 1]

regsub {[\n]*[ ]*module[ ]+} $v_param "" v_param1

regsub {[\n]*[ ]*\)[\s]*\([ ]*} $v_param1 "\n\)u_$m_module\( " v_param2

}

# regsub param

regsub -all -line {[ ]*parameter[ ]*([\w]+)[ ]*\=[ ]*[\w\']+[ ]*\,} $v_param2 " \.\\1\(\\1\)," v_param2

regsub -all -line {[ ]*parameter[ ]*([\w]+)[ ]*\=[ ]*[\w\']+[ ]*} $v_param2 " \.\\1\(\\1\)" v_param2

regsub -all -line {[ ]*\[[\w\+\-\*\/]+:[\w\+\-\*\/]+\][ ]*} $v_param2 " " v_param3

regsub -all -line {[ ]*input[ ]*([\w]+)[ ]*} $v_param3 " \.\\1\(\\1\)" v_param3

regsub -all -line {[ ]*output[ ]*([\w]+)[ ]*} $v_param3 " \.\\1\(\\1\)" v_param3

regsub -all -line {[ ]*inout[ ]*([\w]+)[ ]*} $v_param3 " \.\\1\(\\1\)" v_param3

puts $v_param3

# clip clear and write text

eval clipboard clear

clipboard append $v_param3

# destroy win

set i_id [after 10 {destroy .}]

vscode联动

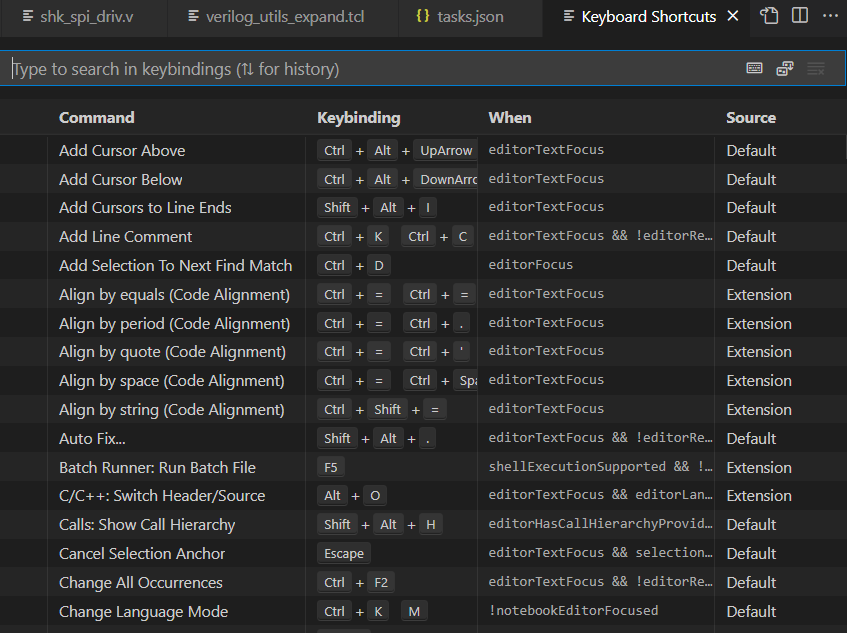

- 添加快捷键(注意快捷键不要冲突)

{

"key": "alt+m",

"command": "workbench.action.tasks.runTask",

"args": "verilog_utils"

},

- 添加任务(注意路径)

"tasks": [

{

"label": "verilog_utils",

"type": "shell",

"command": "D:/f1_library2/b0_script_app/c2_vscode_plug/verilog_utils_expand.bat",

"args": [],

"presentation": {

"echo": false,

"reveal": "never",

"focus": false,

"panel": "shared",

"showReuseMessage": false,

"clear": false

},

"problemMatcher": []

}

]

- 检查效果

- ctrl + C 复制module

- alt + m 转化为例化端口

- ctrl + v 粘贴到制定的位置

- 理论上后两步可以合并,但是没有找到方法

小结

-

可以完成verilog的例化

-

可以保留注释

-

使用时使用vscode调用bat脚本即可

-

能满足需求

-

缺陷:会把注释的端口释放,暂未找到解决方法

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/17304866.html,文中资源链接如下:

1. GITHUB开源仓库

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 单元测试从入门到精通

· 上周热点回顾(3.3-3.9)

· winform 绘制太阳,地球,月球 运作规律