verilog之readmemb

1、基本作用

用于读取存储器的值的系统函数。这里首先要知道什么是存储器。在verilog中,有一些比较大的数据是需要存储的,一般需要使用存储器,语法结构类似二维数组。

reg [7:0] mem[256:1];

initial mem[1]=8'hff;

这里的mem就是一个存储器。前面的是位宽,后面的是地址。这个和存储器的结构是十分相似的。对于这类变量,一般用于仿真存储设备。readmemb可以读取存储器,显示为二进制。readmemh可以显示为16进制。通过这两个函数可以将存储器的值显示。

2、实际例子

module readmemb; reg [7:0] memh[1:256]; reg memb[1:256]; initial memb[128]=0; initial memh[254]=8'hff; initial $readmemb("memb.data",memb,128,1); initial $readmemh("memh.data",memh,128,1); endmodule

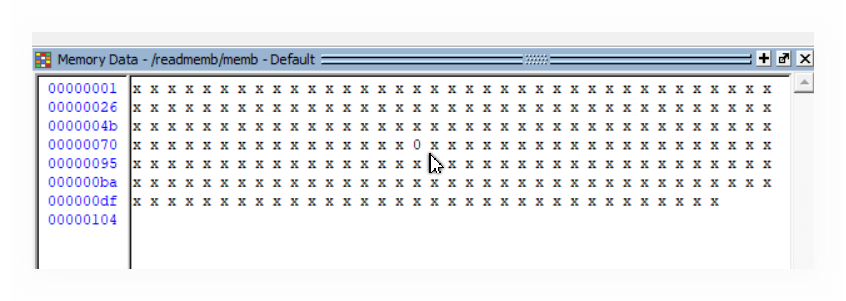

memb:

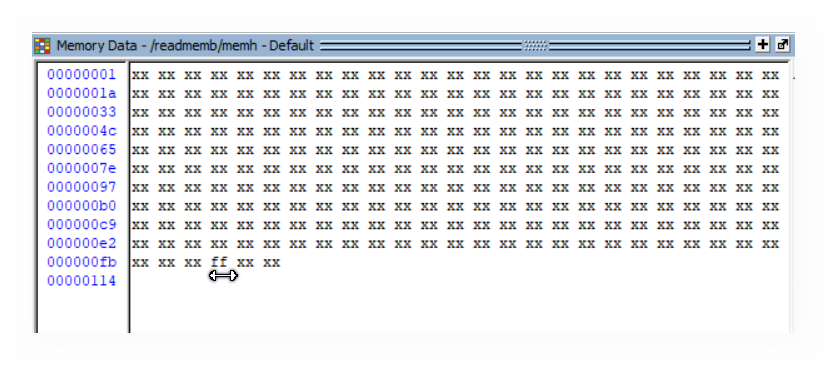

memh:

可以看到存储器的赋值结果。

3、总结

当需要使用存储器来仿真时,readmemb(h)是一个重要的手段来观测结果的变化。

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/13382806.html,文中资源链接如下:

1. GITHUB开源仓库