FPGA之PLD的简单设计

1、实验原理

PLD是可编程逻辑器件的简称,是FPGA的前身(FPGA是在PLD的基础上发展出来的)。从PLD设计可以感受早期可编程逻辑器件的特点,了解FPGA在器件层的原理特点。本次实验采用WinCupl软件编辑一个PLD的配置文件,使用proteus进行仿真。

2、实验操作

(1)设计PLD配置文件

在file中新建工程,设置两个输入和一个输出。

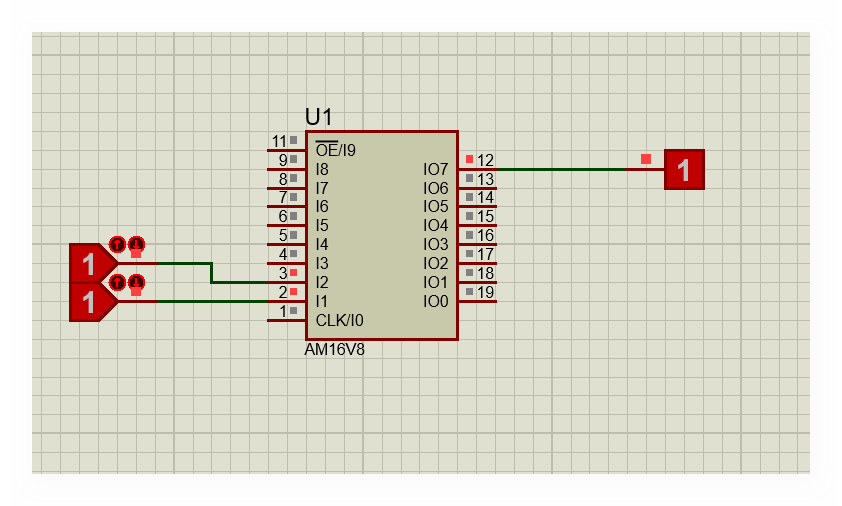

Name Demo ; PartNo 00 ; Date 2020/7/12 ; Revision 01 ; Designer Engineer ; Company ttt ; Assembly None ; Location ; Device G16V8 ; /* *************** INPUT PINS *********************/ PIN 2 = a ; /* */ PIN 3 = b ; /* */ /* *************** OUTPUT PINS *********************/ PIN 12 = c ; /* */ c=a&b;

配置与门,其中2、3分别与PLD器件的管脚编号对应。12与输出管脚编号对应。

(2)快速仿真

在proteus中添加器件。由于只有一个与门,所以可以直接用逻辑输入输出用于调试。调用配置文件就是在器件的属性中有使用外部文件的窗口。仿真结果就是一个与门的结果。

3、实验结果

从这个简易的流程中可以看到设计的方法。由于只是一个与门,所以设计的方法和FPGA很类似。不过,PLD配置使用的语言不是verilog,目前也没有了解具体的名称。&、#、!、$分别是与 或 非 异或四种逻辑关系。从端口可以看到有时钟信号,具体的编辑方法还没有找到。有兴趣的可以找一下相关的资料。

这里记录一下操作的流程,不涉及具体的语法。

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/13289742.html,文中资源链接如下:

1. GITHUB开源仓库

浙公网安备 33010602011771号

浙公网安备 33010602011771号