基于proteus的4026的二分频计数

1、芯片原理

4026还是一个CMOS芯片,是直接输出段码的计数器。显然,这个芯片的作用就是和七段数码管配合,直接将计数结果显示在数码管上。这里只是用于分频,只需要一个端口的有效值即可。使能信号方面:INH、MR为低电平时电路导通,DEI为高电平时电路导通。可以得到INH和MR为高电平复位信号,DEI为高电平使能信号。至于具体的设计原理,这里就没有深究。

2、参考电路

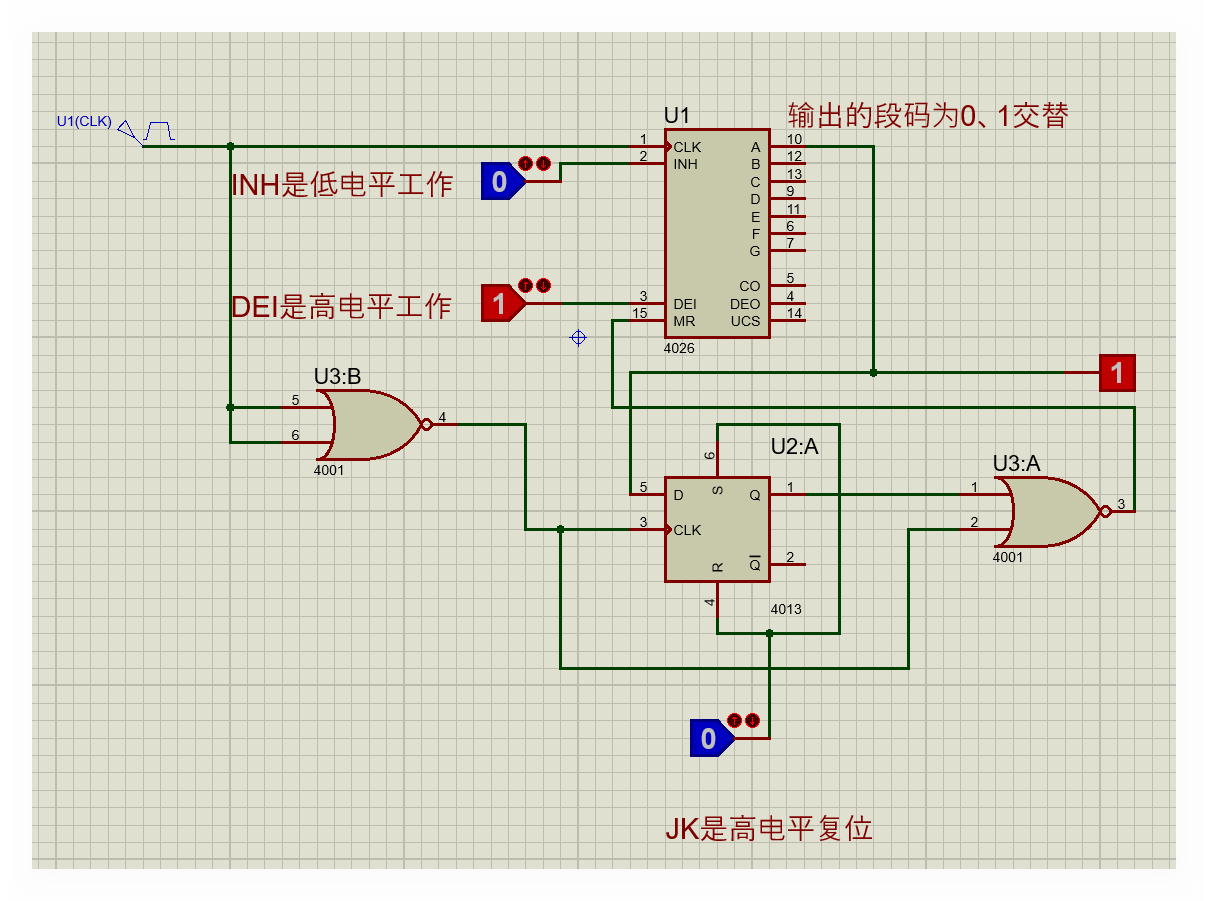

电路原理就是取一个计数为0和1之间有变化的段码做输出,将时钟信号经过D触发器的逻辑判断得到复位信号连接到MR上。

3、设计原理

这个设计的主要工作是得到4026的复位信号。可以看到处理方法是先对时钟取反,构成错位时钟。这个可以保证复位信号可以提前到达。D触发器是对输出进行一次判断,将结果反馈到复位信号。

4、总结

计数器基本上都可以用于分频。在verilog中,计数器都是通过对一个循环信号的判断实现计数,利用计数来实现信号的反转就是分频。

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/13236329.html,文中资源链接如下:

1. GITHUB开源仓库

浙公网安备 33010602011771号

浙公网安备 33010602011771号