PS-AXI-GPIO-流水灯设计

1、实验目的

在了解了AXI协议的基本内容后,通过已经设计好的AXI的IP核来了解实际设计中AXI的工作原理和设计原理是必要的。这个实验以前实际上按照教程做过,但是没有过多地注意AXI总线的作用和地位,对于AXI协议还是当作黑盒子处理。但是,如果想要将自己的FPGA设计挂到AXI上,了解AXI的具体原理是必要的。这次的回顾除了对一些操作做出具体的解析外,主要任务就是了解IP核的AXI的原理,为下一步基于AXI4打包FL的IP核打好基础。

2、实验操作

(1)构建硬件平台

从目标看,依次添加PS ,AXI-GPIO两个IP核,按照常用开发板设计好,使用默认的自动补齐和连线。这个硬件平台就搭建完成。

配置来看,led需要四个输出,所以AXI-GPIO需要一个四位位宽的输出GPIO。

然后就可以进入引脚设置和生成bit流。

至于对具体的结构会在后面的实验分析中进行,这里只是大致的看一下操作。详细的操作在下面的博文中有:GPIO实验

(2)实现软件设计

这部分需要补充的就是如何使用AXI总线调用外设。一般来说官方对于ARM内核使用的AXI上的IP核上都有比较全面的库。通过这些封装好的库可以有效地使用AXI协议。这部分只需要考虑如何使用即可。

假设已经知道如何导入硬件和初始化设置,这里主要针对一些简单的ARM功能进行编程,方便调试硬件。

【1】对于一个空的工程而言,加入主函数main是第一步。

【2】使用系统函数是基本的操作。如果熟悉的人当然可以直接加入头文件和调用系统函数,完全没压力。但是对于初学者来说,面对大量的可用资源往往不知从何下手。这里提供一个简单的方法。

先看一下vitis的ARM处理器的操作系统的基本框架:

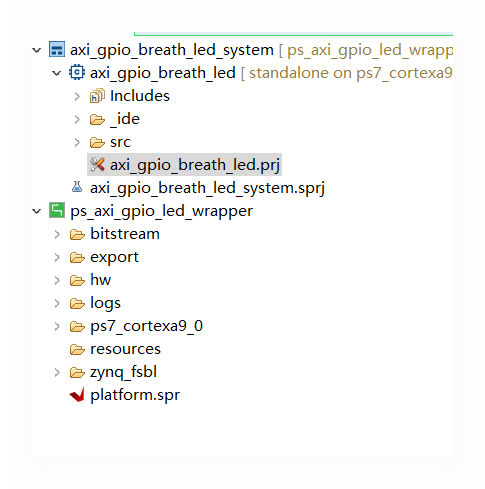

这是vitis创建工程的目录结构。上面的system,也就是操作系统的文件。下面的wrapper则是硬件资源的初始化文件。感觉这两个的关系类似BOOT和WINDOWS的关系。至于文件内容,如果只是想基于ARM内核做开发的话,可以忽略。但是需要了解大致的分布,方便寻找资源来设计。一开始vitis打开了rsc文件夹。这个文件夹就是源文件(也就是用户文件)放置的地方。在这个地方创建一个包含main的主函数,就启动了这个ARM内核。

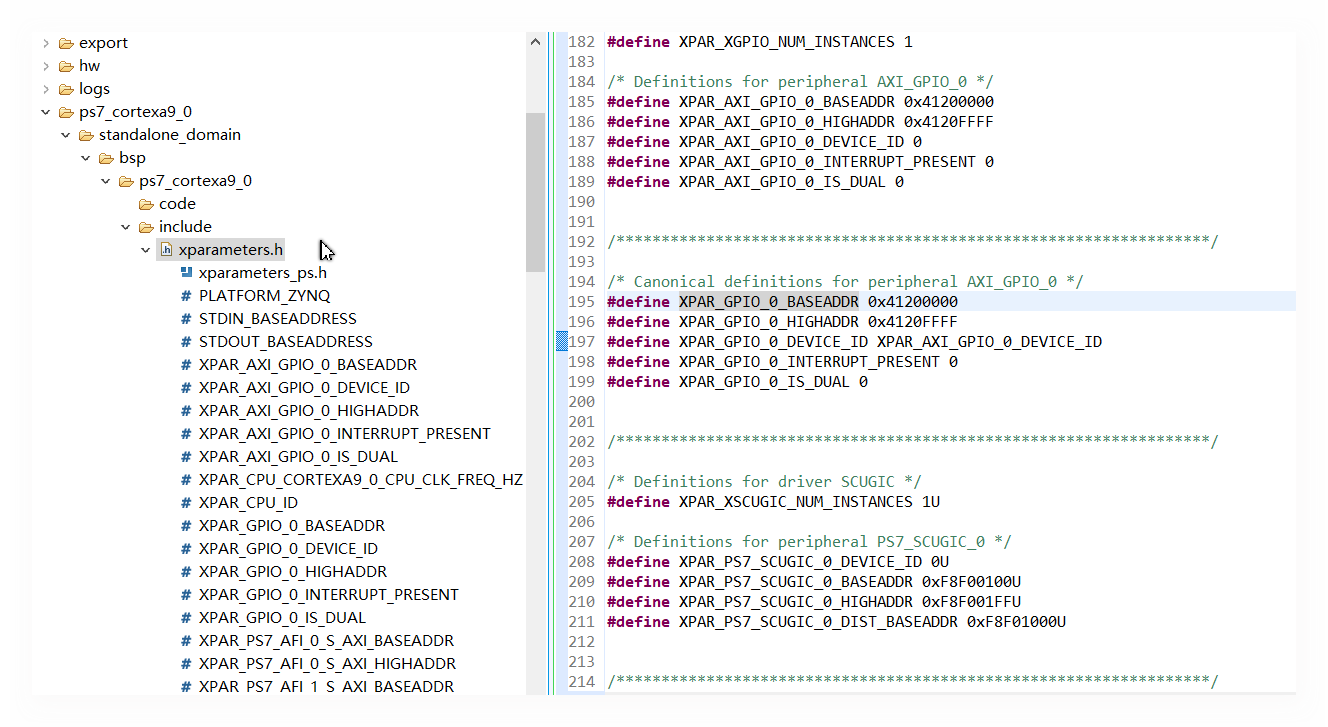

【3】面对空无一物的主文件,首先要找的就是需要定一个硬件的地址方便操作。这里的地址有一个主地址和一个从地址。主地址可以在硬件设计时分配,这里是0x4120,可以在address editor中找到并且修改。光有主地址还是不够的,这里还需要从地址。所有的地址在vitis中可以查看:

这就是地址配置文件的目录。注意这个目录是在wrapper下的,可以快速查找到对应设备的地址。

【4】基于地址的操作

这里使用的是官方IP核,一般是有用户手册来标明从地址对应的寄存器。对于自定义的基于AXI4的设计,这部分由设计者掌握。如何快速查找到官方IP的手册,在vivado中有快捷方式。实质上这里就是自动调用DOCNAV打开对应文件。

在BD视图中右击IP核,在列表中找IP document的具体文档,一般第一个就可以。

这里由于我使用DocNav是更新的,所以这里就不展示,以后再解决这个问题。

从地址0x0000就是数据位,默认为输出,这里也不用修改输出模式。所以可以直接基于地址操作寄存器。

【5】寄存器操作

这里就需要在wrapper中找rsc文件,从里面调用响应的函数即可。

3、实验结果

这里只是初步接触基于软件设计的调试,实验结果以后有时间做出来再看。这里首先掌握ARM内核调试的方法,为后面的操作打下基础。

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/13080741.html,文中资源链接如下:

1. GITHUB开源仓库

浙公网安备 33010602011771号

浙公网安备 33010602011771号