modelsim常用操作

1、库的定义(library)

modelsim是比较常用的仿真软件,主要用于数字电路的仿真,可以实现高效的前后仿真。仿真,就需要几个关键的元素:激励、设计模块、设计模块的约束平台。激励,就是电路的输入。设计模块就是设计好的电路。约束,就是电路实现的实际过程中所需的要求。(这也是后仿真的必须文件)。而库,就是包含这几个要素的集合。个人理解就是用于区分不同工作环境的文件夹。

2、工程的定义(project)

modelsim的project的界限并不明确,只要将某个测试模块的调用模块全部放在一个工程下即可。某个工程下的任意一个模块都可以仿真。可以理解为库下面的相应设计。这种设计架构和常见的电路设计软件不同。一般的设计是建立工程后加入器件和其他的资源库,而modelsim是在资源库下创建工程,这点适应一下就行。

3、创建工程

就是直接使用模块仿真,不加入其他约束。

由于没有其他的约束,可以直接使用默认的work来创建工程。

file:用于文件流的输入输出,创建保存新的文件都在这里实现

edit:编辑,用于某些操作的选择

view:视图,选择视觉效果

Compile:编译,就是更新工程文件

Simulate:仿真,就是启动激励文件,开始仿真

add:添加元素,向特定的窗口添加元素

library:设置库

bookmarks:批量处理

Window:新建窗口,一般不小心关掉某个显示窗口时可以在这里找。

help:访问一些帮助网站或者文档

这里是非常常见的Windows软件窗口,基本的操作可以和其他软件对比使用。

操作流程:

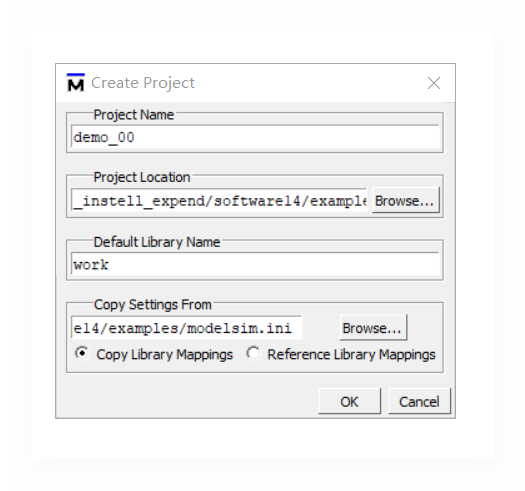

file》new》project

新建的工程,输入工程名,其他默认。

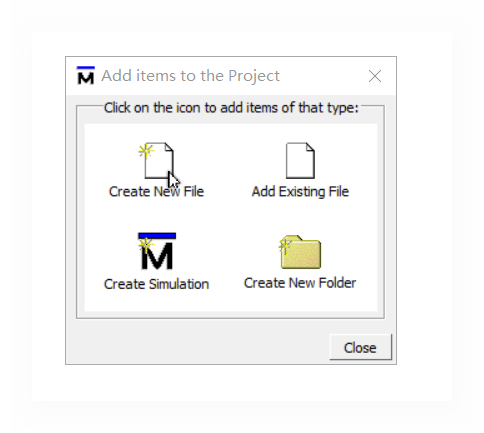

选择创建新文件即可

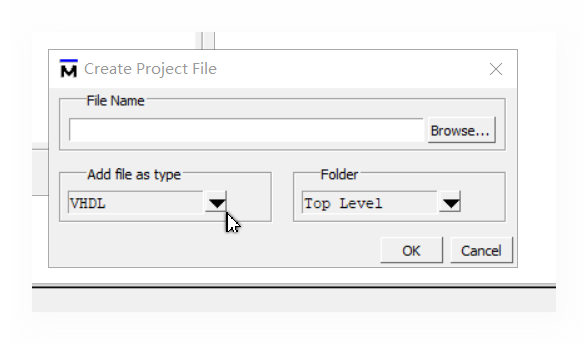

这里选择文件的语言verilog(根据需要设计),输入文件名

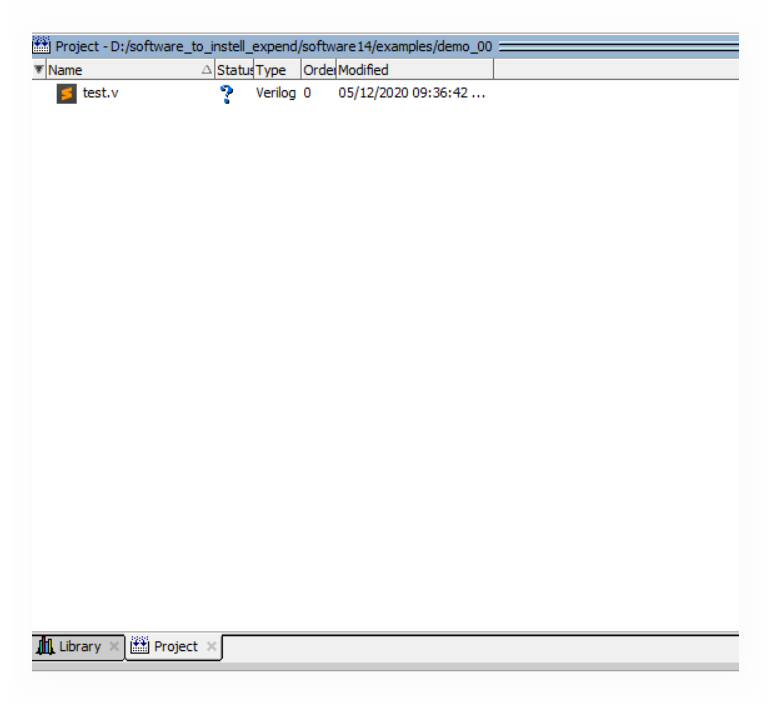

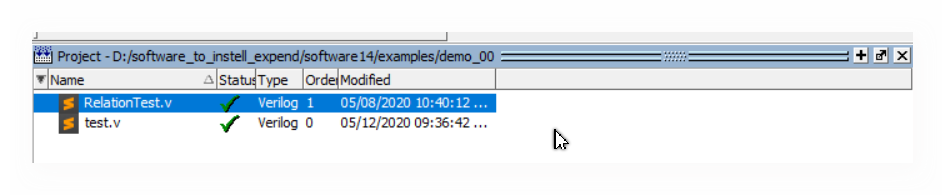

这个project面板包含当前工程的所有文件,(注意,modelsim只会打开一个工程,打开新的工程会关闭原来的工程)

新建的文件是在该工程目录下的未知文件,需要编译。

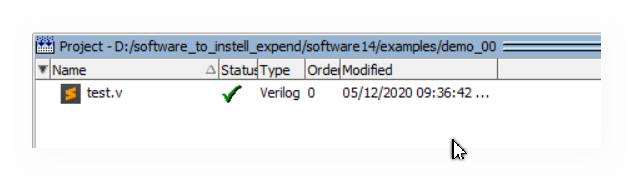

一般右击》compiled》compile all即可编译所有文件,其他选项也可以尝试一下。

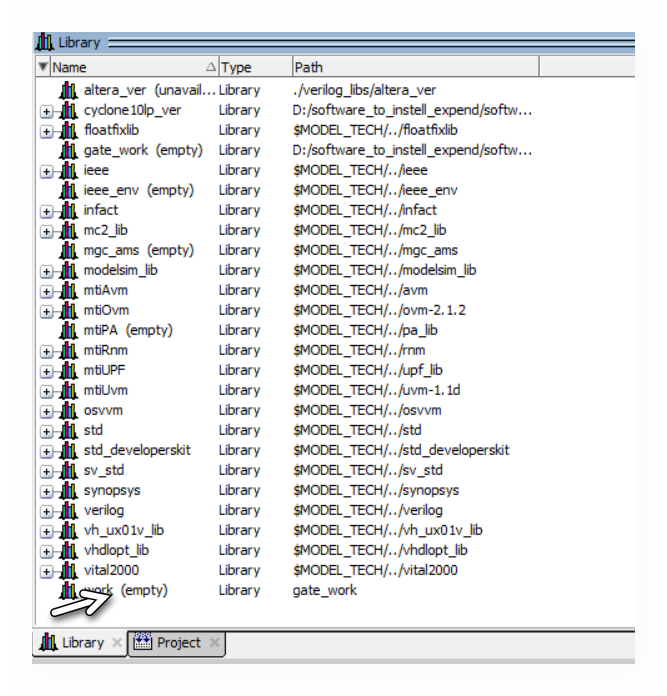

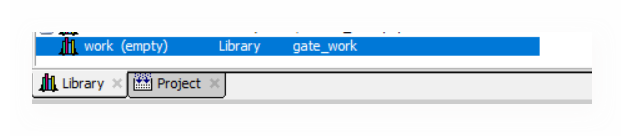

另外一个重要的面板是library,这里可以选择仿真文件开始仿真。这里也是modelsim最容易翻车的地方。

4、使用控制台仿真

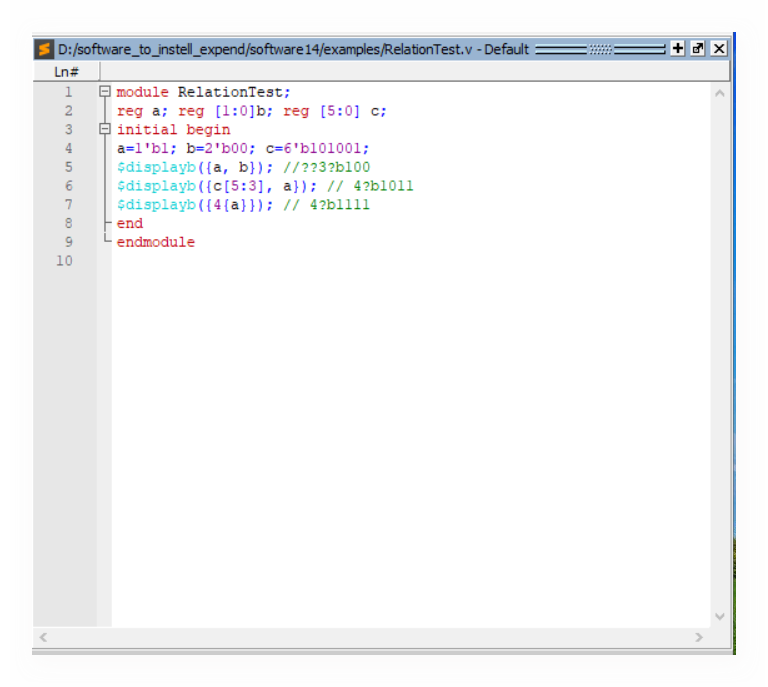

verilog代码:

这里是一个新的窗口,在project面板内部的文件上右击》edit就可以调出相应的代码编辑面板。代码很短,就不单独列出代码来,敲一下就好。注意verilog的代码名和模块名一致。

右击编译后如图所示。

一般来说,此时work库里会自动添加相应的仿真选项,但是这里没有出现,解决方法有两种:

1、右击》refresh或者右击》update

2、重启软件

当然,应当保证文件编译通过且文件模块名一致。

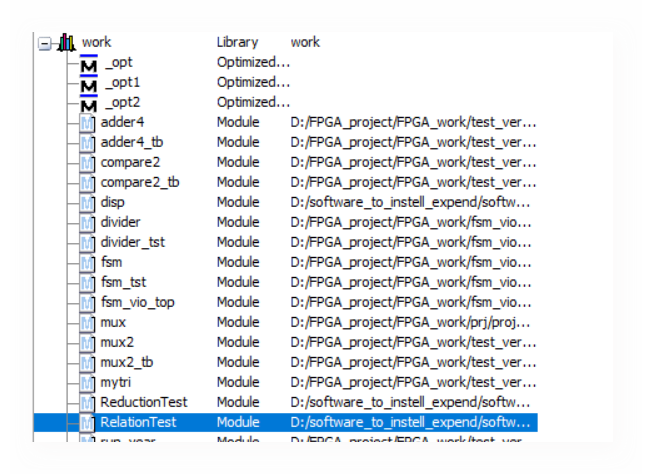

这是就会出现相应的module选项。

接下来:选中module》右击》simulate

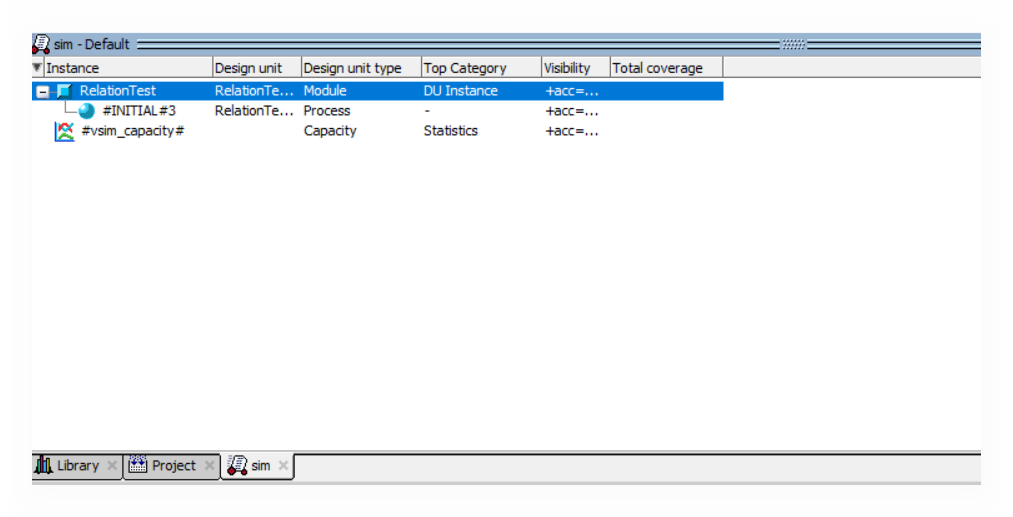

这里就出现了sim面板,也就是simulate的结果。

但是这里并不会直接出现控制面板的结果。

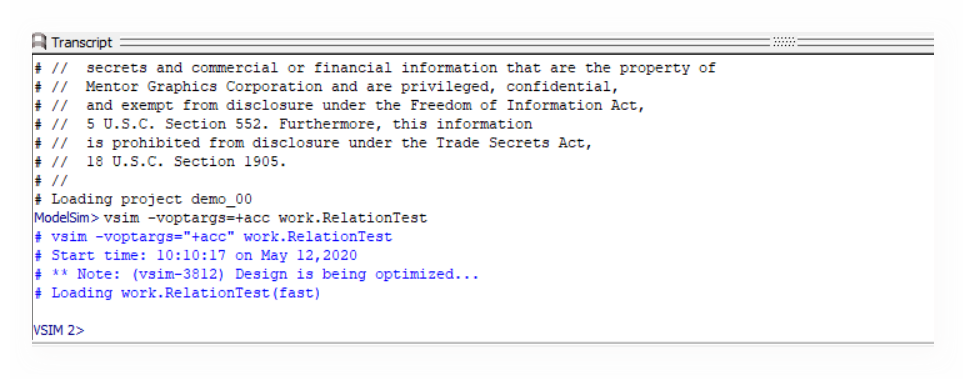

这个是控制面板Transcripe,用于输入指令和显示结果。

这里并没有display的结果。只有仿真的报告。但是前面的指令对象由sim变成了VSIM。

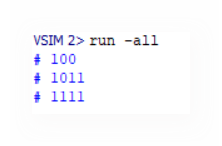

在控制面板输入run -all就可以得到。

5、波形仿真

这部分的内容有时间再做吧,前面的操作基本相同,就是在sim面板中添加信号到wave中即可(使用前面菜单栏中的add实现)。至于如何调整波形、展开波形和观察波形,可以自己探索。

======== ======\\ ======= -

|| || \\ // \\ /-\

|| || || // // \\

|| || // || // \\

====== ======= || === ========

|| || || \\ // \\

|| || \\ || // \\

|| || \\ // // \\

|| || ======= // \\

作者:绿叶落秋风,专注FPGA技术分析和分享,转载请注明原文链接:https://www.cnblogs.com/electricdream/p/12874573.html,文中资源链接如下:

1. GITHUB开源仓库

浙公网安备 33010602011771号

浙公网安备 33010602011771号