Xilinx 7 Series DDR3 存储接口学习

目录:

一、环境说明

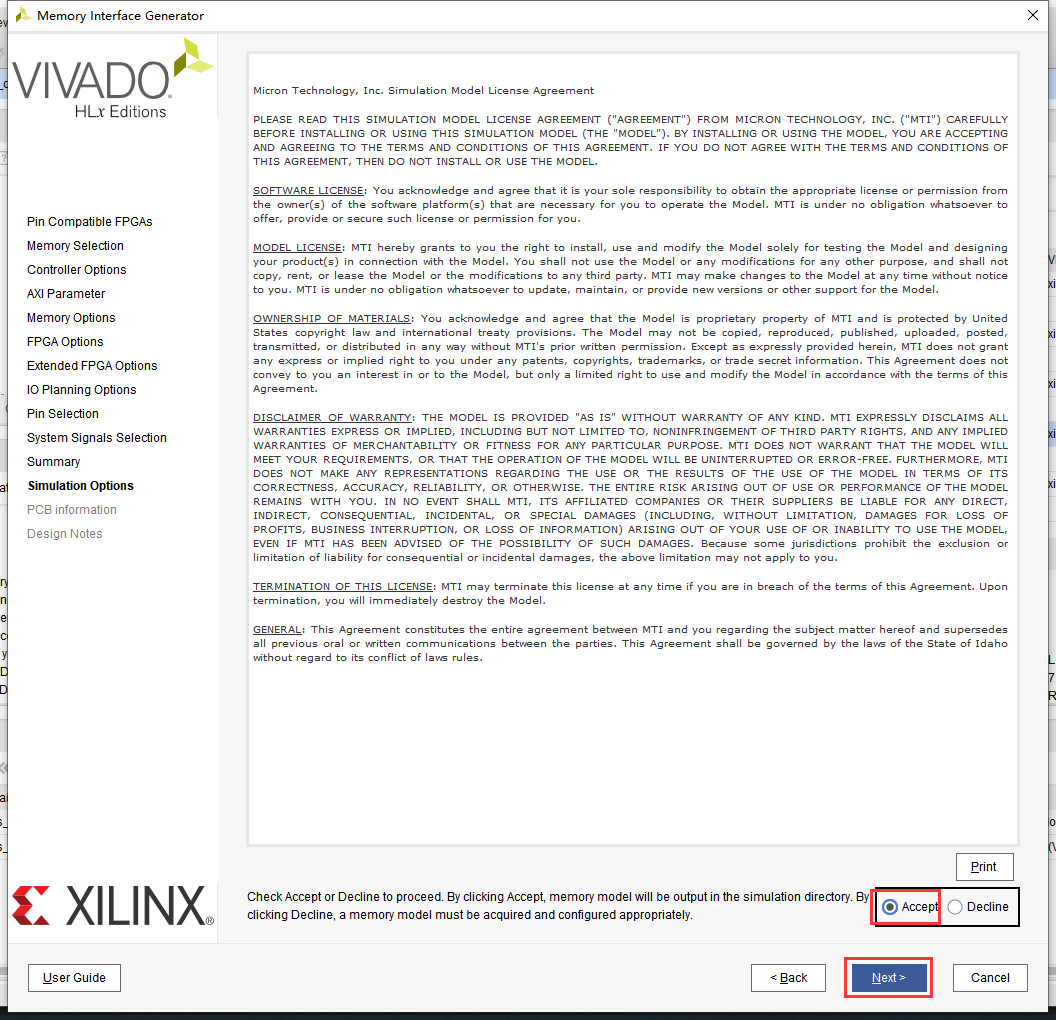

二、配置DDR3 IP核

备注:参考博文DDR3(1):IP核调取 - 咸鱼FPGA - 博客园 (cnblogs.com)

一、环境说明

- 软件:VIVADO 2018.3

- 硬件:ARTIX-7

- 前提:新建工程

二、配置DDR3 IP核

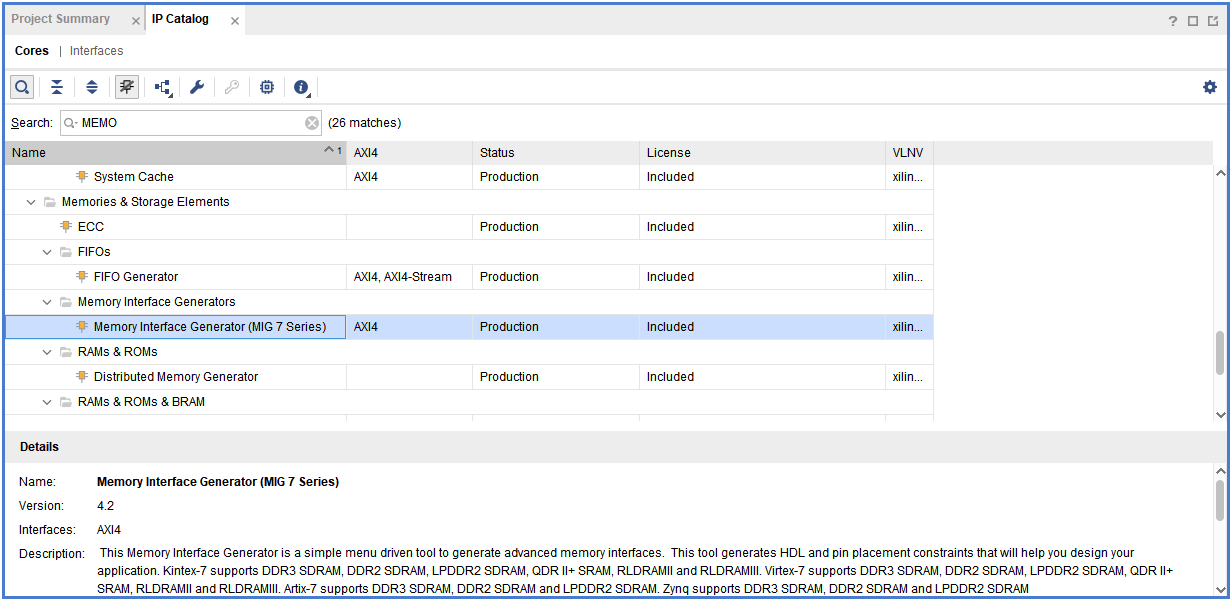

- 打开IP核:<IP Catalog> →<Memory Interface Generator(MIG 7 Series)>

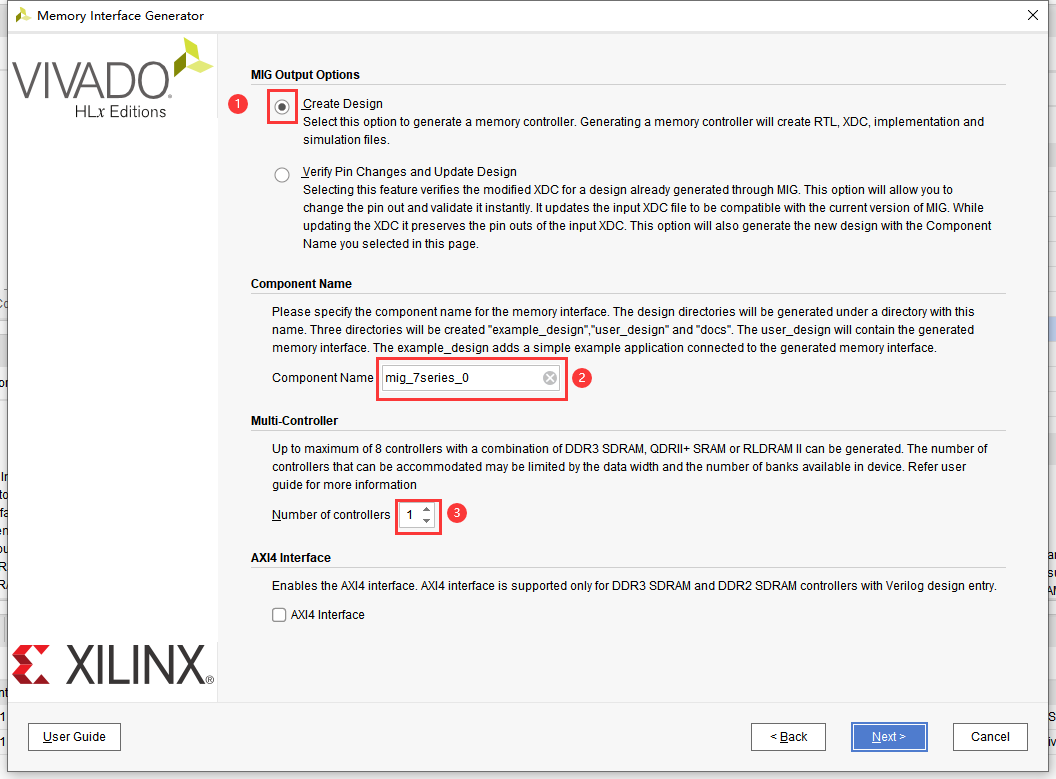

2. PAGE1:MIG Output Options (内存接口生成器 输出选项卡)

备注:AXI4接口:AMBA Advanced extensible Interface(AXI4)slave interfaces;高级可扩展接口从属接口;

DDR2和DDR3 SDRAM 设计支持内存映射 AXI4接口。AXI4接口只能通过verilog来实现,如果勾选了AXI4接口

那么你在进入IP之前就要选择verilog语言。不勾选则用户界面就是最初的接口;

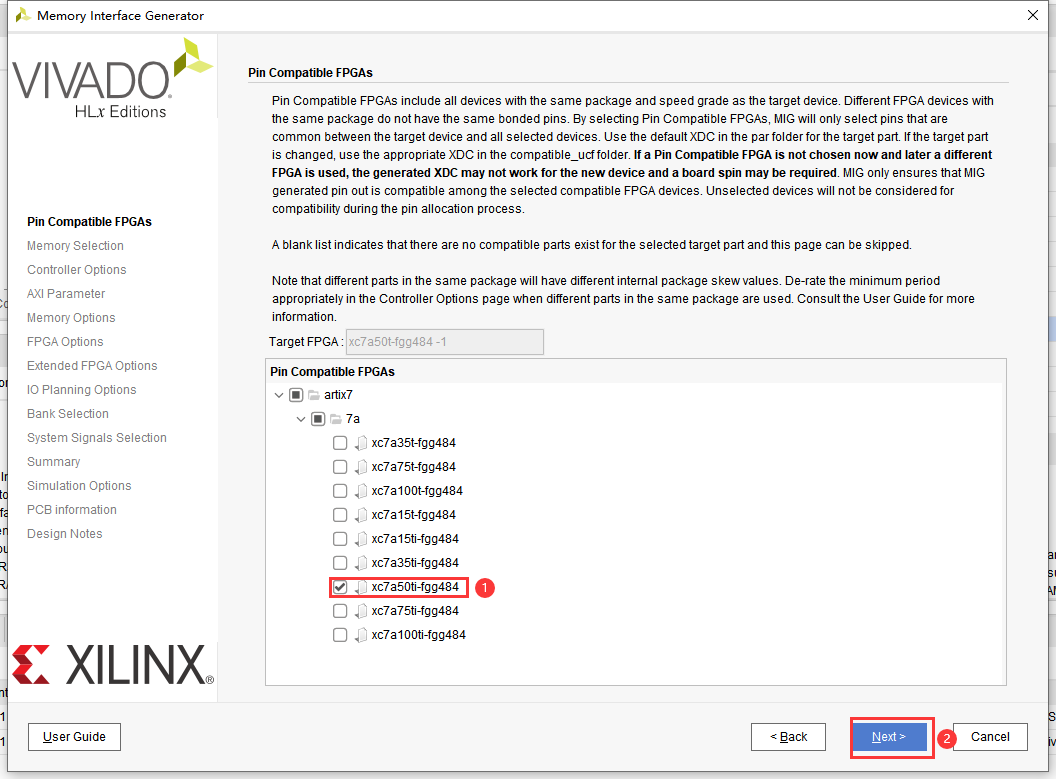

3. PAGE2:Pin Compatible FPGAs(引脚间可兼容的FPGA)

备注:选择可兼容(封装和速度等级相等的)FPGA,MIG将会生成目标设备和选择设备相同的引脚;

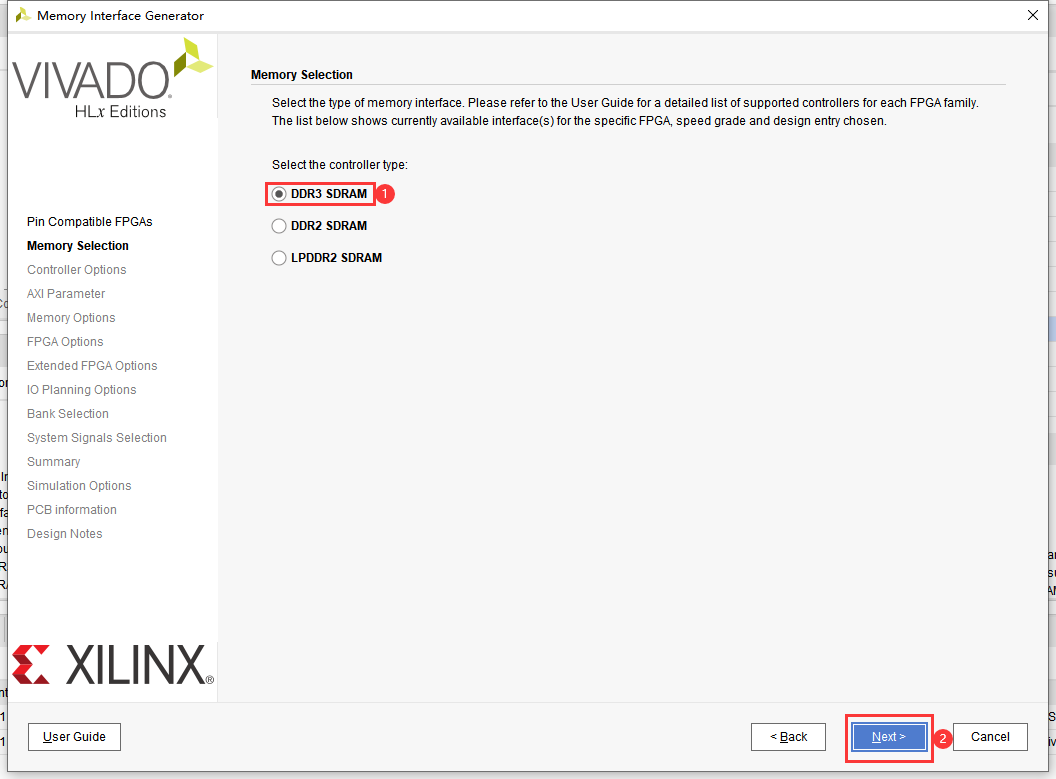

4. PAGE3:Memory Selection(存储接口选择 选项卡)

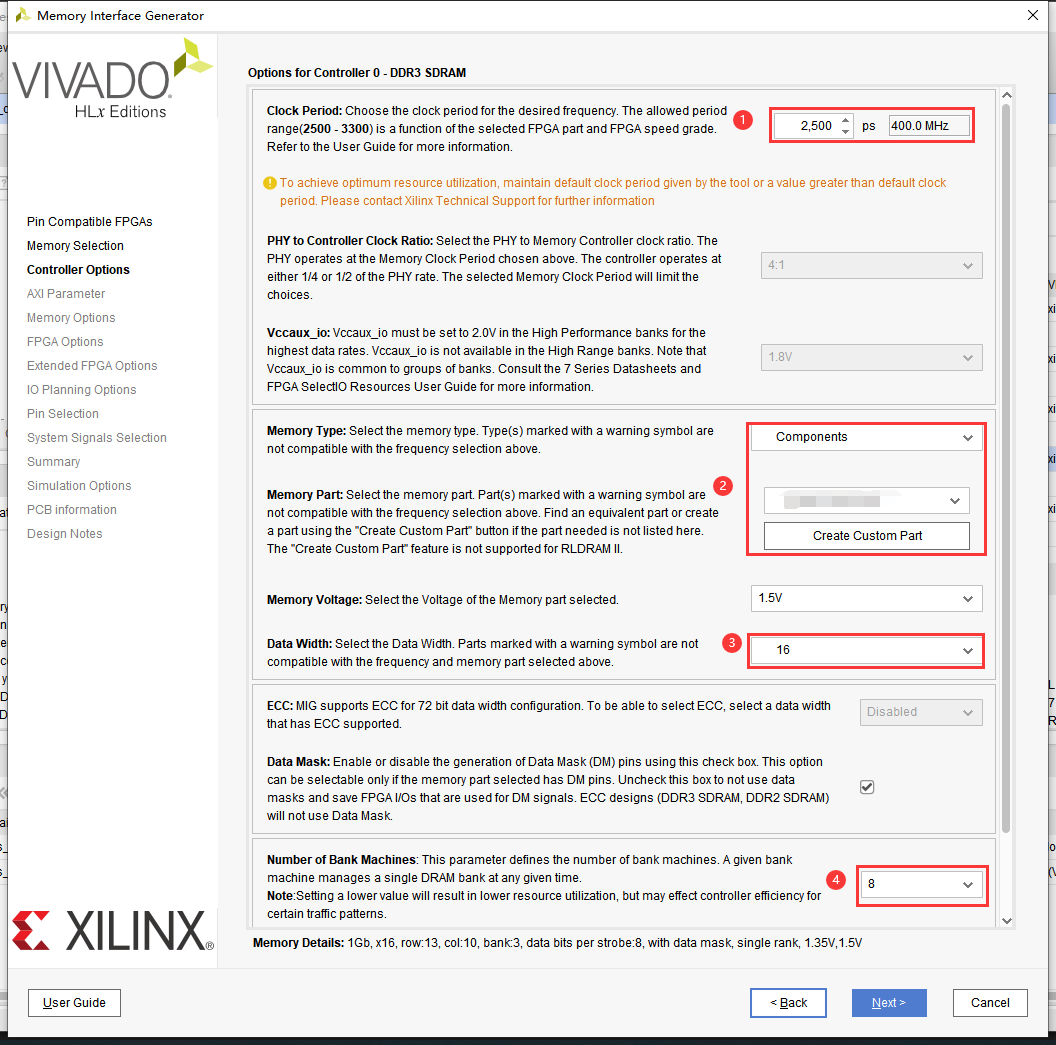

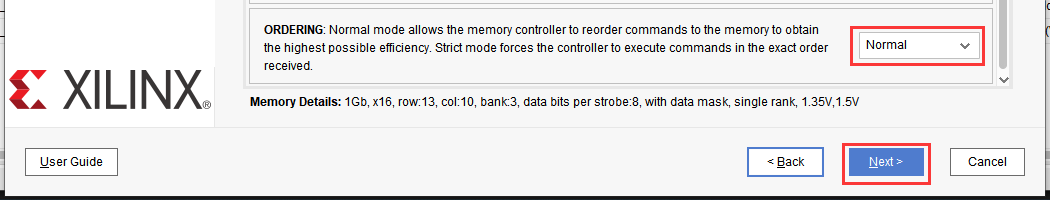

5. PAGE4:Controller Options(控制器选项卡)

- Clock Period :1Gb = 400M x 2 x 16bit ;(400M双沿=800M单沿)

- Memory Type:DDR3 SDRAM的内存类型有:内存颗粒(component)、内存条(RDIMMs、UDIMMs、SODIMMs)

- Memory Part :DDR3 SDRAM的内存型号,如果列表里没有,则需要自己创建新的组件。根据内存颗粒的数据手册填写(tcke、tfaw、tras......)

- Data Width:一片DDR3数据位宽为16bit,如果你是两片则为32bit

- Number of Bank Machines:一个bank mechine管理一个DDR3 bank

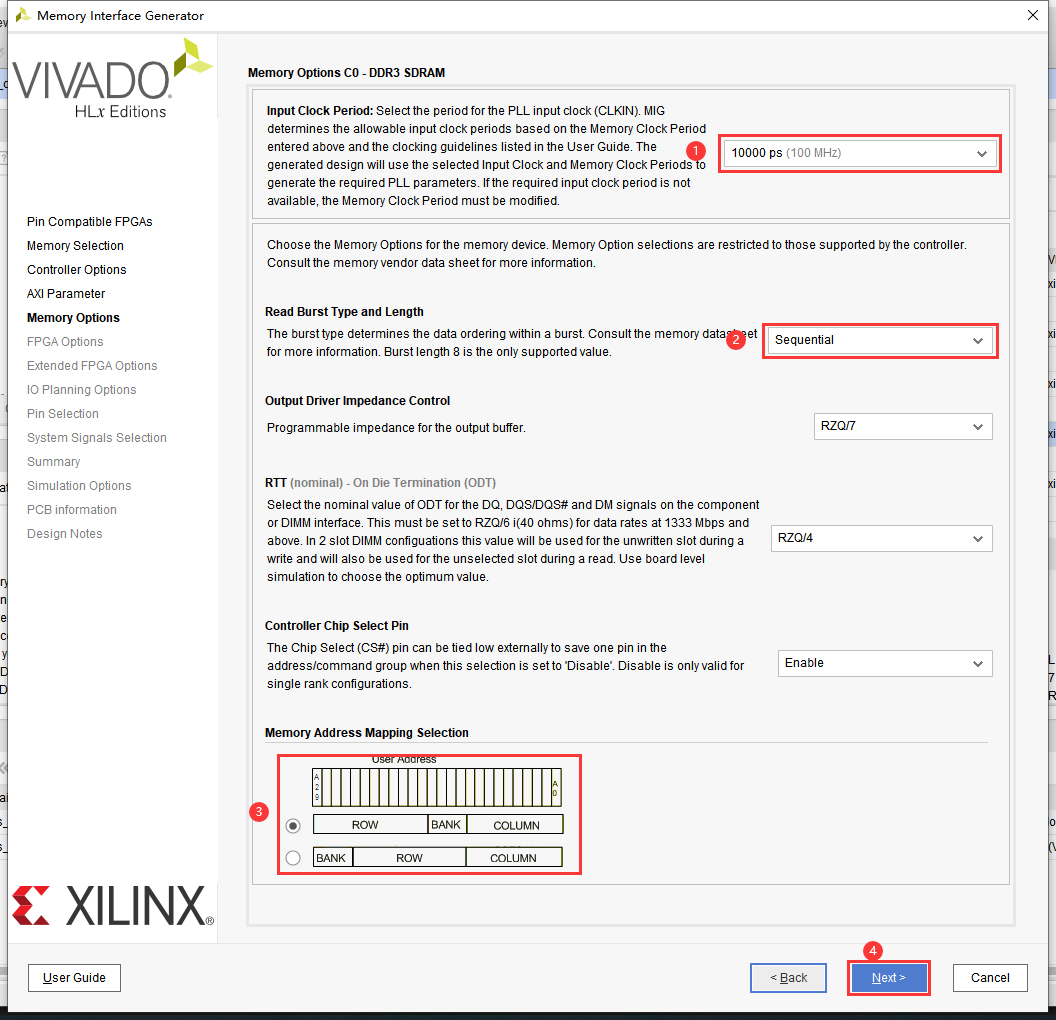

6. PAGE6:Memory Options(内存选项卡)

- Input Clock Period:之前选择的400M时钟,在4:1的PHY到用户接口时钟比例要求下,这里的时钟是400 x 1/4 = 100M;

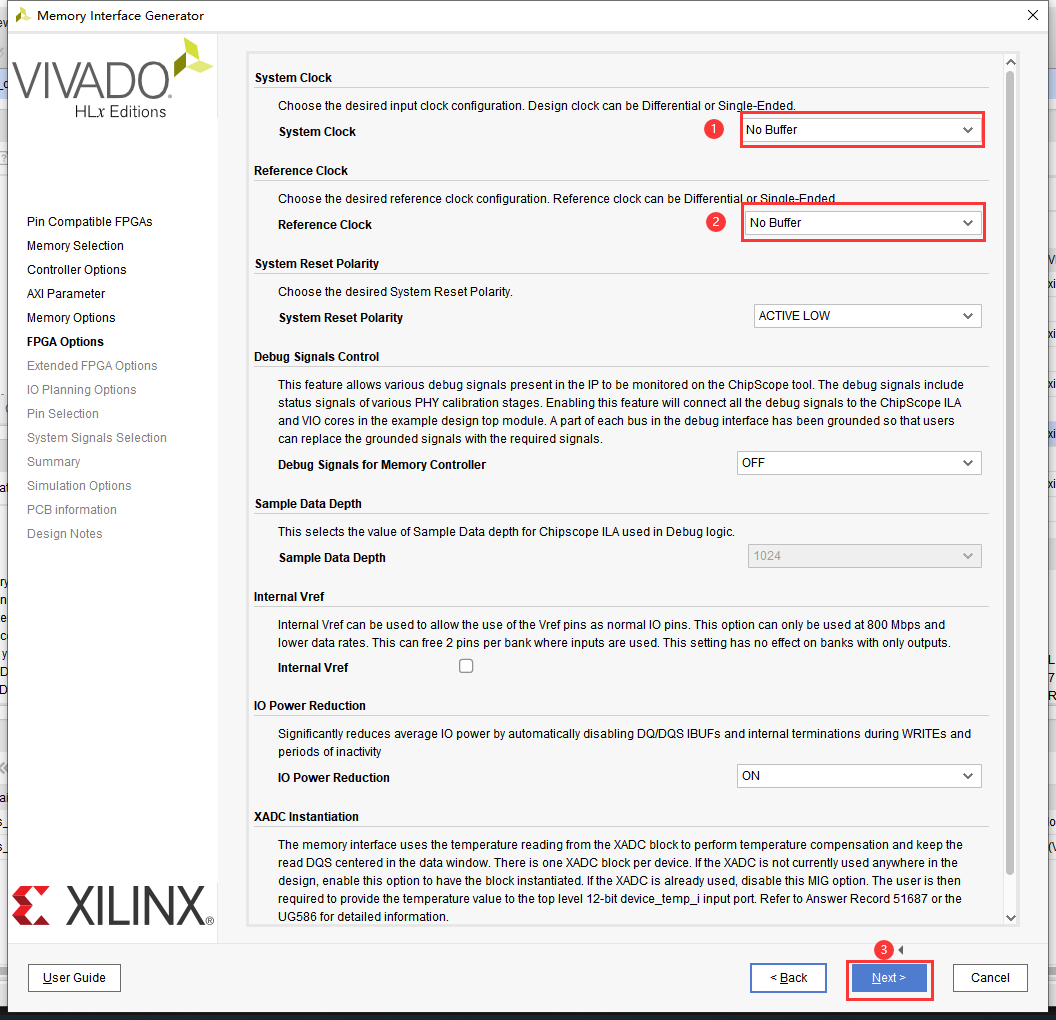

7.PAGE7:FPGA Options(FPGA选项卡)

- system clock、reference clock:选择有single-ended(单端)、differential-signal(差分)、no buffer(内部产生信号)

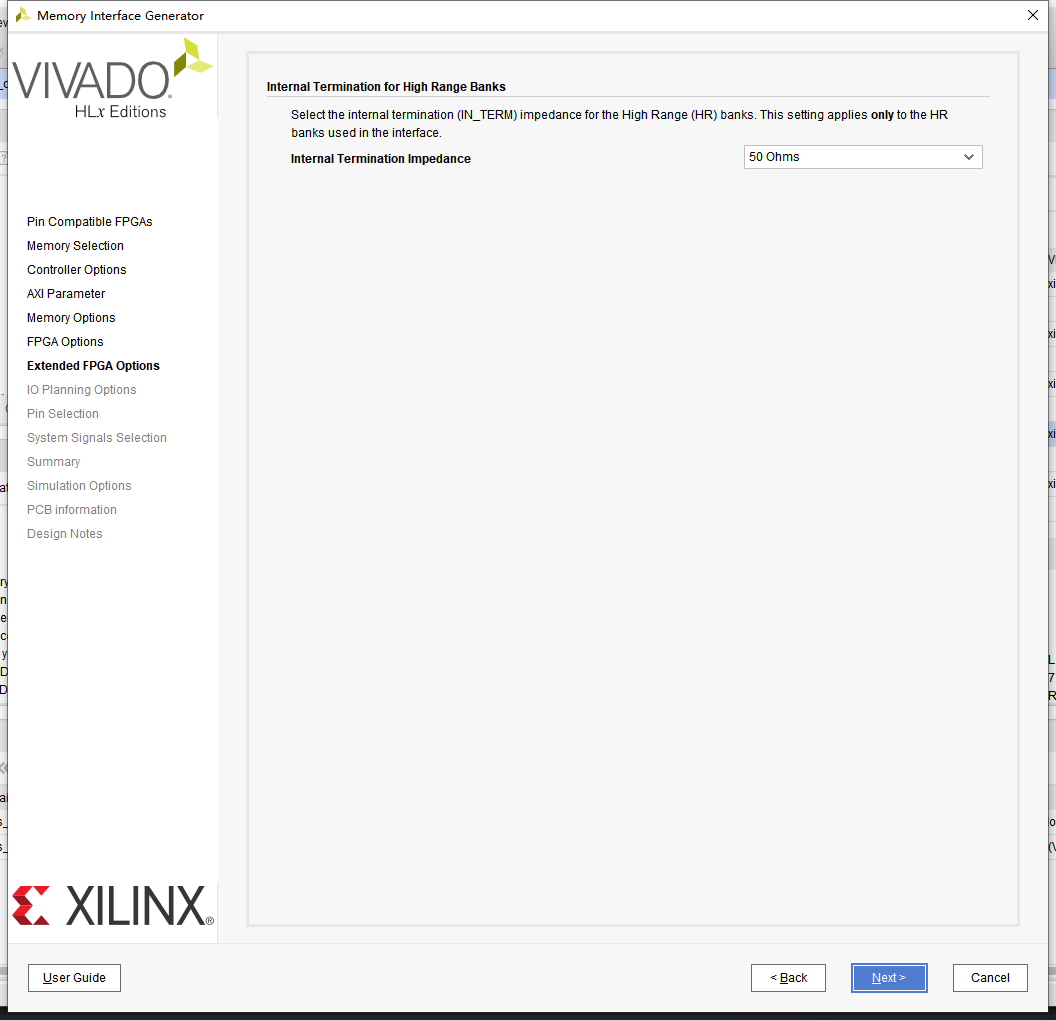

9.PAGE9:extended FPGA options(扩展选项卡)

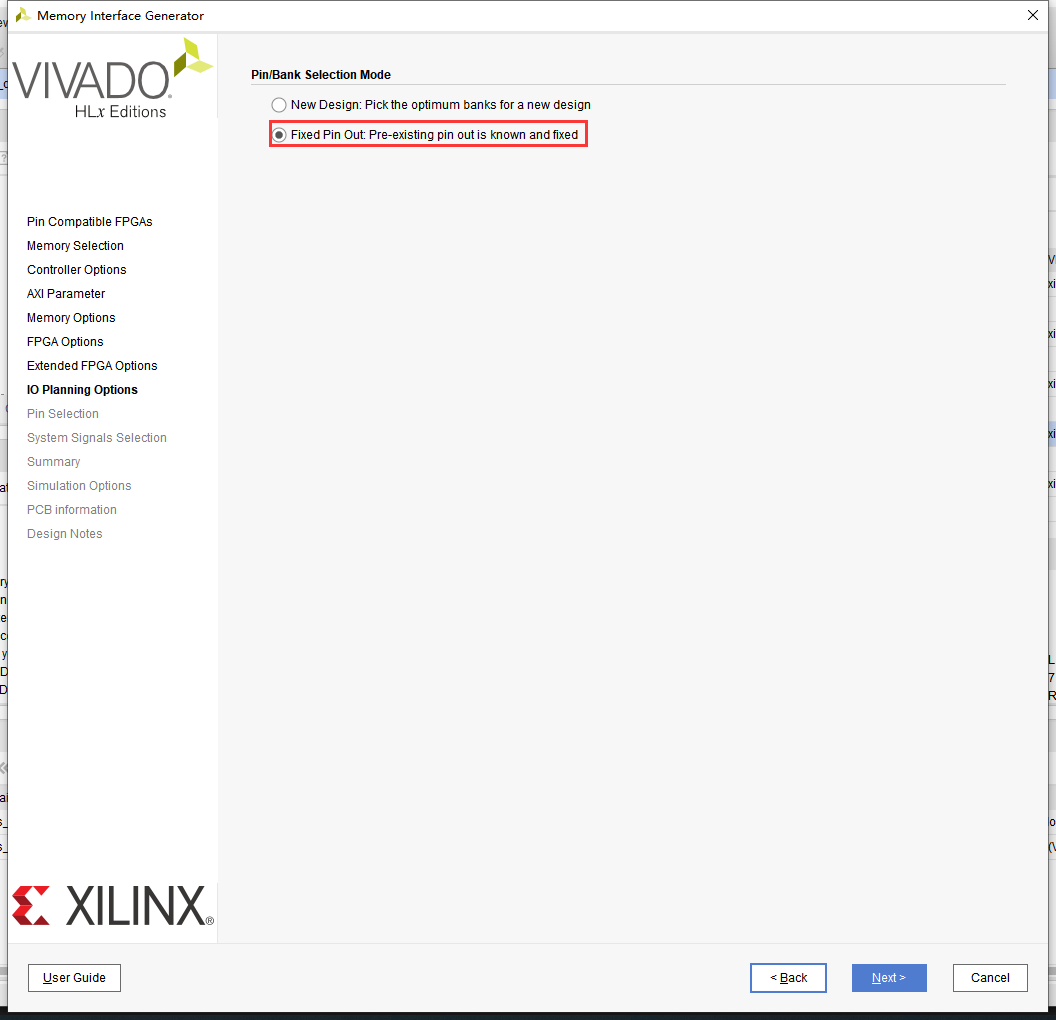

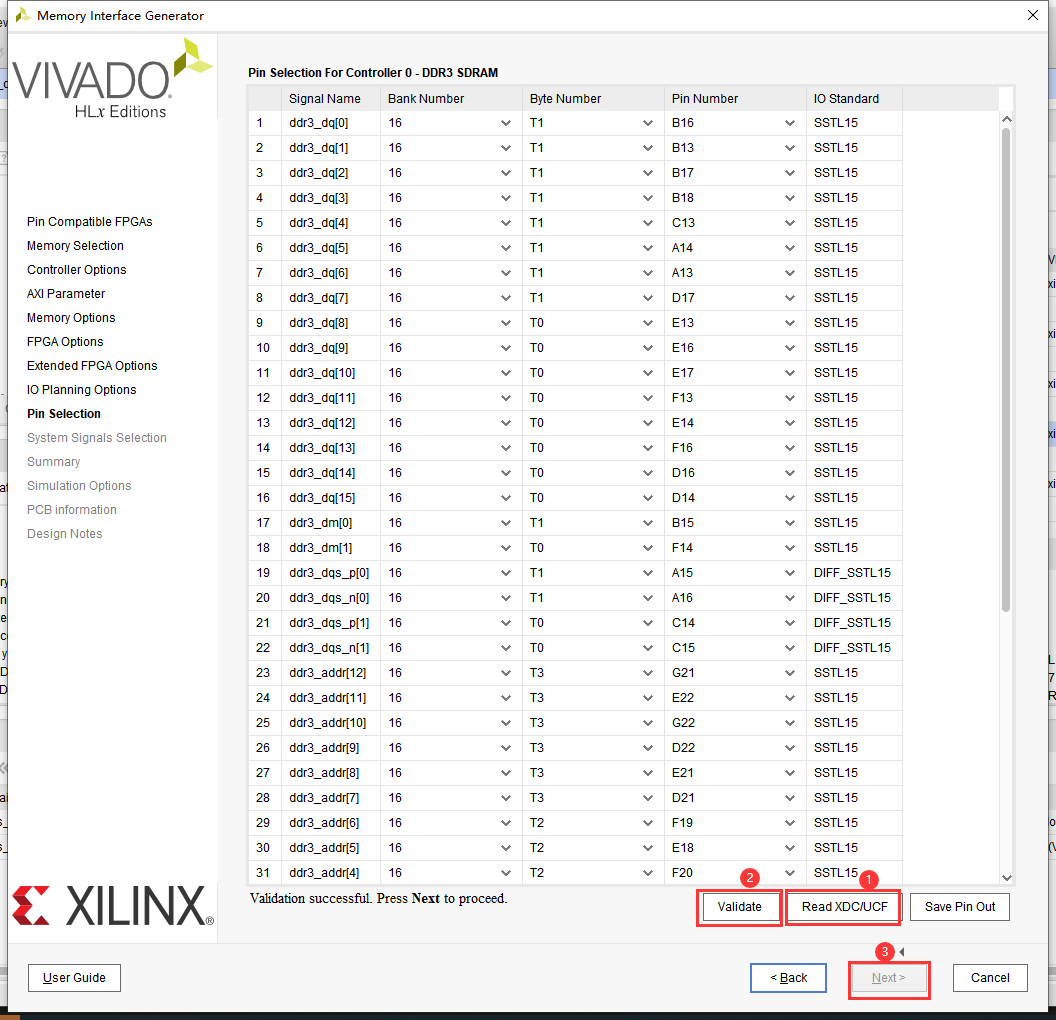

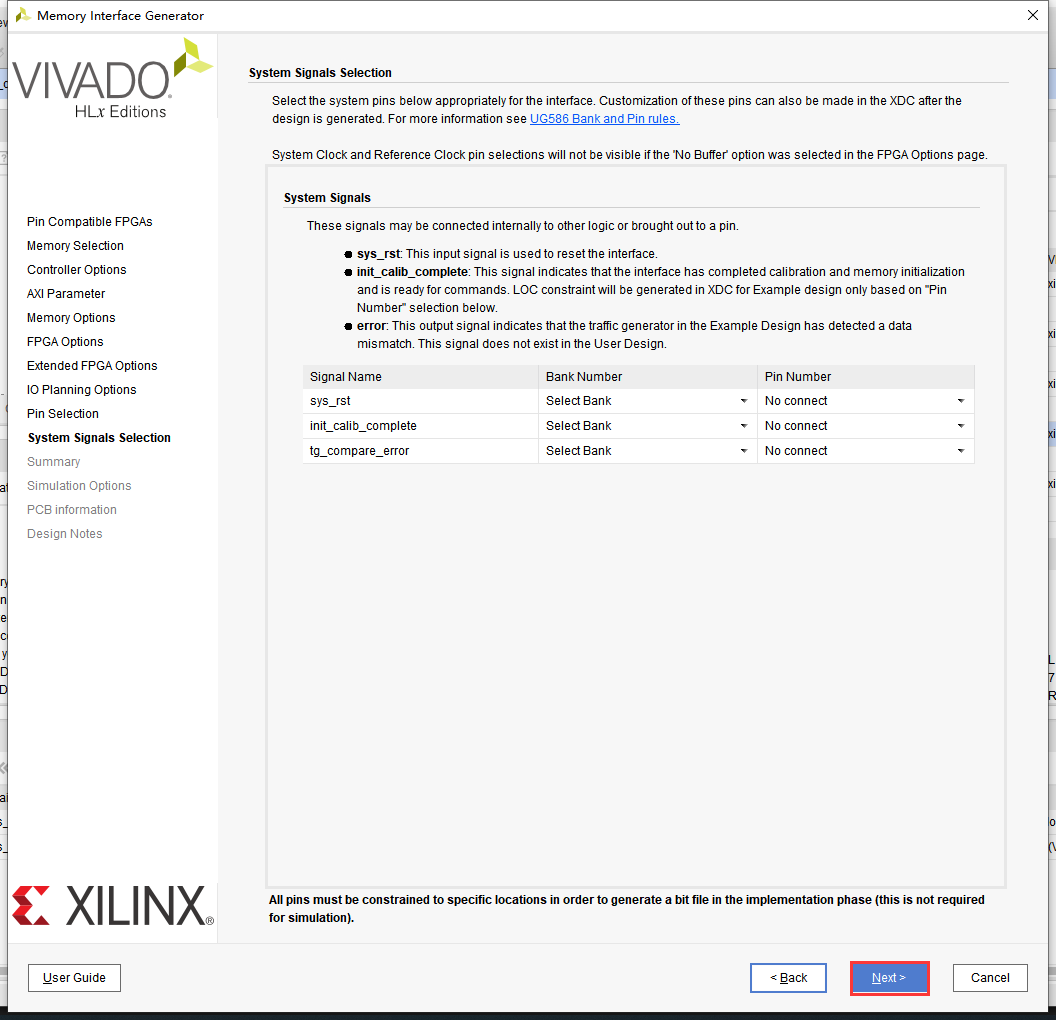

10.PAGE10:Pin Selection Options(引脚选择 选项卡)

- 第一步导入XDC,第二步验证一下,第三部NEXT;

- 如果这里出现 clk_ref,则说明之前你的clock reference 没有选择内部信号;

11.PAGE11:summary

浙公网安备 33010602011771号

浙公网安备 33010602011771号