FPGA学习笔记02-VHDL语法基础-顺序语句

三、LOOP语句

2. WHILE-LOOP语句

(1) 书写格式

1 WHILE 条件 LOOP 2 <顺序处理语句> 3 END LOOP [标号]

在while-loop循环中,条件为真执行循环,条件为假结束循环。

(2) 例子

1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.std_logic_arith.all; 4 use ieee.std_logic_unsigned.all; 5 ENTITY test_whileloop is 6 port( 7 sysclk : in std_logic; 8 rst_n : in std_logic; 9 --a : IN STD_LOGIC_VECTOR(7 DOWNTO 0); 10 result : OUT STD_LOGIC); 11 END test_whileloop; 12 13 architecture example_while of test_whileloop is 14 signal a : std_logic_vector(7 downto 0); 15 begin 16 17 process(sysclk,rst_n) 18 begin 19 if rst_n = '0' then 20 a <= (others => '0'); 21 elsif rising_edge(sysclk) then 22 if a = "11111111" then 23 a <=(others => '0'); 24 else 25 a <= a + 1; 26 end if; 27 end if; 28 end process; 29 30 process(a) 31 variable tmp : STD_LOGIC; 32 variable i : integer; 33 begin 34 tmp := '0'; 35 i := 0; 36 WHILE (i < 8) LOOP 37 tmp := tmp XOR a(i); 38 i := i + 1; 39 END LOOP; 40 result <= tmp; 41 END PROCESS; 42 END example_while;

备注:<tmp := '0'> <tmp := tmp xor a(i)>这句话是偶校验,偶校验是指,tmp(校验位)和a算在一起一共有偶数个‘1’;

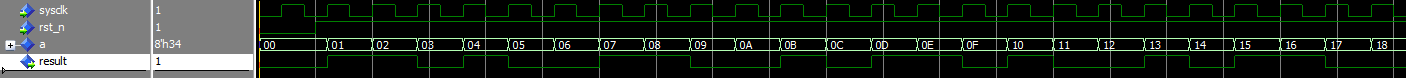

(3) 仿真结果

2. NEXT语句

(1) 书写格式

1 NEXT [标号] [WHEN 条件]

(2) 例子代码

1 use ieee.std_logic_1164.all; 2 use ieee.std_logic_arith.all; 3 use ieee.std_logic_unsigned.all; 4 ENTITY test_whileloop is 5 port( 6 sysclk : in std_logic; 7 rst_n : in std_logic; 8 result : OUT STD_LOGIC_VECTOR(1 DOWNTO 0)); 9 END test_whileloop; 10 11 architecture example_while of test_whileloop is 12 signal a : std_logic_vector(7 downto 0); 13 begin 14 15 process(sysclk,rst_n) 16 begin 17 if rst_n = '0' then 18 a <= (others => '0'); 19 elsif rising_edge(sysclk) then 20 if a = "11111111" then 21 a <=(others => '0'); 22 else 23 a <= a + 1; 24 end if; 25 end if; 26 end process; 27 28 process(a) 29 variable tmp1,tmp2 : std_logic; 30 variable i,j : integer; 31 begin 32 tmp1 := '0'; 33 tmp2 := '0'; 34 i := 0; 35 j := 0; 36 N1 : FOR i in 7 DOWNTO 1 loop 37 N2 : FOR j in 0 TO j loop 38 NEXT N1 WHEN i = j; 39 tmp1 := a(i); 40 tmp2 := a(j); 41 END LOOP N2; 42 END LOOP N1; 43 result <= tmp1&tmp2; 44 END PROCESS; 45 END example_while;

(3) 仿真结果

(4) 说明

- NEXT语句结束本次循环迭代,进入下一次循环;

- [标号]表明下一次循环的起始位置;没有标号从loop开始循环;

- [WHEN条件]是NEXT语句的执行条件;没有条件则无条件进入下一次循环;

- NEXT语句主要用于loop语句内部的循环控制;

- EXIT语句与NEXT语句类似;在嵌套循环时,都是结束内部循环,进入标号位置;

浙公网安备 33010602011771号

浙公网安备 33010602011771号