异步复位,同步释放(转)

异步复位同步释放电路

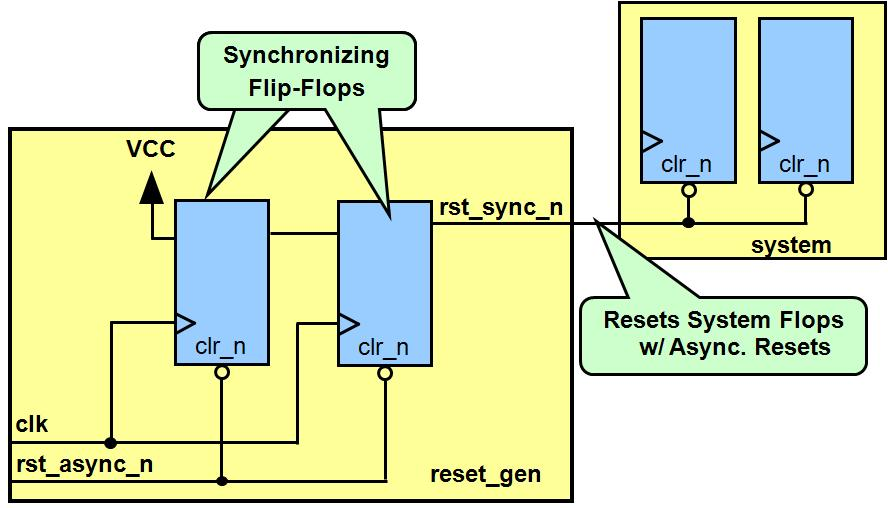

在进行时序分析的时候要保证传输的信号满足建立时间和保持时间,避免采样发生亚稳态(亚稳态会造成采样不确定;亚稳态传播)。同样复位信号在复位和释放的时候也要满足建立时间和保持时间。一般采用异步复位同步释放的方式,如下图所示:

左边两个寄存器是同步释放寄存器,右边是需要复位的design。

1. 当rst_async_n为低,复位的时候,立马异步复位design。

当rst_async_n由低变高,复位释放的时候,第一级寄存器采样VCC可能出现亚稳态,第二级再同步一次,基本不会出现亚稳态。

always @ (posedge clk, negedge rst_async_n)

if (!rst_async_n)

{rst_s2,rst_s1} <= 0;

else

{rst_s2,rst_s1} <= {rst_s1,1'b1};

assign rst_sync_n = rst_s2;

endmodule

两级同步基本可以消除亚稳态

同步释放电路中,第一级寄存器一般会发生亚稳态,亚稳态传播一段时间(小于一个周期)后,会恢复稳定,第二级寄存器对稳定后的信号采样,不会发生亚稳态。但如果工艺很先进的时候,亚稳态持续了一个周期以上,那么第二级寄存器采样也会发生亚稳态,这样就需要第三极寄存器同步。

参考

真理剑客是个武功高强的朝圣者,独自战胜了三个匪徒,在基督徒到达终点之前加入了他的朝圣队伍。