和FPGA设计不同

1)无法换管子

2)由于没有CTS,所以多出新的问题

26)FLOW

In regular backend flow with onlyone functional mode SDC, please explain timing closure methodology/issue/fixesin pre-CTS, post-CTS and post-Route stages.

在只有一个function SDC的普通后端流程中,对于pre-CTS, post-CTS 和 post-Route这三步,请分别讲述它们在时序收敛上的方法,一般会遇到的问题和解决方法。

答案:

pre-CTS时,使用ideal clock,只fix setup

post-CTS后,使用propagate clock,可以只fix setup,检查hold,但可以不fix hold

post-Route后,依然使用propagate clock,fix setup和hold

具体遇到的问题和解决方法:

pre-CTS: 如果有setup,重在调整floorplan,buffer tree结构

Post-CTS: 如果有setup,重在调整clock tree,buffer tree结构或者size

Post-Route: 如果有setup/hold,微调clock tree/buffer tree的size,routingchannel和图层,实在不行,回到CTS

3)

28)CTS

There are function SDC withmultiple clock domain and scan SDC with an individual scan clock. Assume thosefunctional clock are un-balanced, how do you balance the scan clock?

假设一个设计的function SDC中有多个时钟,在scan mode下,另有一个单独的scanclock,如果functional的各个时钟树之间是不平衡的,请问如何平衡那个scan时钟?

答案:

如果CTS支持multi-mode,直接使用即可。

如果不支持,或者MMCTS效果不理想,就是在CTS spec中,同时定义function 和 DFT 的时钟,然后在scanclock里面,把MUX设为leave pin,再让它们与function clok到MUX的延迟做动态平衡

https://blog.csdn.net/u011729865/article/details/53488431

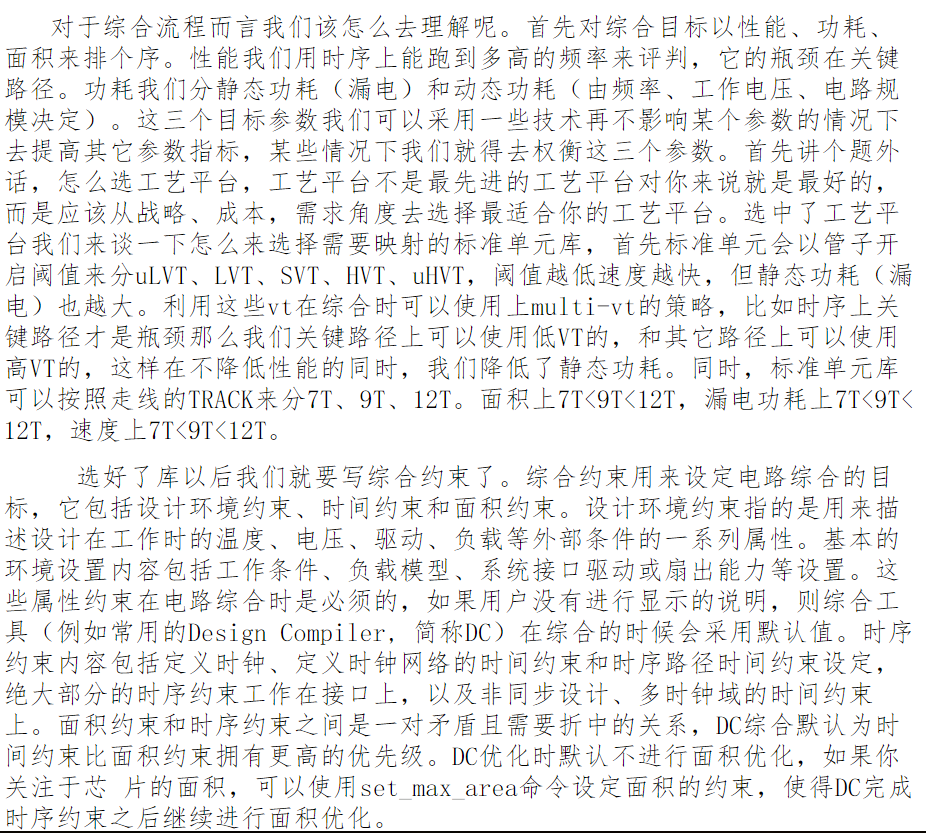

标准单元库的理解

对umc28nm standard cell library,做一些阅读理解,很多数据资料来源。

HVT/SVT/LVT的意思?

high Vt

Standard Vt(也有称为Regular Vt,即RVT)

low Vt

阈值电压越低,因为饱和电流变小,所以速度性能越高;但是因为漏电流会变大,因此功耗会变差。

PVT

process、voltage、temperature

technology是28nm工艺;process是制造流程,一般分为FF/TT/SS。两者的内容应该包括high-speed/high-density/HVT/SVT/LVT/multi-channel等信息。

multi-channel library

对应不同的gate-length,即沟道长度。一般比工艺28nm要大一些。

例如,umc28nm的SVTmin 相对 SVTmax,性能增加20%,静态功耗增加80%。

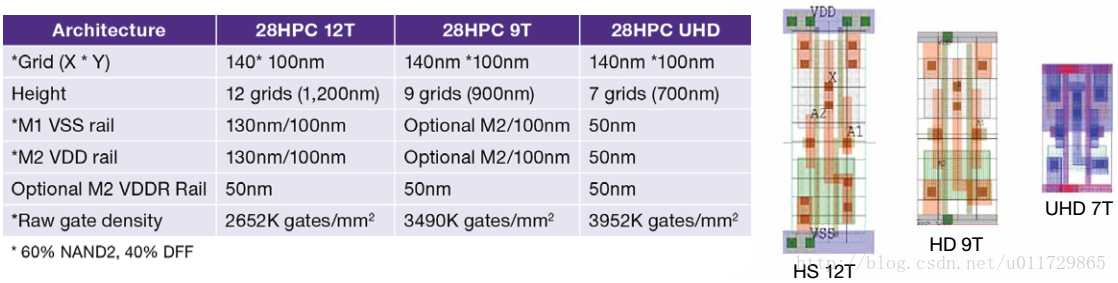

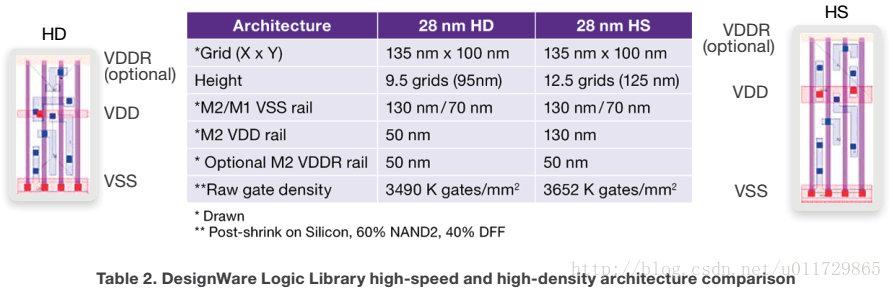

7T/9T/12T

分别对应ultra-high-density(for lowest power in SOC blocks)、high-density(for highest density in GPU blocks)、high-speed(for highest performance in CPU blocks)。

T,代表track;是单元库的版图规则;作为一个计量单位。

标准单元库的单元高度,基本都是固定的,方便版图的布局;高度,通常以track作为计量单位,即用M2 track pitch来表示。

track和pitch的区别?

对于前端设计人员来说,不必深入。只要看懂databook就可以了。个人当前理解track和pitch,就是一样的;pitch=minSpacing+minWidth。

grid是单元库里,与工艺制造精度相关的名称。一般pin都放置在grid上,这也不需要多加深入,就认为是工艺在版图上的最小精度就可以了。

don’t use单元列表

综合不允许使用的,一般是驱动能力太强或者太弱的标准单元不用;还有其它为了性能、功耗、面积衡量的单元。

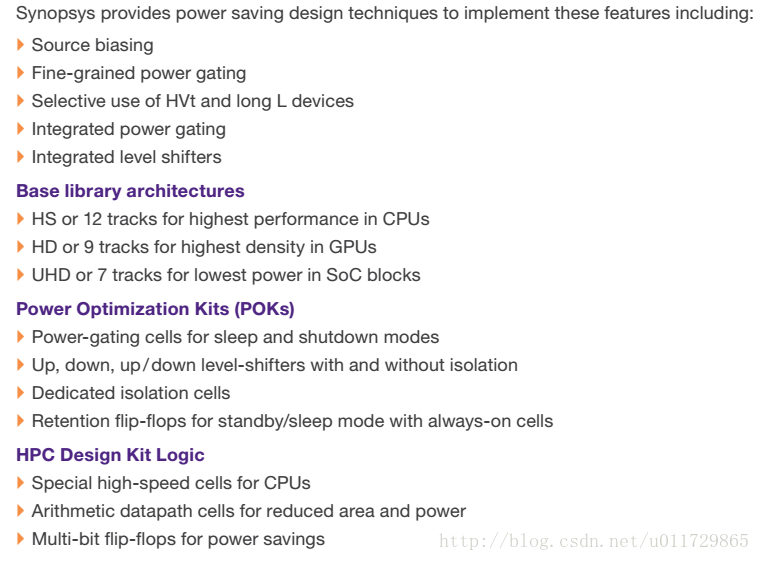

推荐的单元库选择方法

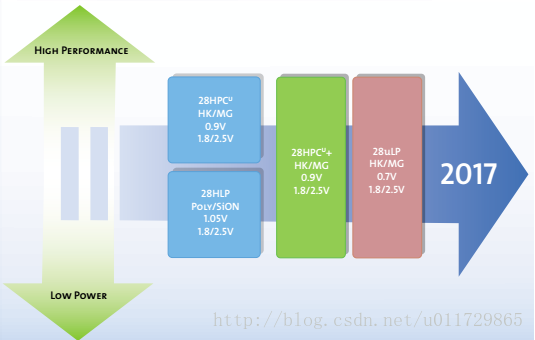

HLP和HPC的区别

HLP,high performance low power;这个应该是主流?

HPC,high performace compact。

ps:28nmHLP的core电压,是1.05V;HPC的core电压,则是0.9V。

举例,以CA53来看,HPC相对HLP,性能增加32%;面积减小5%。

另外,发现HLP的版图,跟HPC不一样。

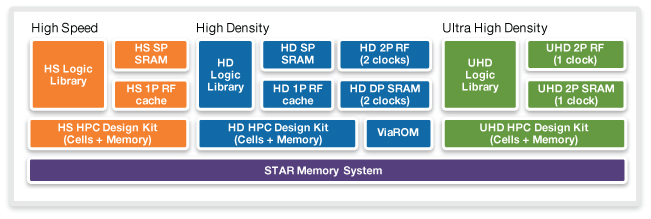

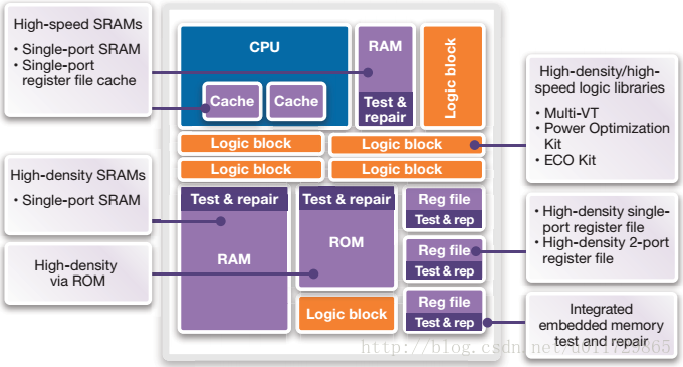

SOC系统需要的单元库划分

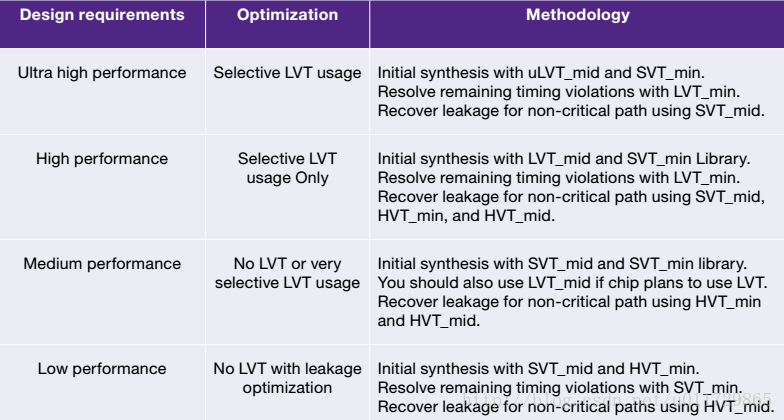

推荐的单元库优化方法

————————————————

版权声明:本文为CSDN博主「亓磊」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/u011729865/article/details/53488431

数字标准单元库-后端简要理解

参考博文:https://blog.csdn.net/u011729865/article/details/53488431

对umc28nm standard cell library,做一些阅读理解,很多数据资料来源。

HVT/SVT/LVT的意思?

high Vt

Standard Vt(也有称为Regular Vt,即RVT)

low Vt

阈值电压越低,因为饱和电流变小,所以速度性能越高;但是因为漏电流会变大,因此功耗会变差。

PVT

process、voltage、temperature

technology是28nm工艺;process是制造流程,一般分为FF/TT/SS。两者的内容应该包括high-speed/high-density/HVT/SVT/LVT/multi-channel等信息。

multi-channel library

对应不同的gate-length,即沟道长度。一般比工艺28nm要大一些。

例如,umc28nm的SVTmin 相对 SVTmax,性能增加20%,静态功耗增加80%。

7T/9T/12T

分别对应ultra-high-density(for lowest power in SOC blocks)、high-density(for highest density in GPU blocks)、high-speed(for highest performance in CPU blocks)。

T,代表track;是单元库的版图规则;作为一个计量单位。

标准单元库的单元高度,基本都是固定的,方便版图的布局;高度,通常以track作为计量单位,即用M2 track pitch来表示。

track和pitch的区别?

对于前端设计人员来说,不必深入。只要看懂databook就可以了。个人当前理解track和pitch,就是一样的;pitch=minSpacing+minWidth。

grid是单元库里,与工艺制造精度相关的名称。一般pin都放置在grid上,这也不需要多加深入,就认为是工艺在版图上的最小精度就可以了。

don’t use单元列表

综合不允许使用的,一般是驱动能力太强或者太弱的标准单元不用;还有其它为了性能、功耗、面积衡量的单元。

推荐的单元库选择方法

HLP和HPC的区别

HLP,high performance low power;这个应该是主流?

HPC,high performace compact。

ps:28nmHLP的core电压,是1.05V;HPC的core电压,则是0.9V。

举例,以CA53来看,HPC相对HLP,性能增加32%;面积减小5%。

另外,发现HLP的版图,跟HPC不一样。

SOC系统需要的单元库划分

推荐的单元库优化方法

举例说明ulvt:

uLVT是什么意思呢,UltraLowVoltageThreshold,指的是标准逻辑单元(StandardCell)用了超低电压门限。电压低对于动态功耗当然是个好事,但是这个标准单元的漏电也很高,和频率是对数关系,也就是说,漏电每增加10倍,最高频率才增加log10%。后端可以给EDA工具设一个限制条件,比如只有不超过1%的需要冲频率的关键路径逻辑电路使用uLVT,其余都使用LVT,SVT或者HVT(电压依次升高,漏电减小),来减小总体漏电。对于动态功耗,后端还可以定制晶体管的源极和漏极的长度,越窄的电流越大,漏电越高,相应的,最高频率就可以冲的更高。所以我们有时候还能看到uLVTC16,LVTC24之类的参数,这里的C就是指ChannelLength。

本文来自博客园,作者:{e_shannon},转载请注明原文链接:https://www.cnblogs.com/e-shannon/p/15843668.html