【转】贴片晶振挖空敷铜

链接:https://baijiahao.baidu.com/s?id=1601884209225441523&wfr=spider&for=pc

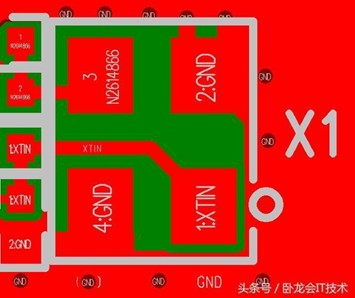

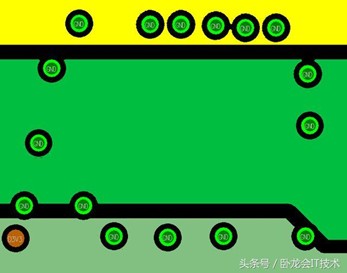

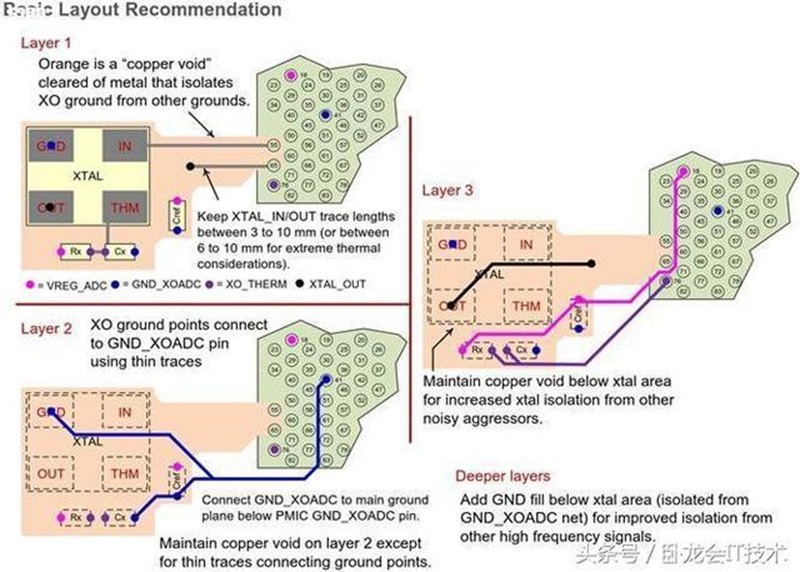

在一些多层PCB设计中,我们经常能看到贴片晶振在设计时会在相邻*面层做挖空处理。如下所示:

Figure 1 TopLayer布局 Figure 2 Layer2 LAYOUT

Layer2为GND层,在设计时用禁止区域将晶振正下方做了挖空处理;

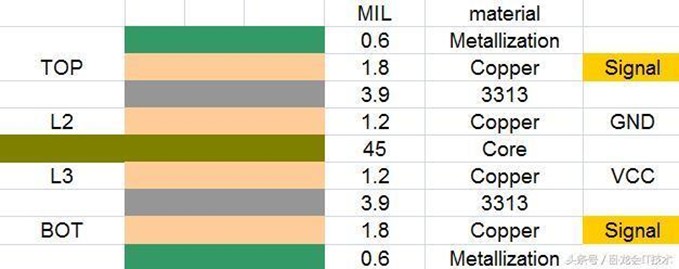

由图可知,芯板占了主要的厚度,焊盘到*面的距离d只有3.9mil,非常的小,如果用电容计算公式C=εs/4πkd计算出来的寄生电容在数pF-数十pF间。

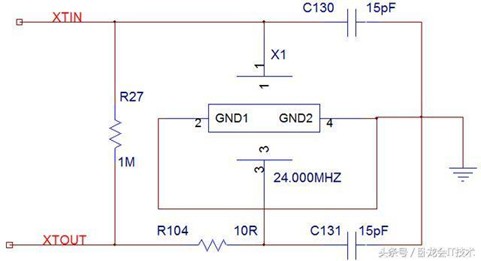

有一个实际案例是这样的:原厂参考原理图中晶振的负载电容是15pF。

因此在设计当中,尤其是对于晶体设计,更加需要控制对地的寄生电容。一般这个数值是要保证晶体到地的距离大于250um,所以一般都要挖掉一层到两层来达到设计要求。

除了负载电容会影响到晶振频偏外,但大家似乎都忘了,高温也会影响频偏。

如高通说法,其实真正最主要用意是隔绝热传导,避免周围的PMIC或者其他发热体的热透过铜皮传导到晶振,以至于频偏。故直接不铺铜,以隔绝热的传递。