浅谈AXI协议及搭建自己的AXI IP核-01(协议解读)

一、什么是AXI协议?

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,AMBA包括以下几个部分:

- Advanced High-performance Bus (AHB):高性能总线,用于连接高性能主设备,如处理器和DMA控制器等。AHB总线具有多主从设备、分时复用等特点,支持带宽请求、优先级传输和错误处理等功能。

- Advanced Peripheral Bus (APB):外设总线,用于连接低速器件,例如控制器和定时器等。它是单主多从的设备总线,APB总线是一种简单的串行总线,具有定时器可编程特性,其速度较慢,但其节点可达数目较多。

- Advanced eXtensible Interface (AXI):可扩展性接口,用于连接系统中高速器件之间的互连。AXI是多主和多从设备的连接,AXI总线支持优先级传输、带宽请求、流水线传输和乱序传输等功能,是AMBA规范中最高级别的总线接口协议。

学过STM32的同学应该很眼熟APB总线,在STM32等微处理器架构中GPIO等外设都是挂载在APB总线上的,具体APB协议这里不过多深入。

而AXI由于地址/控制和数据相位是分离的,支持不对齐的数据传输及突发传输的特点,因此在擅长高速、高数据量的FPGA上大放异彩。

二、为什么要学习AXI协议

在学习xilinx FPGA过程中我们会经常遇到AXI接口,特别在ZYNQ架构上,ZYNQ-7系列上集成了2个异构高性能A9处理器以及FPGA资源,因此需要一种接口用来实现FPGA与ARM的高速数据交换,而由于上述AXI总线的天然优势使之自然而然地承担了该任务。同时xilinx的一些其他高速接口的IP核的控制(PCIE、DDR等)也是通过AXI接口实现的。因此想要学习ZYNQ架构或者处理高速信号,AXI协议都是绕不过去的门槛。

三、AXI协议

AXI协议定义了五个独立的事务通道。地址通道携带着控制信息,用于描述传输数据的性质。五个独立通道都由一组信息信号、以及提供双向握手机制的VALID和READY信号组成。

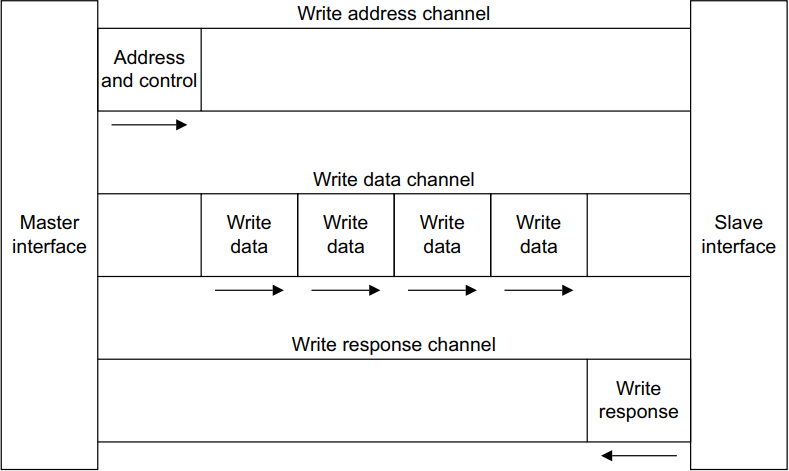

下面结合读写过程,对5个通道进行说明, - 写过程

上图表示了一次AXI写的过程,

写地址通道:首先Master在写地址通道(write address channel)发起一次写地址请求,表明自己写入的数据将存储至哪个地址。

写数据通道:随后Master在写数据通道(write data channel)写入数据,注意,axi是支持突发传输(即给一个起始地址,可以连续写入多个数据,第二次写地址时地址自增写入数据长度即可),因此可以看到写数据通道写入了多个数据,这些数据在地址上是连续的。例如假设数据位宽为16bit(2Byte),突发长度为8(一次写入8个数据),那么写地址每次需要增加 2*8 。

写应答通道:由于双方已经约定好了数据位宽及突发长度,所以在Mater写完最后一个数据(wlast)后,Slave会进行写通道和写数据的应答,表示Slave已经成功完成接受这一次突发写入内容。 - 读过程

上图表示了一次AXI读过程,

读地址通道:Master在读地址通道写入想要读取的数据地址,

读数据通道:Slave在读数据通道将该地址的突发长度数据返回给Master - 握手机制

值得注意的是,在这5个通道所产生的读写事务都是基于握手机制完成的,主从通信都使用相同的VALID/READY握手过程来传输地址、数据和控制信息。这种双向流控制机制意味着Master和Slave都可以控制信息的移动速率。传输只发生在VALID和READY信号都是1的时候。

- 源端产生VALID=1信号:表示地址、数据或控制信息可用。

- 终端生成READY=1信号:表示可以接受该信息。

那么就存在一个问题,握过程中VALID和READY的前后关系,或者握手过程是怎么样的?

AXI支持三种形式的握手形式:

- VALID before READY:

源端发起VALID后必须等到终端回应READY后才可以释放VALID。 - READY before VALID :

终端先产生READY信号,源端产生VALID,终端拉高READY后可以取消拉高,不必一直保持到完成握手。 - VALID with READY:

VALID和READY信号同时拉高,完成握手。

4. 读写时序

-

写时序图

-

读时序

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】凌霞软件回馈社区,博客园 & 1Panel & Halo 联合会员上线

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】博客园社区专享云产品让利特惠,阿里云新客6.5折上折

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 清华大学推出第四讲使用 DeepSeek + DeepResearch 让科研像聊天一样简单!

· 推荐几款开源且免费的 .NET MAUI 组件库

· 实操Deepseek接入个人知识库

· 易语言 —— 开山篇

· 【全网最全教程】使用最强DeepSeekR1+联网的火山引擎,没有生成长度限制,DeepSeek本体