执行硬件设置以及实现低功耗的STM32 GPIO配置

引言 STM32微控制器通用输入/输出引脚(GPIO)提供许多与应用框架内外部电路相连接的方 法。本应用笔记提供有关GPIO配置的基本信息,以及硬件和软件开发人员使用GPIO引脚优 化其STM32 32-bit ARM Cortex MCUs电源性能的指南。 本应用笔记必须与www.st.com提供的相关STM32参考手册和数据表结合使用。

1 文档约定

1.1 词汇表

本节介绍本文档中所用的主要首字母缩略词和缩写词定义。

AMR: 绝对最大额定值 GPIO: 通用输入/输出 GP: 通用 P: 推挽 PU: PU上拉 PD: 下拉

OD: 开漏 AF: 复用功能 VIH: 由数字量输入解析为逻辑1的最小电压电平

VIL: 由数字量输入解析为逻辑0的最大电压电平

VOH: 由数字量输出设置为逻辑1值所提供的最小保证电压电平

VOL: 由数字量输出设置为逻辑0值所提供的最大保证电压电平

VDD: 为 I/Os 稳压器供电的外部电源。

VDDIO2: I/O的外部电源,独立于VDD电压

VDDA: 模拟量的外部电源 VSS: 接地 IIH: 输入为1时的输入电流 IIL: 输入为0时的输入电流

IOH: 输出为1时的输出电流 IOL: 输出为0时的输出电流 Ilkg: 漏电流 IINJ: 注入电流

1.2 寄存器缩写

寄存器说明中使用以下缩写词(x = A至H):

GPIOx_MODER: GPIO端口模式寄存器 GPIOx_OTYPER: GPIO输出类型寄存器 GPIOx_OSPEEDR: GPIO输出速度寄存器

GPIOx_PUPDR: GPIO端口上拉/下拉寄存器 GPIOx_IDR: GPIO端口输入数据寄存器 GPIOx_ODR: GPIO端口输出数据寄存器

GPIOx_BSRR: GPIIO端口置位/复位寄存器 GPIOx_LCKR: GPIO端口配置锁定寄存器 GPIOx_AFRL: GPIO复用功能低位寄存器

GPIOx_AFRH: GPIO复用功能高位寄存器 GPIOx_ASCR: GPIO端口模拟量开关控制寄存器

2 GPIO 主要特性

STM32 GPIO具备下列特性:

• 输出状态:推挽或开漏 + 上拉/下拉,取决于GPIOx_mode、GPIOx_OTYPER、和 GPIOx_PUPDR寄存器设置

• 从输出数据寄存器GPIOx_ODR或外设(复用功能输出)输出数据

• 可为每个I/O(GPIOx_OSPEEDR)选择不同的速度

• 输入状态:浮动、上拉/下拉、模拟量,取决于GPIOx_MODER、GPIOx_PUPDR和 GPIOx_ASCR寄存器设置

• 将数据输入到输入数据寄存器(GPIOx_IDR)或外设(复用功能输入)

• 置位和复位寄存器(GPIOx_ BSRR),对 GPIOx_ODR 具有按位写权限

• 锁定机制(GPIOx_LCKR),可冻结 I/O 端口配置

• 模拟功能选择寄存器(GPIOx_MODER和GPIOx_ASCR)

• 复用功能选择寄存器(GPIOx_MODER,GPIOx_AFRL,和GPIOx_AFRH)

• 快速翻转,每次翻转最快只需要两个时钟周期

• 引脚复用非常灵活,允许将 I/O 引脚用作 GPIO 或多种外设功能中的一种

3 GPIO功能说明

STM32 GPIO可用于各种配置。每个GPIO引脚都可以通过软件在以下任何模式下单独配置:

• 输入浮空

• 输入上拉

• 输入下拉

• 模拟

• 具有上拉或下拉功能的开漏输出

• 具有上拉或下拉功能的推挽输出

• 具有上拉或下拉功能的复用功能推挽

• 具有上拉或下拉功能的复用功能开漏

3.1 GPIO缩写

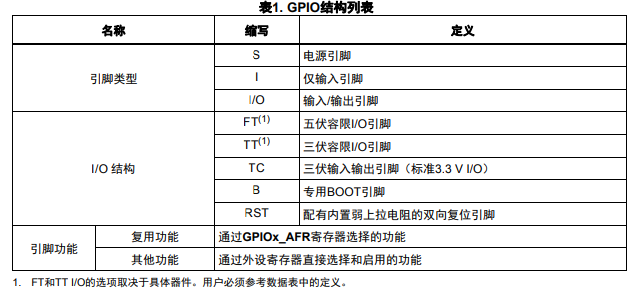

STM32器件范围内有多种GPIO结构可供使用。每个结构都与选项列表相关联

表 1总结了适用于STM32产品的GPIO定义和缩写

例如,以下描述涉及STM32数据表中的GPIO: PB1 I/O FT表示: – PB1 I/O引脚:端口B位1输入/输出 – FT:5 V 容限 在开始电路板设计之前,请务必参考STM32产品的数据表或STM32CubeMX工具,以检查与目 标应用程序一致的GPIO可用性。 请参阅www.st.com/stm32上有关软件开发工具的部分

3.2 GPIO等效原理

STM32产品集成了三个主要的GPIO基本结构:

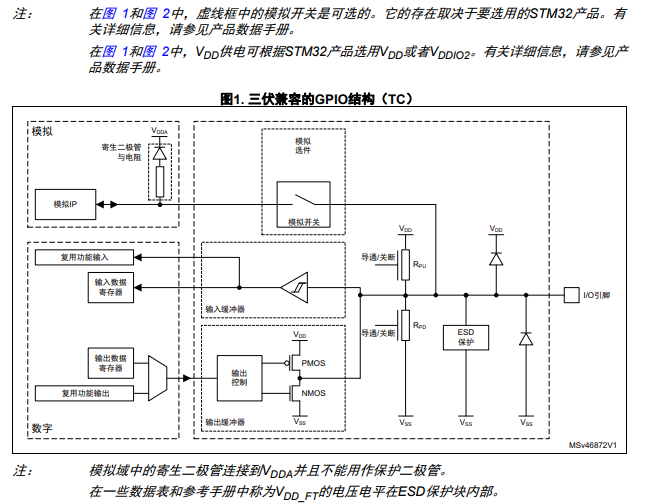

• 三伏兼容(缩写为TC)。 图 1给出了等效的GPIO图结构。

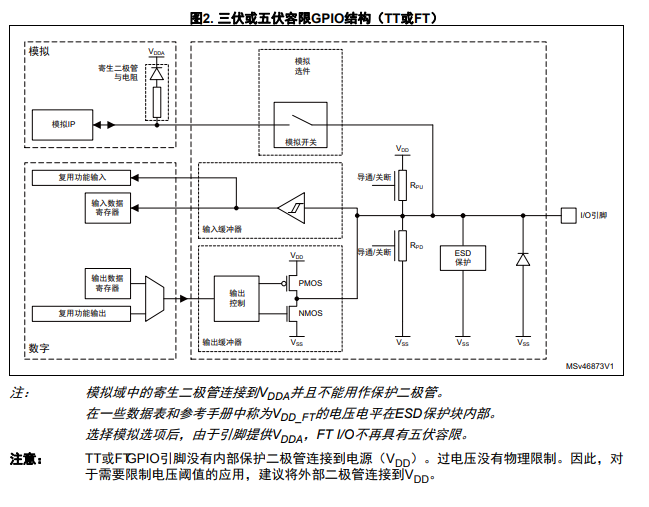

• 三伏容限(缩写为TT)。

• 五伏容限(缩写为FT) 图 2给出了TT或FT等效的GPIO图结构。

3.3 GPIO模式描述

本节介绍STM32器件中可用的GPIO引脚配置

3.3.1 输入模式配置

当STM32器件I/O引脚配置为输入时,必须选择以下三个选项之一:

• 带内部上拉的输出。STM32器件中使用上拉电阻,以确保在浮动输入信号的情况下具有 良好定义的逻辑电平。根据应用要求,可以使用外部上拉电阻。

• 带内部下拉的输入。在STM32器件中使用下拉电阻,确保在浮动输入信号的情况下具有 良好定义的逻辑电平。根据应用要求,可以使用外部下拉。

• 悬空输入。信号电平跟随外部信号。当没有外部信号时,施密特触发器在由外部噪声引 起的逻辑电平之间随机切换。这增加了总体消耗。

编程为输入时,I/O端口具有以下特征:

• 输出缓冲器被关闭

• 施密特触发器输入被打开

• 根据GPIOx_PUPDR寄存器中的值决定是否激活上拉或下拉电阻

• 输入数据寄存器每隔 1 个 AHB 时钟周期对 I/O 引脚上的数据进行一次采样

• 通过读取GPIOx_IDR输入数据寄存器可获取I/O状态

浙公网安备 33010602011771号

浙公网安备 33010602011771号