Physical Cell 介绍——Boundary Cell (End-CAP Cell)

本公众号【读芯树:duxinshu_PD】主要介绍数字集成电路物理设计相关知识,才疏学浅,如有错误,欢迎指正交流学习。

这是集成电路物理设计的第一个系列【physical cell】的第一篇文章,也是本公众号的第一篇文章,从boundary cell说起:

1,什么是boundary cell?

-

boundary cell也叫做endcap cell, 一般会放置在floorplan的四周,ROW的边界。

2,为什么需要insert boundary cell?

-

在芯片制造的过程中,最边界的standard cell最容易受到损伤,为减少standard cell的制造过程中的损伤,需要在边界放置boundary cell,boundary cell有dummy poly gate,当制造过程中的损伤发生在边界时,boundary cell的损伤不会影响正常standard cell的功能。

-

如果没有在边界放置boundary cell, 可能会对芯片的功能造成不可逆的损伤。

-

在well和implant 层之间不能有gap,否则会有drc,boundary cell保证了well和implant 层之间没有gap。

-

boundary cell的poly extension保证了standard cell的source/drain不会出现在边界。

-

boundary cell放置在row的边界同时保证了边界的well tie的需求。

3,boundary cell的layout是什么样的?

-

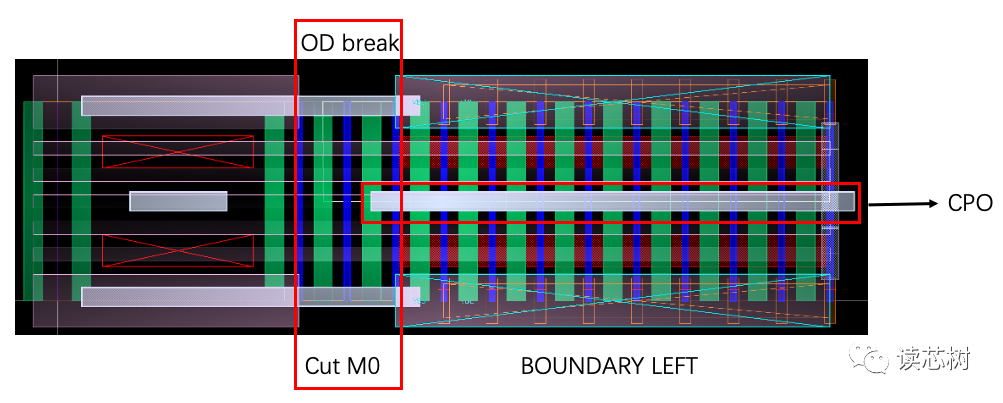

boundary cell没有logic pin,只有VDD/GND的连接;

-

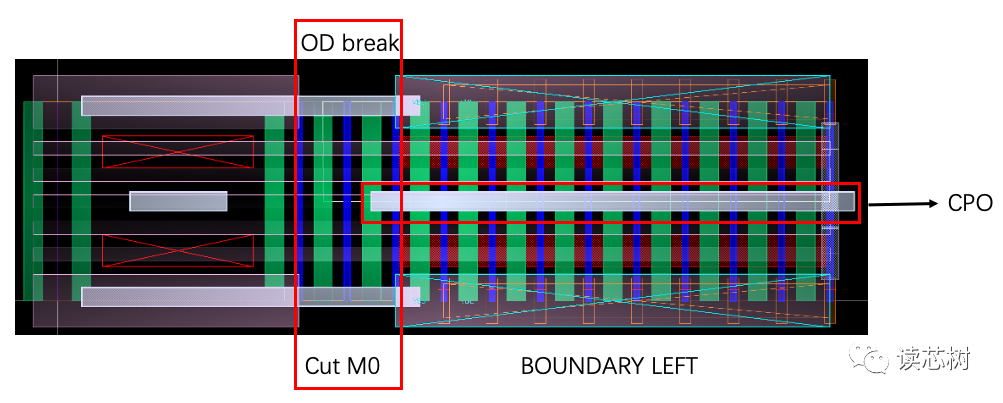

boundary cell在最左或者右侧扩展NWELL来减小well proximity effects (WPE 见5)。

-

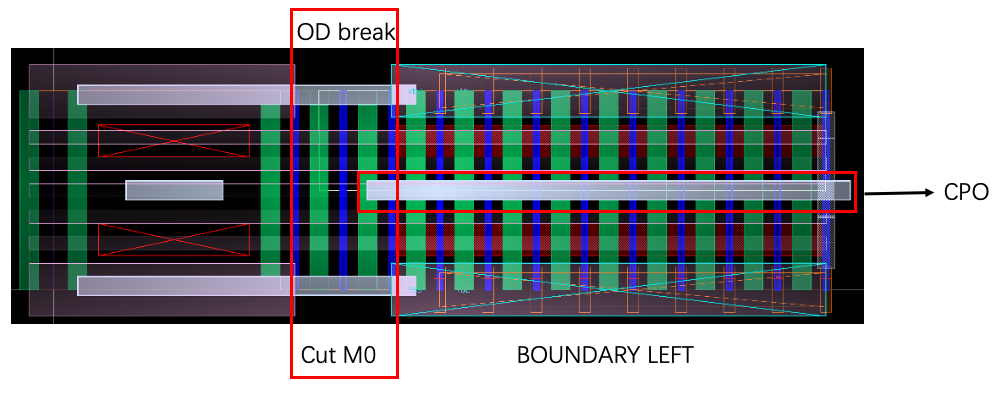

boundary cell有dummy poly用于保护standard cell 的gate。

-

boundary cell的poly layer会被切断 (Poly Cut layer)

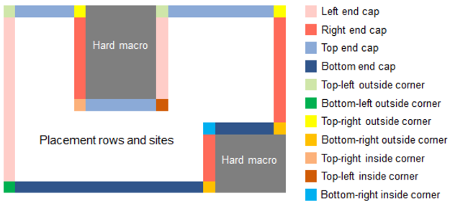

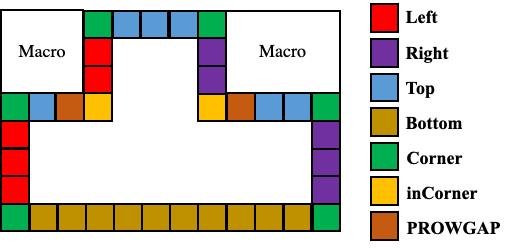

4,如何在floor plan阶段insert boundary cell?

FC/ICC2 cmd:

>set_boundary_cell_rules \ -top_boundary_cells "BOUNDARYPROW* \ -bottom_boundary_cells "BOUNDARYPROW* \ -left_boundary_cell "BOUNDARYLEFT*" \ -right_boundary_cell "BOUNDARYRIGHT*" \ -top_right_outside_corner_cell "BOUNDARYPCORNE*" \ -bottom_right_outside_corner_cell "BOUNDARYPCORNER*" \ -top_left_outside_corner_cell "BOUNDARYPCORNER*" \ -bottom_left_outside_corner_cell "BOUNDARYPCORNER*" \ -top_right_inside_corner_cells "BOUNDARYPINCORNER*" \ -bottom_right_inside_corner_cells "BOUNDARYPINCORNER*" \ -top_left_inside_corner_cells "BOUNDARYPINCORNER* \ -bottom_left_inside_corner_cells "BOUNDARYPINCORNER*" \ -top_left_inside_horizontal_abutment_cells "BOUNDARYPROWLGAP*" \ -bottom_left_inside_horizontal_abutment_cells "BOUNDARYPROWLGAP*" \ -top_right_inside_horizontal_abutment_cells "BOUNDARYPROWRGAP*" \ -bottom_right_inside_horizontal_abutment_cells "BOUNDARYPROWRGAP*"\ -mirror_left_inside_corner_cell \ -mirror_left_outside_corner_cell \ -segment_parity {horizontal_odd vertical_even} \ -min_vertical_jog 0.042 \ -min_horizontal_jog 0.612 \ -min_vertical_jog 0.042 \ -min_horizontal_jog 0.612 \ -min_vertical_separation 0.21 \ -min_horizontal_separation 2.397>compile_boundary_cells

>check_boundary_cell

Innovus cmd:>setEndCapMode -reset>setEndCapMode \

-rightEdge BOUNDARYLEFT* \ -leftEdge BOUNDARYRIGHT*\ -leftTopCorner BOUNDARYPCORNER*\ -leftBottomCorner BOUNDARYPCORNER* \ -rightTopCorner BOUNDARYPCORNER*\ -rightBottomCorner BOUNDARYPCORNER* \ -topEdge {BOUNDARYPROW8* BOUNDARYPROW4*BOUNDARYPROW2* BOUNDARYPROW1*} -bottomEdge {BOUNDARYPROW8* BOUNDARYPROW4* BOUNDARYPROW2* BOUNDARYPROW1*} -rightTopEdge BOUNDARYPINCORNER* \ -rightBottomEdge BOUNDARYPINCORNER* \ -leftTopEdge BOUNDARYPINCORNER* \ -leftBottomEdge BOUNDARYPINCORNER* \ -rightTopEdgeNeighbor BOUNDARYPROWRGAP*\ -rightBottomEdgeNeighbor BOUNDARYPROWRGAP*\ -leftTopEdgeNeighbor BOUNDARYPROWLGAP*\ -leftBottomEdgeNeighbor BOUNDARYPROWLGAP*\ >addEndCap >verifyEndCap -report endcap.rpt

5, 什么是阱临近效应(WPE: Well Proximity Effect)

-

WPE会影响芯片的性能和良率。

-

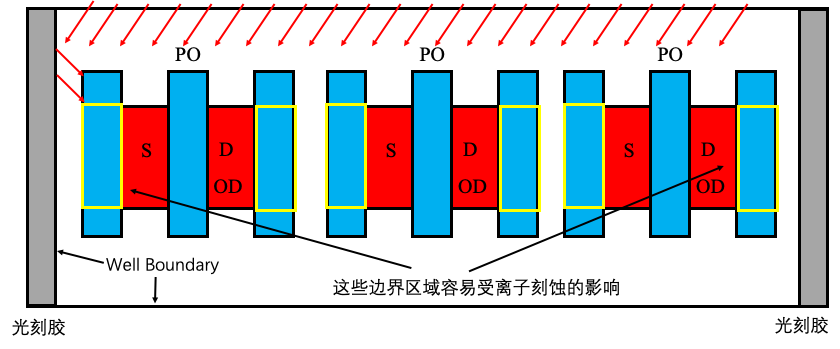

在芯片制造的过程中,会出现各种制造的二级效应,靠近阱边界的晶体管和非边界的晶体管的性能相比有很大的不同,这会造成晶体管速度有+/-10%的差异。

-

离子注入阱的过程中,在阱边界(光刻胶)会造成注入离子的反射散射,位于阱边界的晶体管有不同的离子注入情况,这会造成该晶体管不同的性能表现。

6,参考文献

1,fusion compiler/ IC Compiler 2 user guide

2,innovus user guide