GD32H7 内部 ram 使用 分散加载 配置 详述

1.对ram使用自己编辑的 链接文件重新配置

由于官网没有完全分配出所有的ram,这里自己编辑个全部的,方便自己区分与调用。

1 ; ************************************************************* 2 ; *** Scatter-Loading Description File generated by uVision *** 3 ; ************************************************************* 4 ; 参考链接: https://www.armbbs.cn/forum.php?mod=viewthread&tid=98697&extra=&page=1 5 6 LR_IROM1 0x08040000 0x000C0000 { ; load region size_region 7 ER_IROM1 0x08040000 0x000C0000 { ; load address = execution address 8 *.o (RESET, +First) 9 *(InRoot$$Sections) 10 .ANY (+RO) 11 .ANY (+XO) 12 } 13 14 ;数据DTCM(128K),来自共享 RAM,其起始地址 0x24080000 15 RW_RAM1 0x20000000 0x00020000 { ; RW data 16 .ANY (+RW +ZI) 17 ;*(.dtcm_sram) 18 } 19 20 ;网络接收描述符使用 16k + 16k 21 RW_RAM2 0x30000000 0x00004000 { ; SRAM0 22 .ANY (+RW +ZI) 23 *(.sram0_nocache) ;自定义 section 的执行域 放入 ram 中 24 } 25 26 RW_RAM3 0x30004000 0x00004000 { ; SRAM1 27 .ANY (+RW +ZI) 28 *(.sram1_nocache) 29 } 30 31 ;备份域BKPRAM(4K) 32 RW_RAM4 0x38800000 0x00001000 { ; BKPRAM 33 .ANY (+RW +ZI) 34 ;*(.backup_sram) 35 } 36 37 ;共享 RAM(总512KB-ITCM(64k)-DTCM(128k)=320k), 38 ;其实际为(ITCM+DTCM+AXI SRAM)共享,地址顺序ITCM->DTCM->AXI SRAM,起始地址 0x24080000 39 RW_RAM5 0x240B0000 0x00050000 { ; SHARE RAM 40 .ANY (+RW +ZI) 41 ;*(.share_sram) 42 } 43 44 ;AXI SRAM(512KB) 45 RW_IRAM1 0x24000000 0x00080000 { ; AXI SRAM 46 .ANY (+RW +ZI) 47 ;*(.axi_sram) 48 } 49 50 ;指令ITCM(64k),来自共享 RAM,其起始地址 0x24080000 51 RW_IRAM2 0x00000000 0x00010000 { ; ITCM 52 .ANY (+RW +ZI) 53 ;*(.itcm_sram) 54 } 55 }

对网络的修改使用的 32k cache配置为透传模式;

/* 保护整个SRAM0,共16K字节 */ /* Configure the DMA descriptors and Rx/Tx buffer*/ mpu_set_protection( 0x30000000, /* 基地址 */ MPU_REGION_SIZE_16KB, /* 长度 */ MPU_REGION_NUMBER3, MPU_INSTRUCTION_EXEC_PERMIT, /* NUMER3,允许指令访问 */ MPU_AP_FULL_ACCESS, /* 全访问 */ MPU_TEX_TYPE0, /* 类型扩展域0 */ MPU_ACCESS_NON_SHAREABLE, /* 禁止共用 */ MPU_ACCESS_NON_CACHEABLE, /* 禁止cache */ MPU_ACCESS_BUFFERABLE); /* 允许缓冲 */ /* 保护整个SRAM1,共16K字节 */ /* 没有使用系统时,作为LwIP RAM heap,在 LWIP_RAM_HEAP_POINTER 处定义*/ mpu_set_protection( 0x30004000, /* 基地址 */ MPU_REGION_SIZE_16KB, /* 长度 */ MPU_REGION_NUMBER4, MPU_INSTRUCTION_EXEC_PERMIT, /* NUMER4,允许指令访问 */ MPU_AP_FULL_ACCESS, /* 全访问 */ MPU_TEX_TYPE1, /* 类型扩展域1 */ MPU_ACCESS_NON_SHAREABLE, /* 禁止共用 */ MPU_ACCESS_NON_CACHEABLE, /* 禁止cache */ MPU_ACCESS_BUFFERABLE); /* 允许缓冲 */

自定义该部分后,对网络描述符 可以方便的按照字符定义,在配置时不用手动计算其大小。注意: ac5和ac6编译器有所区别,且总体大小不能超过16k

#if defined(GD32H7XX) #if defined (__CC_ARM) /*!< ARM compiler */ //__attribute__((section(".ARM.__at_0x30000000"))) enet_descriptors_struct rxdesc_tab[ENET_RXBUF_NUM]; /*!< ENET RxDMA descriptor */ //__attribute__((section(".ARM.__at_0x30000160"))) enet_descriptors_struct txdesc_tab[ENET_TXBUF_NUM]; /*!< ENET TxDMA descriptor */ //__attribute__((section(".ARM.__at_0x30000300"))) uint8_t rx_buff[ENET_RXBUF_NUM][ENET_RXBUF_SIZE]; /*!< ENET receive buffer */ //__attribute__((section(".ARM.__at_0x30002100"))) uint8_t tx_buff[ENET_TXBUF_NUM][ENET_TXBUF_SIZE]; /*!< ENET transmit buffer */ __attribute__((section(".sram0_nocache"),zero_init)); enet_descriptors_struct rxdesc_tab[ENET_RXBUF_NUM]; /*!< ENET RxDMA descriptor */ __attribute__((section(".sram0_nocache"),zero_init)); enet_descriptors_struct txdesc_tab[ENET_TXBUF_NUM]; /*!< ENET TxDMA descriptor */ __attribute__((section(".sram0_nocache"),zero_init)); uint8_t rx_buff[ENET_RXBUF_NUM][ENET_RXBUF_SIZE]; /*!< ENET receive buffer */ __attribute__((section(".sram0_nocache"),zero_init)); uint8_t tx_buff[ENET_TXBUF_NUM][ENET_TXBUF_SIZE]; /*!< ENET transmit buffer */ #elif defined ( __ICCARM__ ) /*!< IAR compiler */ #pragma location=0x30000000 enet_descriptors_struct rxdesc_tab[ENET_RXBUF_NUM]; /*!< ENET RxDMA descriptor */ #pragma location=0x30000160 enet_descriptors_struct txdesc_tab[ENET_TXBUF_NUM]; /*!< ENET TxDMA descriptor */ #pragma location=0x30000300 uint8_t rx_buff[ENET_RXBUF_NUM][ENET_RXBUF_SIZE]; /*!< ENET receive buffer */ #pragma location=0x30002100 uint8_t tx_buff[ENET_TXBUF_NUM][ENET_TXBUF_SIZE]; /*!< ENET transmit buffer */ #elif defined (__GNUC__) /* GNU Compiler */ //enet_descriptors_struct rxdesc_tab[ENET_RXBUF_NUM] __attribute__((section(".ARM.__at_0x30000000"))); /*!< ENET RxDMA descriptor */ //enet_descriptors_struct txdesc_tab[ENET_TXBUF_NUM] __attribute__((section(".ARM.__at_0x30000160"))); /*!< ENET TxDMA descriptor */ //uint8_t rx_buff[ENET_RXBUF_NUM][ENET_RXBUF_SIZE] __attribute__((section(".ARM.__at_0x30000300"))); /*!< ENET receive buffer */ //uint8_t tx_buff[ENET_TXBUF_NUM][ENET_TXBUF_SIZE] __attribute__((section(".ARM.__at_0x30002100"))); /*!< ENET transmit buffer */ enet_descriptors_struct rxdesc_tab[ENET_RXBUF_NUM] __attribute__((section(".sram0_nocache"))); /*!< ENET RxDMA descriptor */ enet_descriptors_struct txdesc_tab[ENET_TXBUF_NUM] __attribute__((section(".sram0_nocache"))); /*!< ENET TxDMA descriptor */ uint8_t rx_buff[ENET_RXBUF_NUM][ENET_RXBUF_SIZE] __attribute__((section(".sram0_nocache"))); /*!< ENET receive buffer */ uint8_t tx_buff[ENET_TXBUF_NUM][ENET_TXBUF_SIZE] __attribute__((section(".sram0_nocache"))); /*!< ENET transmit buffer */ #endif /* __CC_ARM */

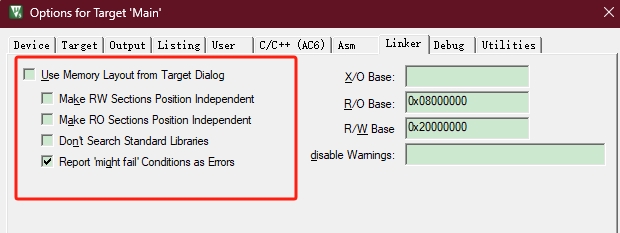

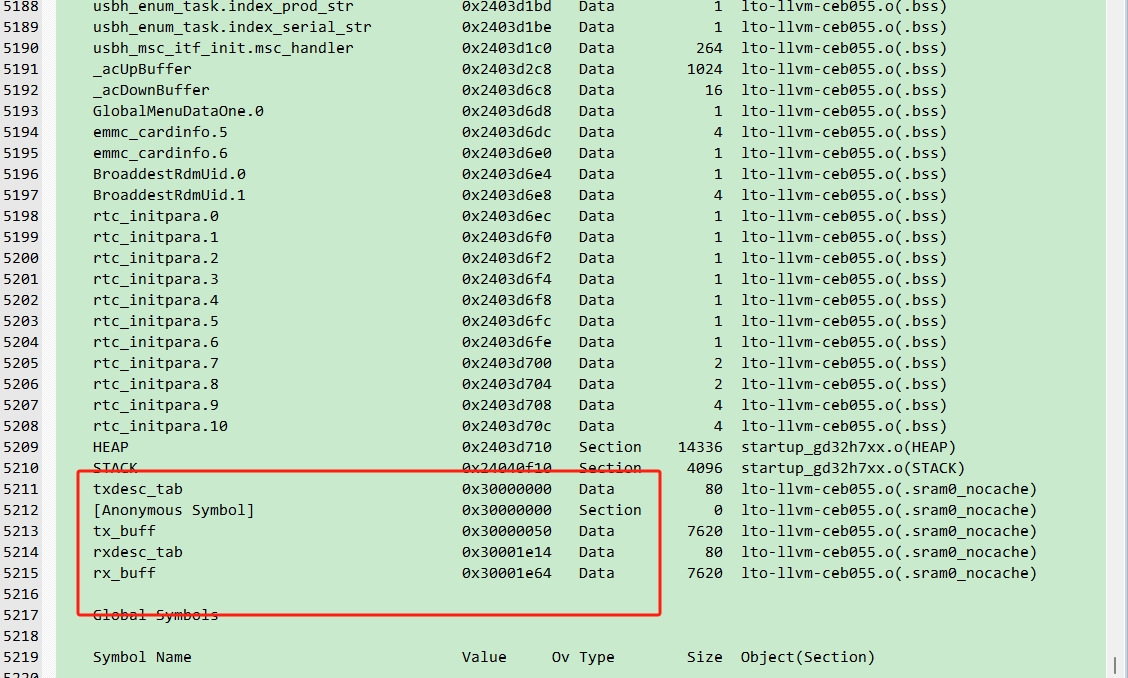

编译后查看 map 分配文件:

确实分配到了 RW_RAM2 区域。这样使用芯片的另外一个mac 就可以分配到 RW_RAM3 ,或者也可将其他不需要cache的变量分配到该区域。

2.其片上 SRAM 存储器配置详述:

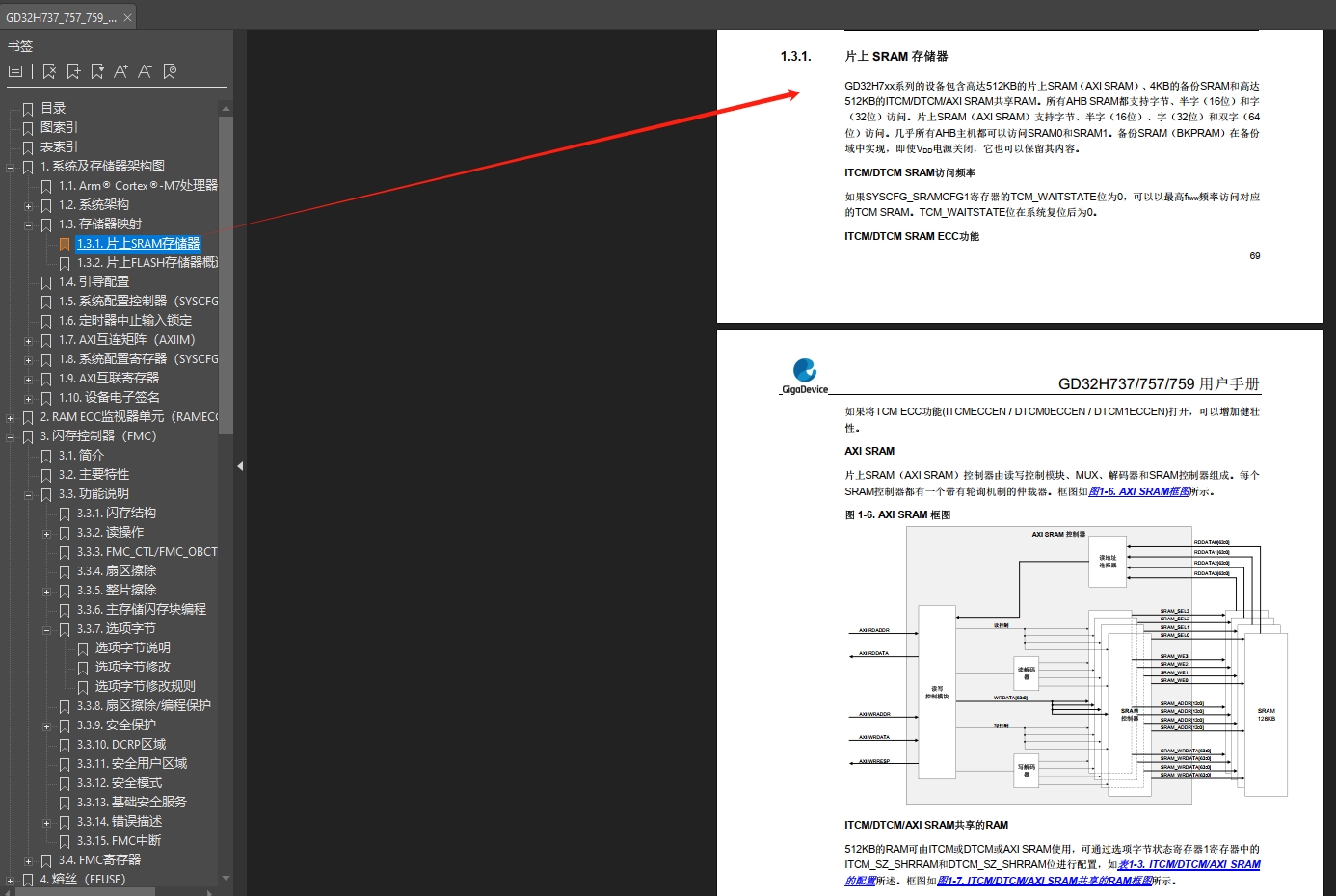

GD32H7xx系列的设备包含高达512KB的片上SRAM(AXI SRAM)、 4KB的备份SRAM和高达512KB的ITCM/DTCM/AXI SRAM共享RAM。

所有AHB SRAM都支持字节、半字(16位)和字(32位)访问。片上SRAM(AXI SRAM)支持字节、半字(16位)、字(32位)和双字(64位)访问。

几乎所有AHB主机都可以访问SRAM0和SRAM1。备份SRAM(BKPRAM)在备份域中实现,即使VDD电源关闭,它也可以保留其内容。

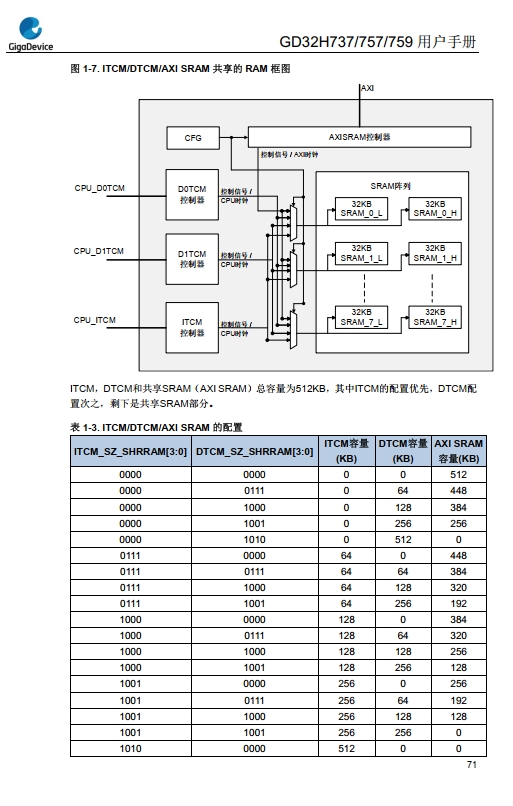

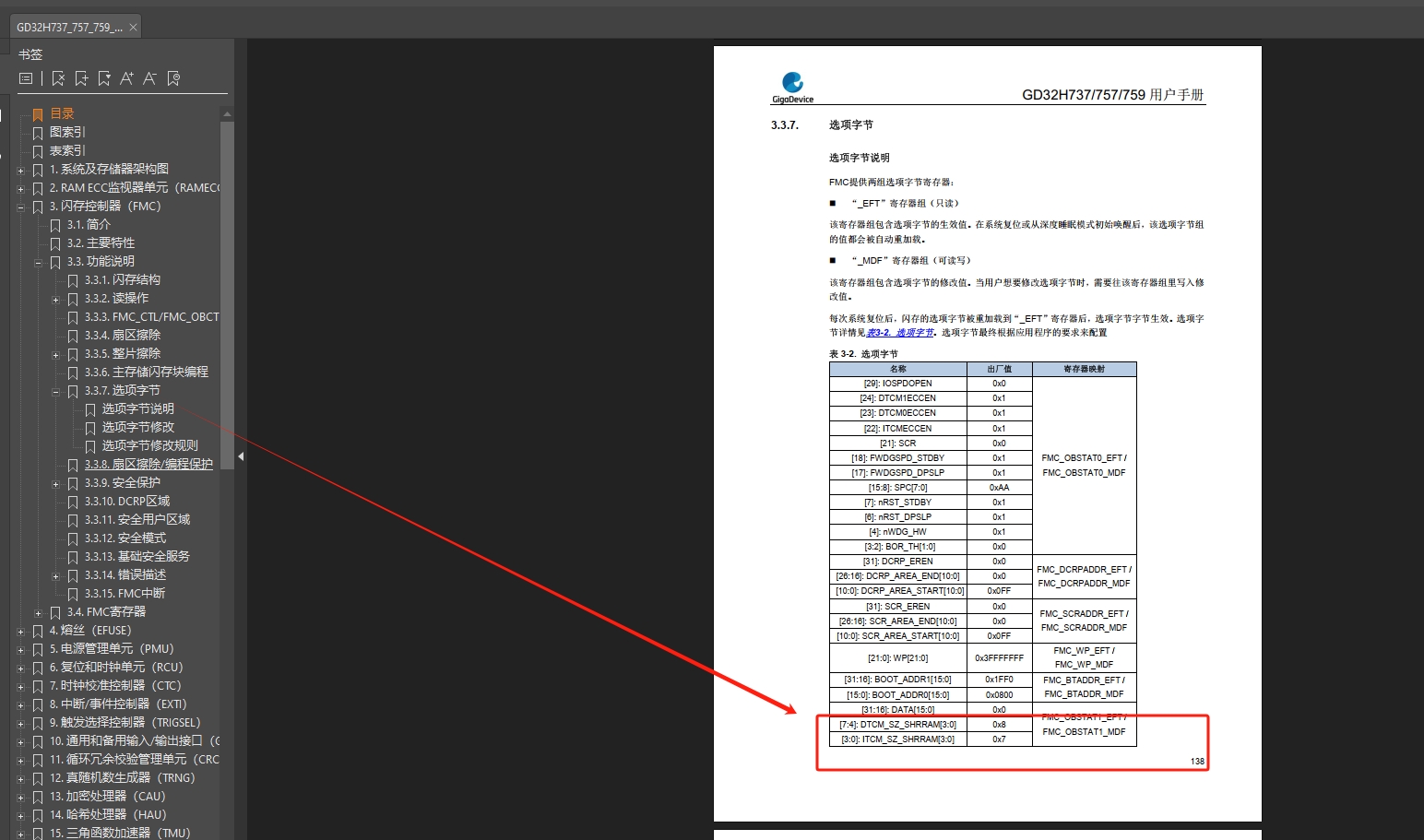

查看该部分选项字默认参数:

可知该MCU默认 ITCM为64k,DTCM为128k。

2.1 其内部分配的详细地址分配如下:

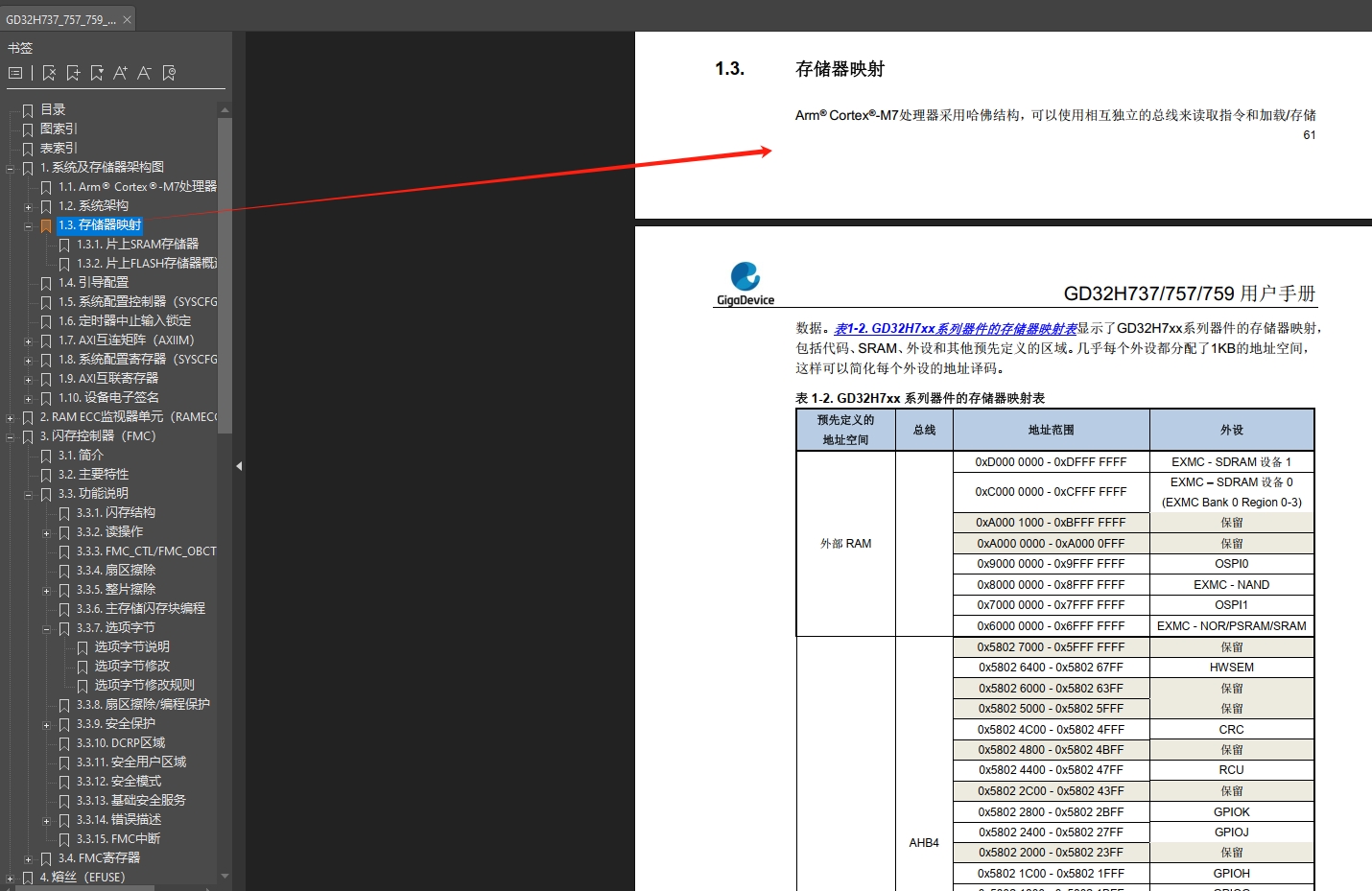

2.1.1 外部 RAM:

2.1.1 内部 RAM:

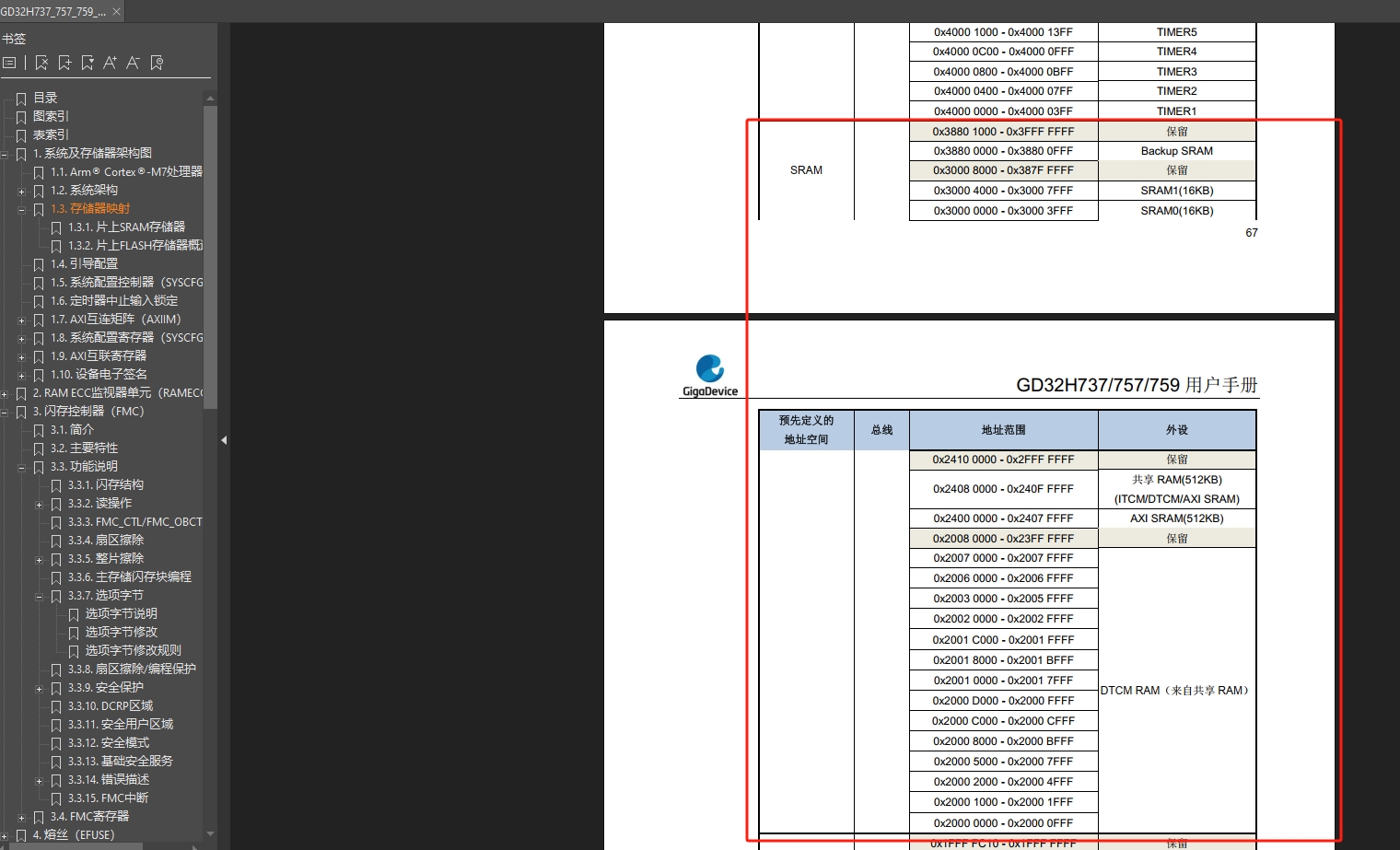

该部分包括SRAM0,SRAM1。这两个地址联系,可以直接当作一款连续的内存使用;

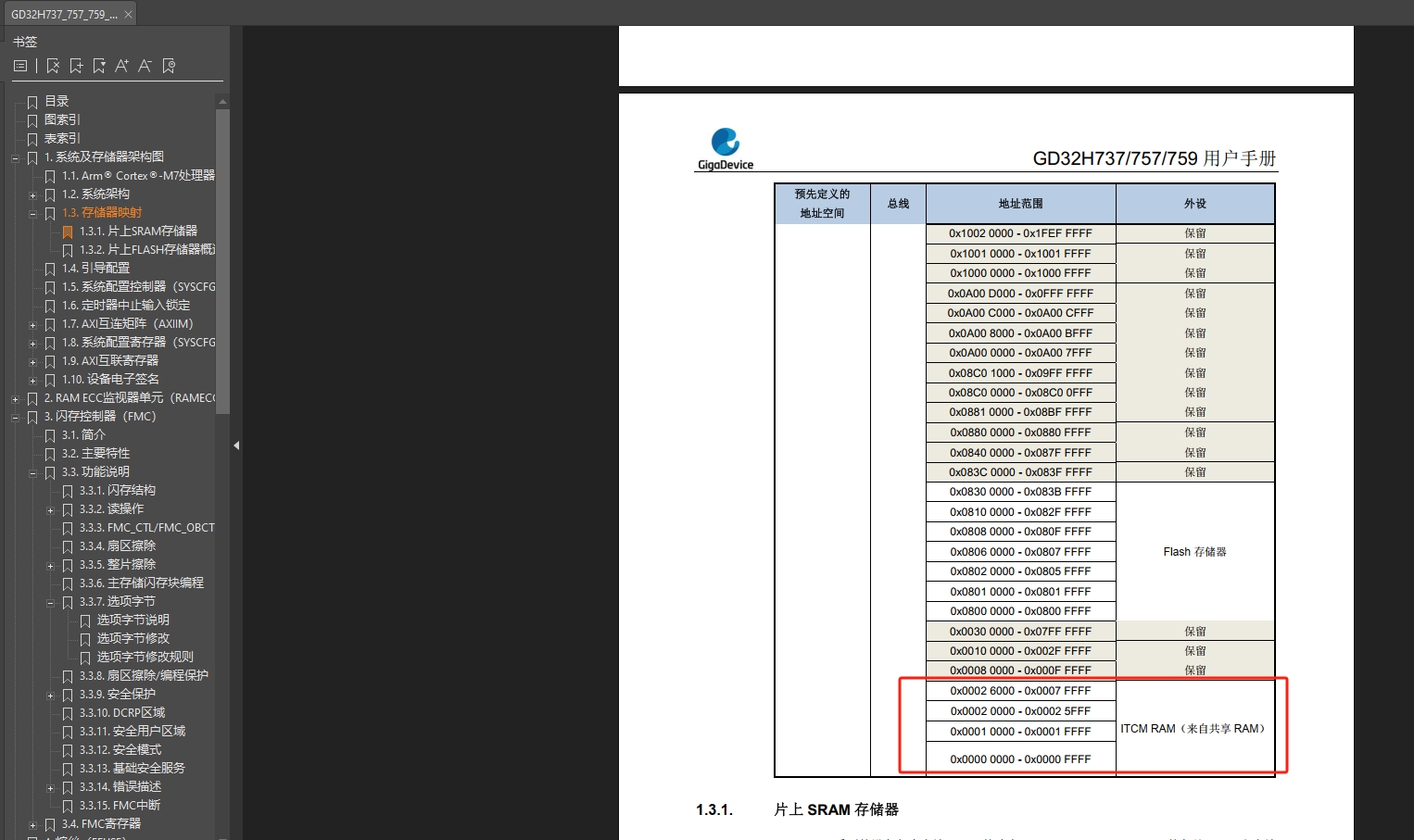

共享RAM,为 ITCM+DTCM共享使用,和地址0x2000 0000 映射DTCM与 0x0000 0000 映射ITCM相关;

AXI SRAM 为独立RAM.

最后一部分为ITCM 来自上述的共享RAM。

本文来自博客园,作者:求隐,转载请注明原文链接:https://www.cnblogs.com/duguqiuying/articles/17899214.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· 三行代码完成国际化适配,妙~啊~

· .NET Core 中如何实现缓存的预热?