sd和emmc如何进行tuning

2、在写操作时,时钟和数据方向是一致的,因此写数据可以由 SDCLK 同步进行传输而不用关心传输线延时

3、在读操作时,时钟方向和数据方向是相反的,主机接收的读数据被往返延时(round-trip delay) ,输出延时以及卡和主机的延时所延迟。

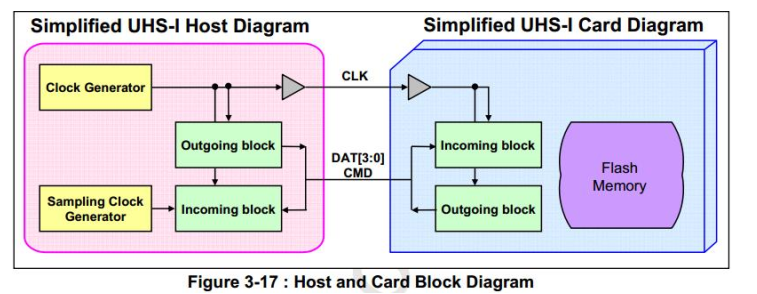

所以主机关键之处在于数据的接收,主机需要具有一个采样时钟发生器,用来接收响应, CRC 状态以及读数据块

通过前面的描述知道,在接收数据的时候,clk和数据之间有延时,所以需要调整这个延时,获取到最佳的采样点

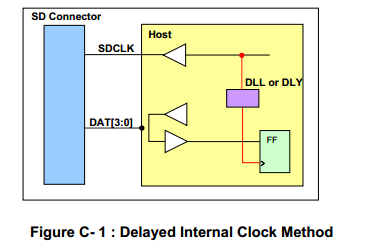

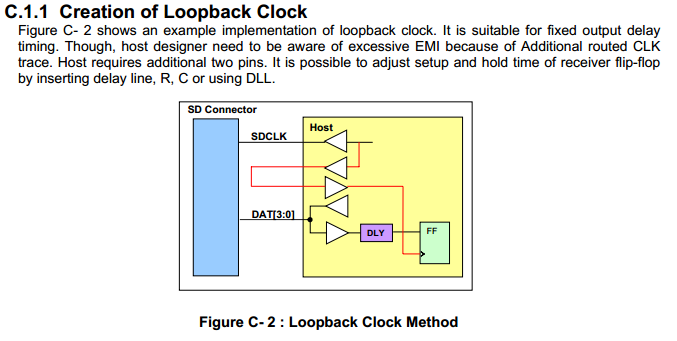

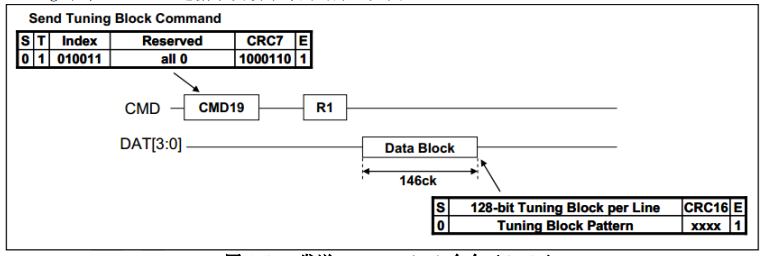

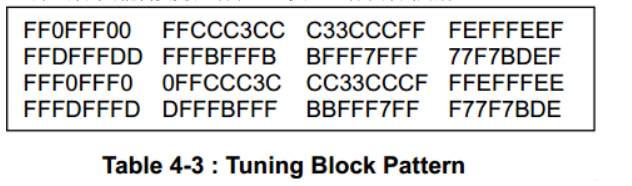

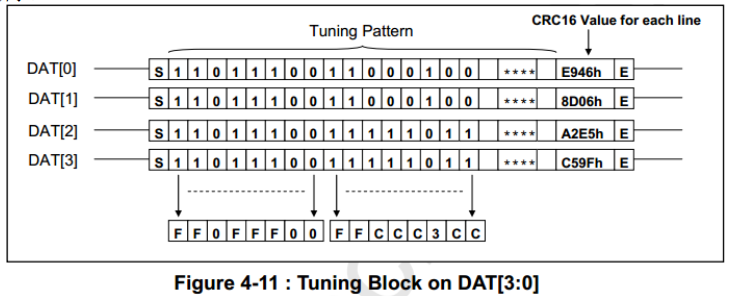

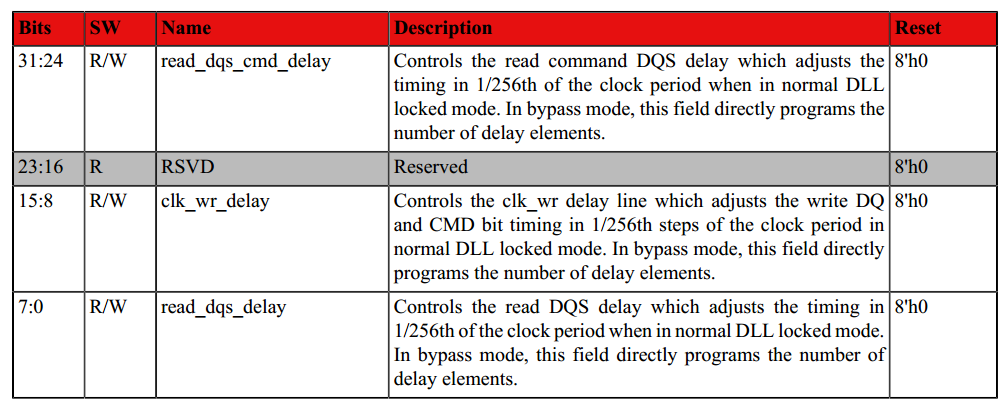

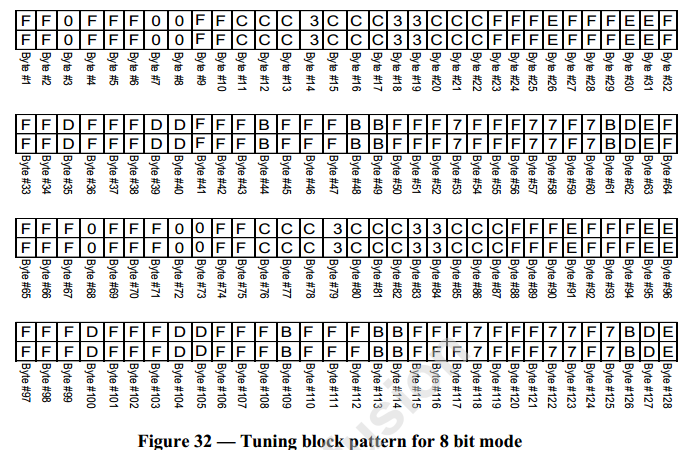

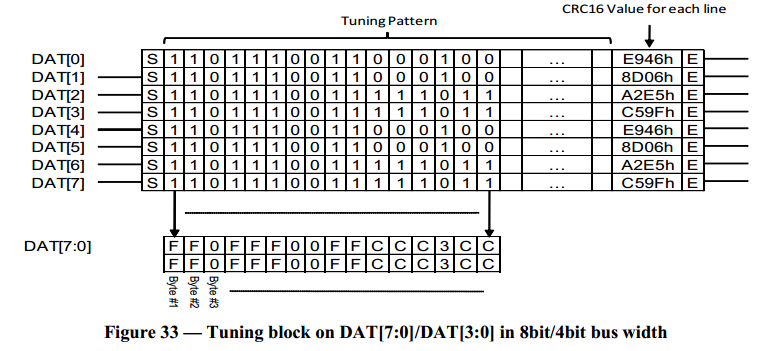

1、主机使用一个可变采样时钟发生器来决定采样点。主机可以通过 CMD19 tuning 命令读取预先定义并保存在卡中的 tuning block,用来辅助找到采样点。

2、该方法可以用于所有频率范围。当频率为低于 25MHz 的低频时,主机不需要 tuning 就可访问卡。

一般应该都是使用的方法1,而且方法1紫色的延时是自动调整的,不需要软件干预

2、SDR50可以选择是否进行tuning,通过SRS17.UTSM50(use tuning for SDR50)进行确认是否需要tuning(1需要,0不需要)\

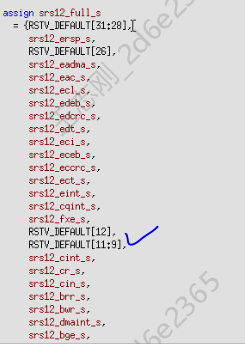

3、cdns的ip没有SRS12_RETUNING_EVENT这个功能,通过看rtl该功能被屏蔽,12bit没有使用,文档上确实也没有

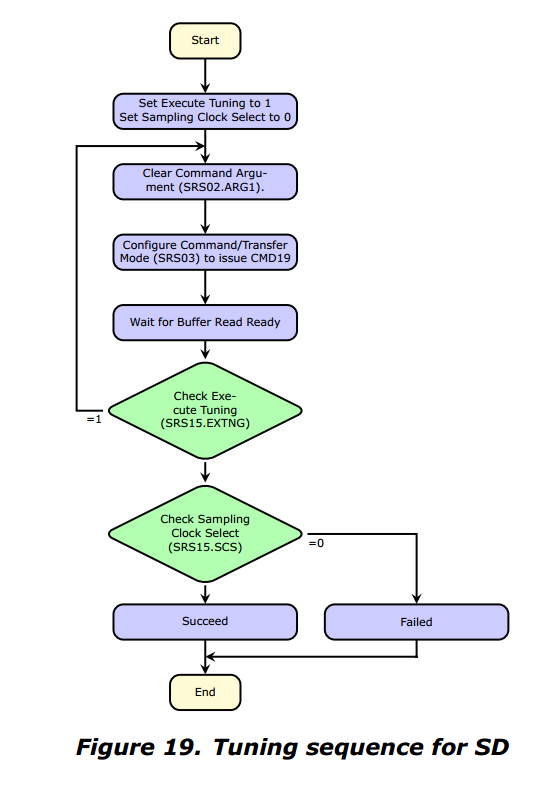

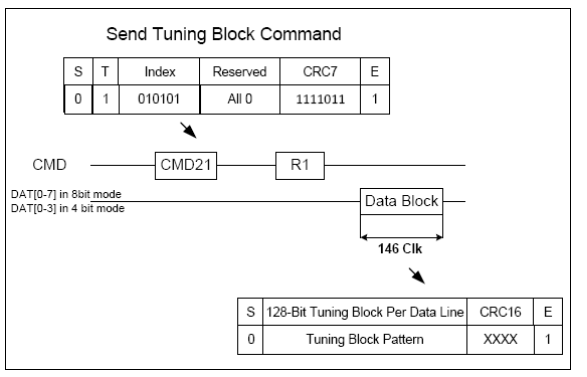

(1)SRS15.SCS(Sampling clock select)清0

该bit为1代表tuning流程成功完成,否则流程失败,并且tunling逻辑的clk会关闭

(2)SRS15.EXTNG(Execute Tuning) 置1

SCS = 0, EXTNG = 0 - Reset and disable clock tuning logic

SCS = 0, EXTNG = 1 - Reset and restart tuning process

SCS = 1, EXTNG = 0 - Stop tuning procedure

SCS = 1, EXTNG = 1 - Start retuning (without clock tuning logic reset)

配置为0,1即Reset and restart tuning process

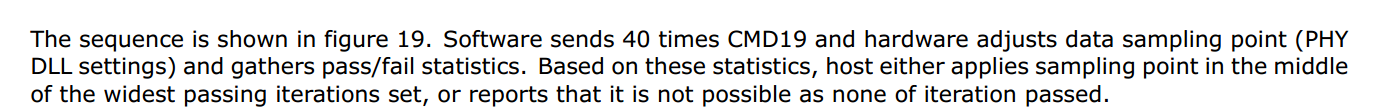

判断SRS15.EXTNG的值是否为1,如果为1,循环执行40次,每次发送CMD19命令,判断CMD19是否执行成功

如果40次完成或者CMD19失败,或者SRS15.EXTNG为0,均会退出40次的循环

如果40次成功执行,并且SRS15.SCS为1,则sd卡的tuning成功,否则失败

CMD19需要在1.8V的transfer状态下且卡处于unlock状态下发送,其他情况下是非法的。

通过上面的流程,phy是怎么调整采样点的?自动调整的吗?上面的流程看软件并没有修改phy寄存器

(1)HS200,HS400需要进行tuning,HS400ES不需要tuning

(2)HS400当需要tuning是需要调用mmc_hs400_to_hs200切换到hs200进行tuning

执行完成后再调用mmc_hs200_to_hs400进行恢复

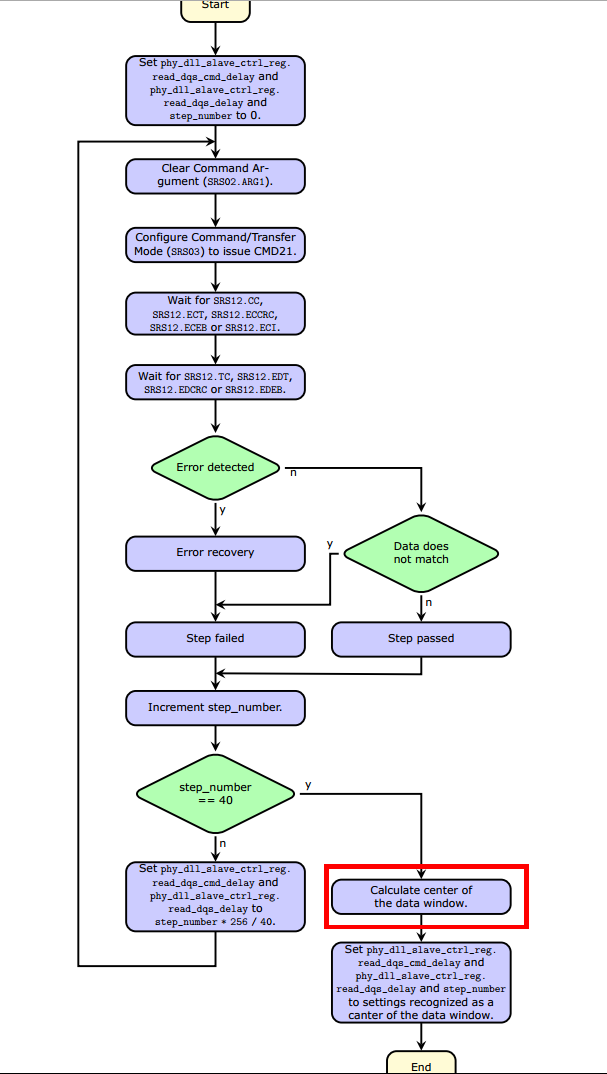

(3)从cdns的寄存器看,tuning主要是配置dqs的延时,但是HS200和HS400并没有strobe信号,是怎么生效的呢?

从phy手册看,DQS有3种来源,1是外部strobe,2是phony dqs, 3是lpbk_dqs(推荐),如果没有strobe信号,可以使用另外两个内部的信号,所以HS200和HS400应该调整的是内部的延时,个人理解在tuning只在read的时候才需要,因为read的时候数据和cmd是dvice发送过来的,clk也是参考的device,所以对host来说data和cmd跨时钟域了,所以需要调整内部的lpbk_dqs去适配clk

但是调整之后,host和device的clk可能有偏移,所以需要定时的tuning才行

发送40次后,会参数40个结果,1代表成功,0代表失败,找到1最多的地方,并且取中间值,对应的pos就是最佳参数,把该参数进行赋值到对应的寄存器中

浙公网安备 33010602011771号

浙公网安备 33010602011771号