牛客网刷题4

25-28

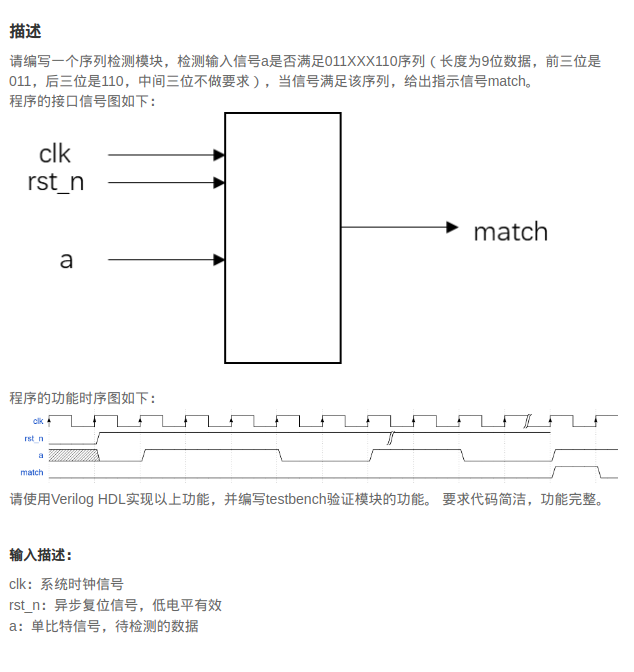

25题

输入序列连续的序列检测_牛客题霸_牛客网 (nowcoder.com)

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [8:0] tmp;

//存储

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

tmp <= 0;

end

else begin

tmp <= {tmp[7:0],a};

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

match <= 0;

end

else if (tmp == 9'b01110001) begin

match <= 1;

end

else begin

match <= 0;

end

end

endmodule

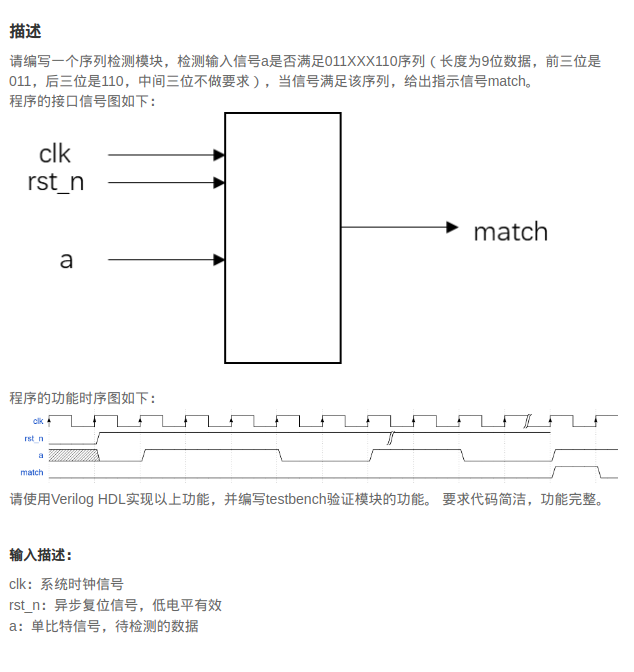

26题

含有无关项的序列检测_牛客题霸_牛客网 (nowcoder.com)

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [8:0] tmp;

//存储

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

tmp <= 0;

end

else begin

tmp <= {tmp[7:0],a};

end

end

wire flag;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

match <= 0;

end

else if (flag) begin

match <= 1;

end

else begin

match <= 0;

end

end

assign flag = tmp[8:6] == 3'b011 && tmp[2:0] == 3'b110;

endmodule

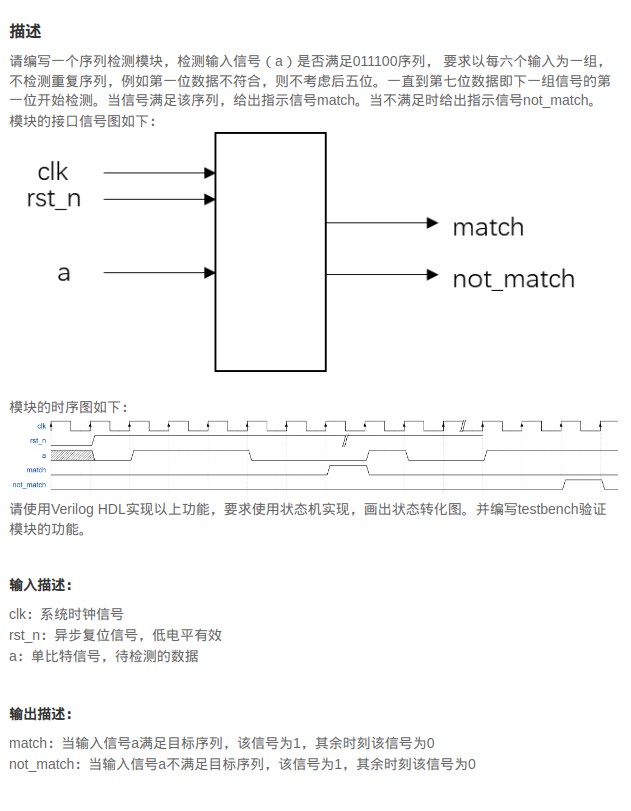

27题

不重叠序列检测_牛客题霸_牛客网 (nowcoder.com)

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

//计数器

reg [2:0] cnt;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt <= 0;

end

else begin

if (cnt == 5) begin

cnt <= 0;

end

else begin

cnt <= cnt + 1;

end

end

end

reg [5:0] tmp;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

tmp <= 0;

end

else begin

tmp[5-cnt] <= data;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

match <= 0;

not_match <= 0;

end

else if(tmp == 6'b011100 && cnt == 5) begin

match <= 1;

not_match <= 0;

end

else if(tmp != 6'b011100 && cnt == 5) begin

match <= 0;

not_match <= 1;

end

else begin

match <= 0;

not_match <= 0;

end

end

endmodule

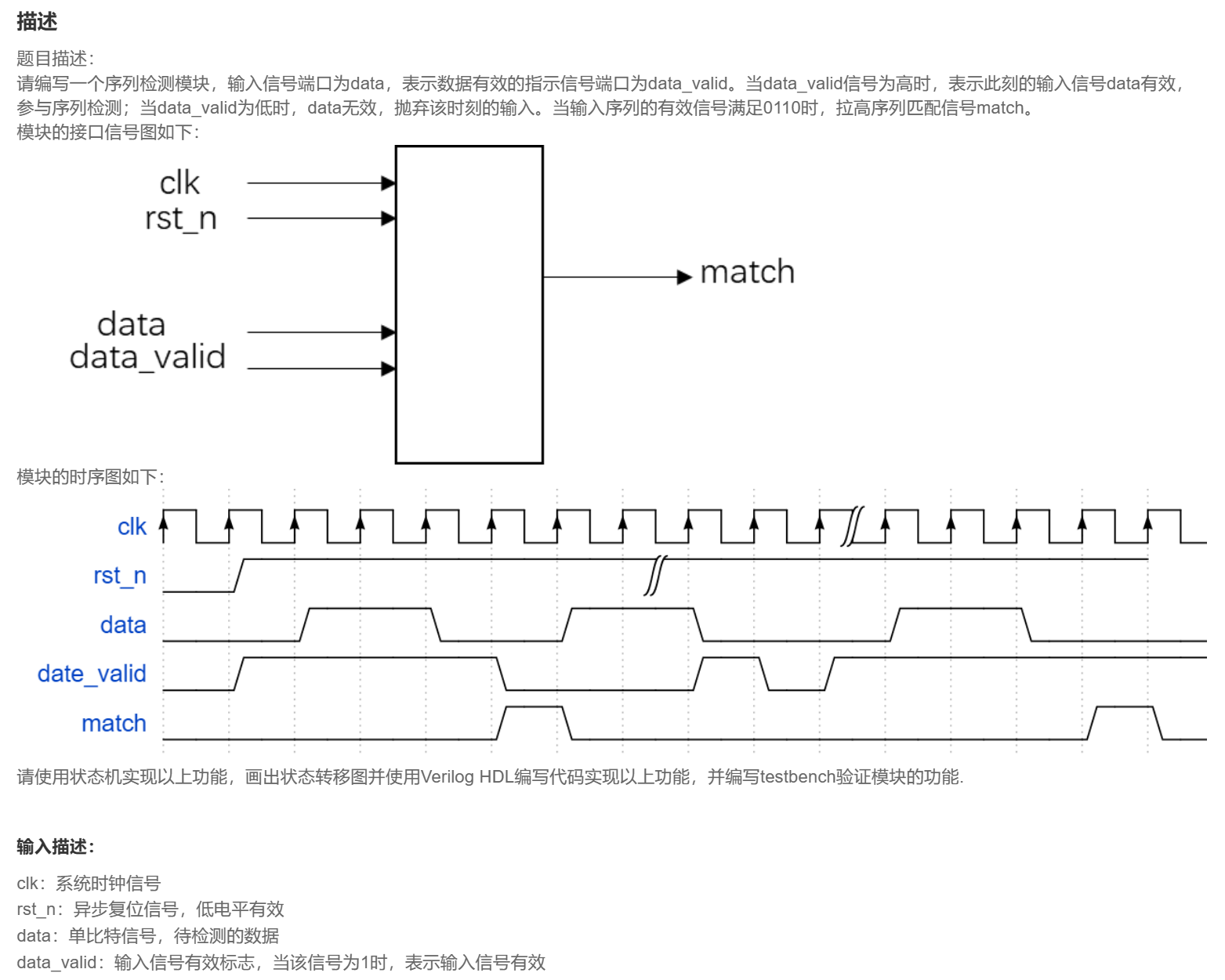

28题

输入序列不连续的序列检测_牛客题霸_牛客网 (nowcoder.com)

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg [3:0] tmp;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

tmp <= 0;

end

else if(data_valid) begin

tmp <= {tmp[2:0],data};

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

match <= 0;

end

else if(tmp[2:0] == 3'b011 && data_valid && data == 0) begin

match <= 1;

end

else begin

match <= 0;

end

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号