时序约束1——建立时间、保持时间、建立余量的概念

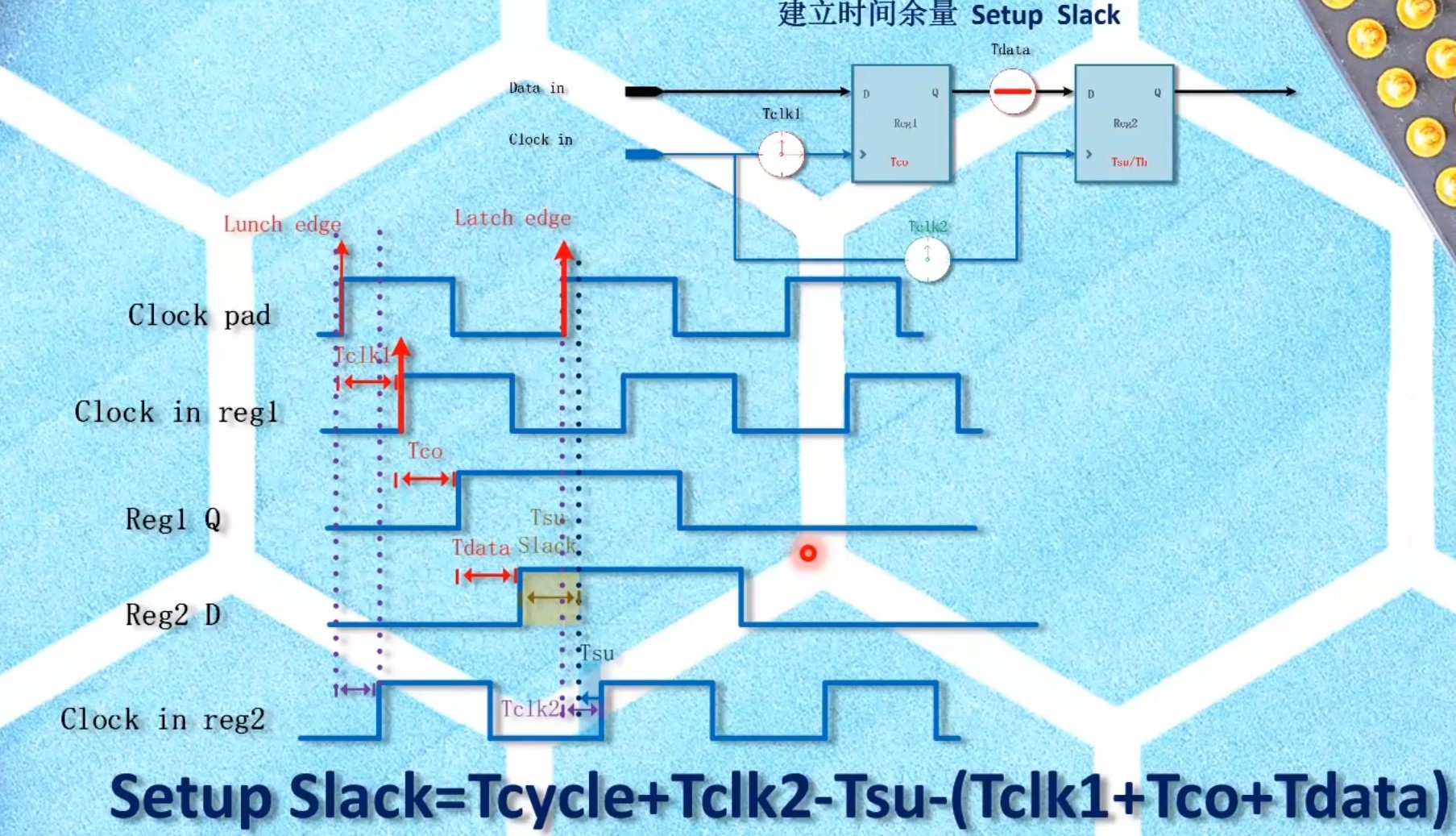

数据到达时间: Tclk1+Tco+Tdata

建立时间: Tcycle+Tclk2-Tsu

建立时间余量: 建立时间 - 数据到达时间

小问题:

注意的点:PinPLL是clock pad路径 是共同经过的路径 ,可以同时加入进去。也可以不计算进去 Fmax 指的是始终周期最小时候的Tcycle多少,也就是建立时间余量为0的时候 是时钟频率最快的时候。

建立时间余量由上面的公式给出:

Tclk1+Tco+Tdata-(Tcycle+Tclk2-Tsu)=4.5ns

Fmax也就是 当建立时间余量 Setup Slack为0的时候。也就是时钟频率的最大值。

Fmax=1/(Tcycle-Setup Slack)=1/(10-4.5)

一次简单的时序约束需要很长的时间

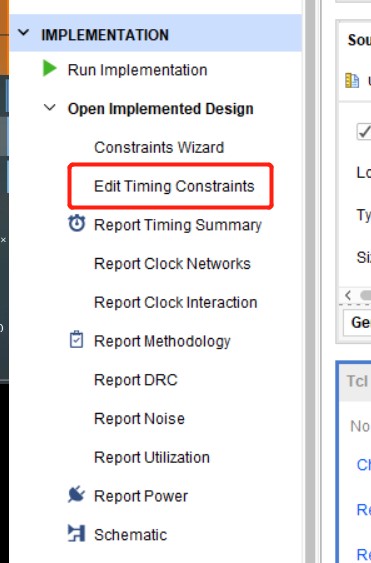

工程文件中,进行时序约束的方法。

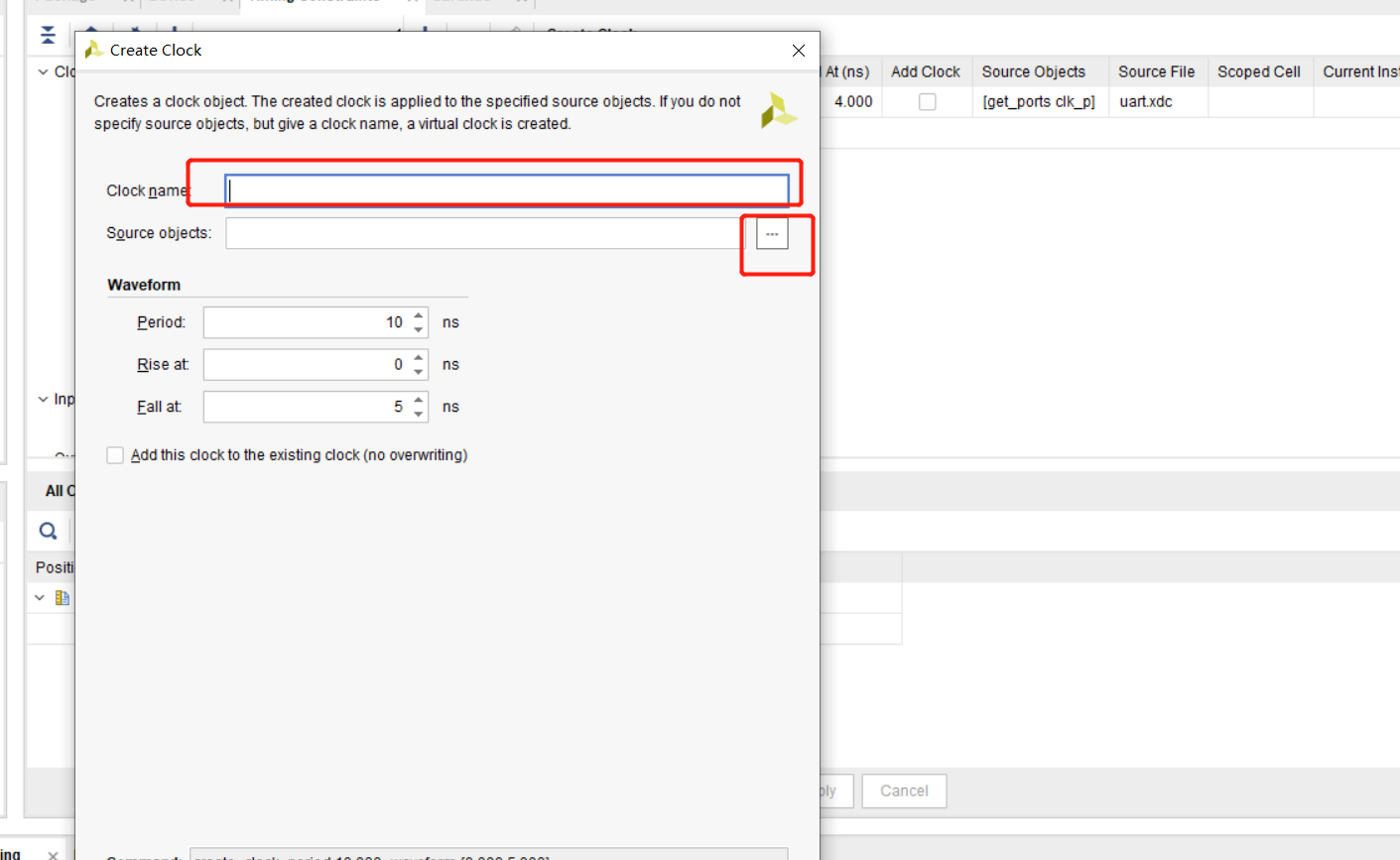

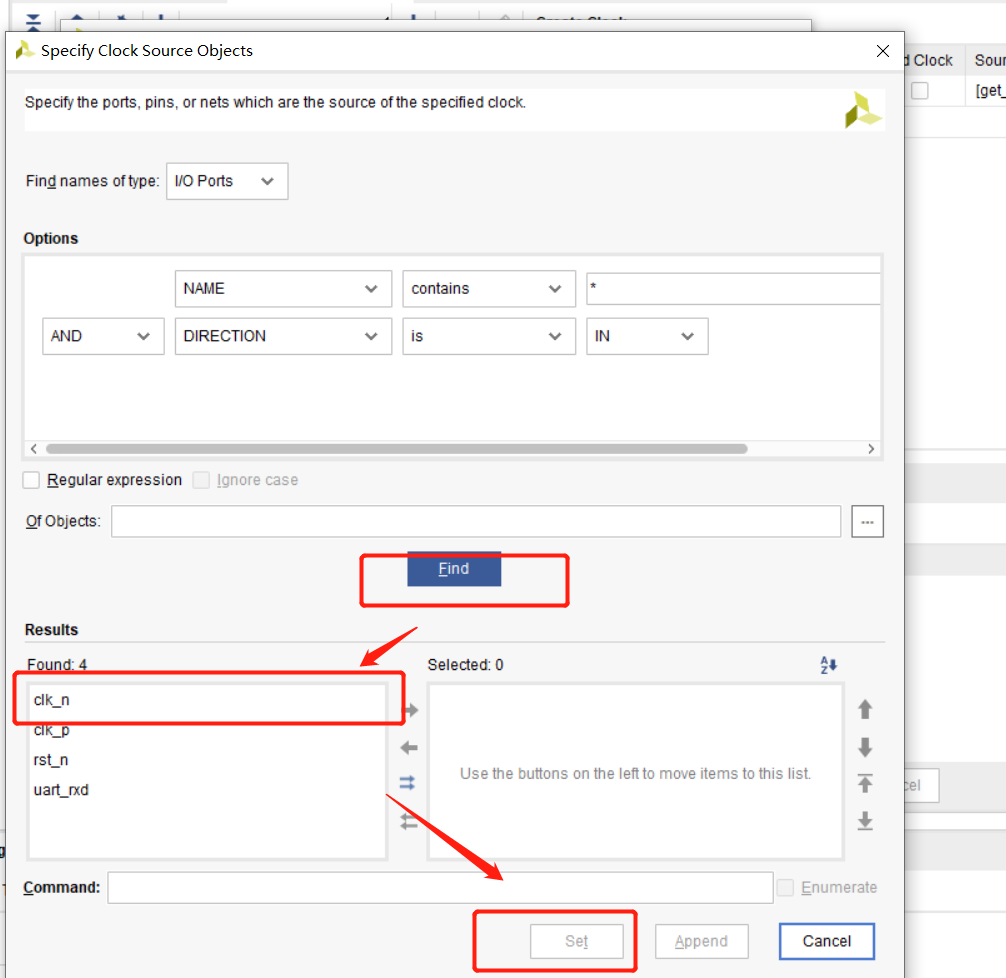

第一步在实现中点击进行时序约束

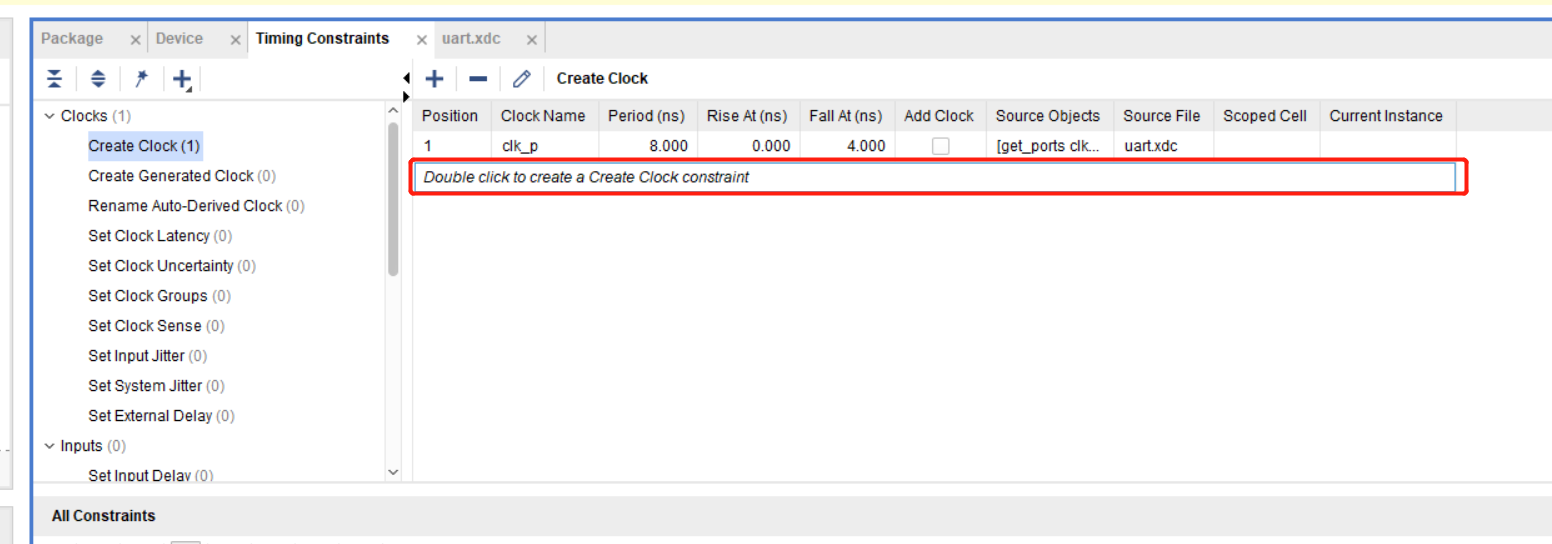

如何查看相关的时序报告(随便建立一个工程文件,写一个先关的带有寄存器的代码)

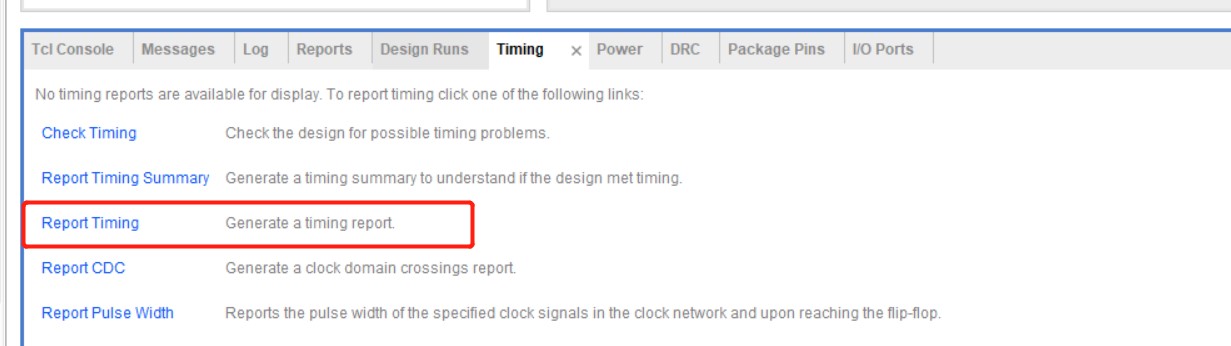

前三个分别是检查相关时序,查看时序的总结报告,以及单独的每一个路径的时序报告

第三个可以单独分析每一个时序路径

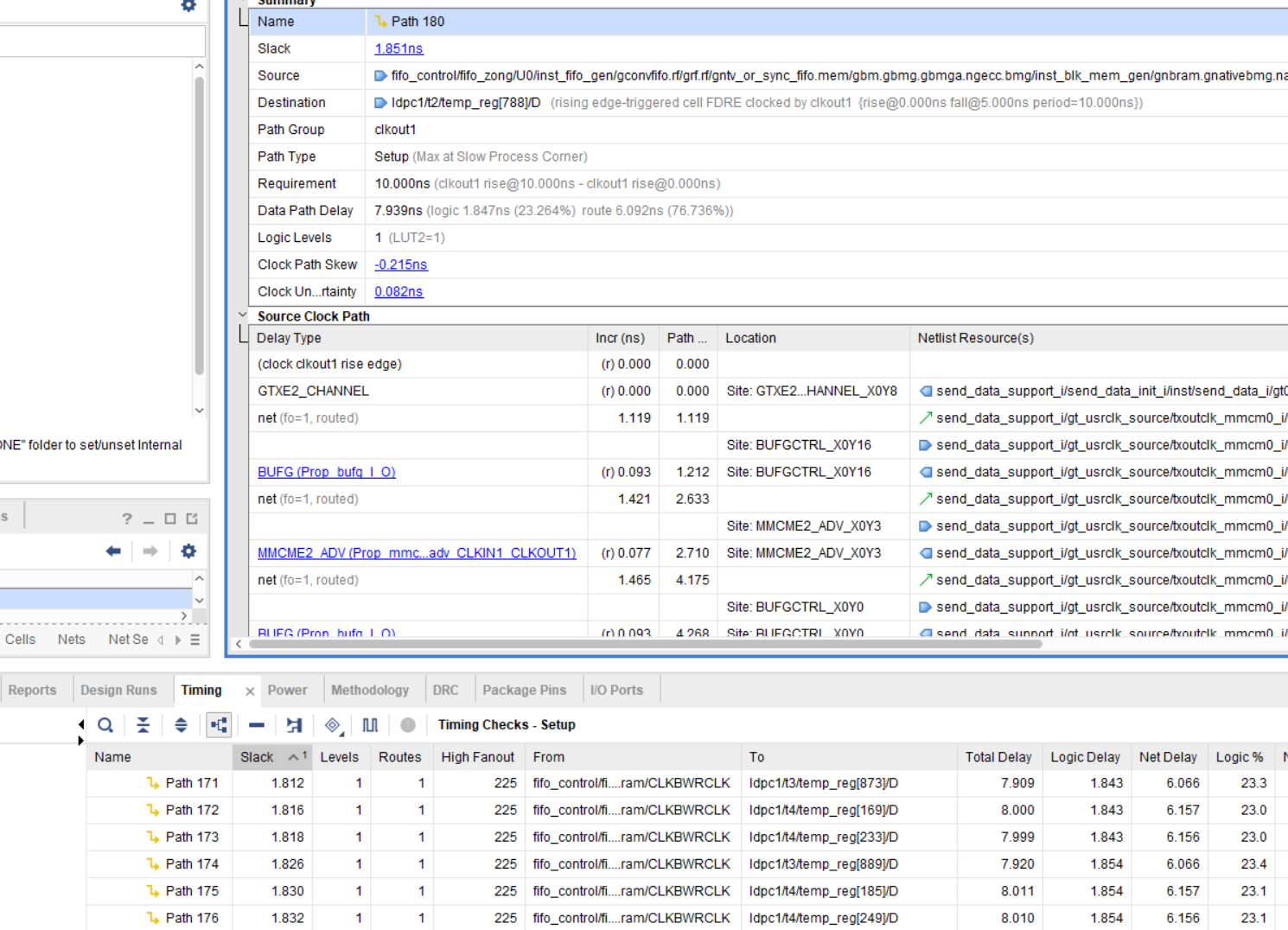

得到的情况如图所示

时钟偏斜: Tclk2目的的采样的时钟的延时减去 Tclk1 用来描述时钟的抖斜偏斜

浙公网安备 33010602011771号

浙公网安备 33010602011771号