分三个模块介绍GTX收发器的原理

首先是时钟篇

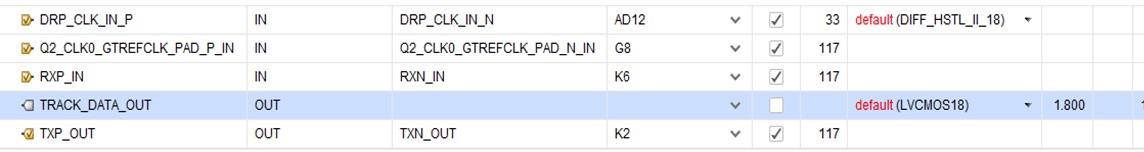

GTX收发器主要的时钟输入有四个

①input wireQ2_CLK1_GTREFCLK_PAD_N_IN,

②input wireQ2_CLK1_GTREFCLK_PAD_P_IN,

③input wire DRP_CLK_IN_P,

④input wire DRP_CLK_IN_N,

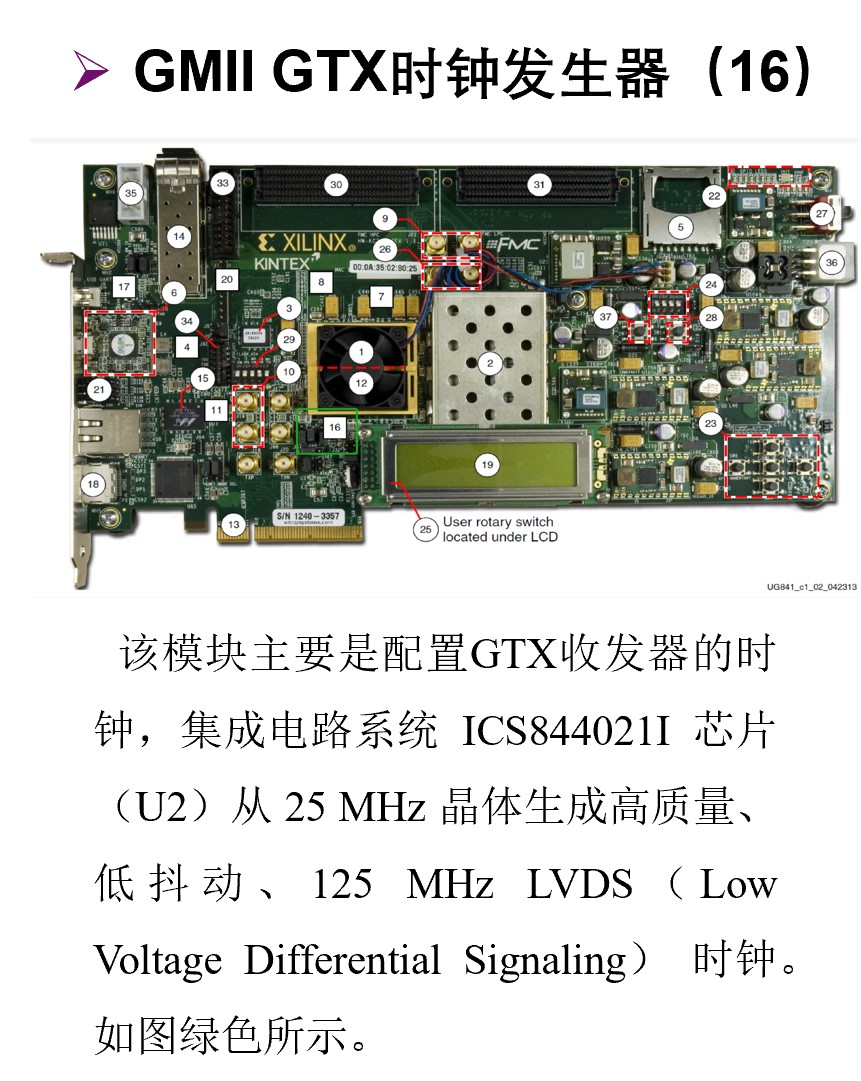

前两个是125M的GMII时钟,用来gtx_common生成QPLLOUTCLK_OUT 和QPLLOUTREFCLK_OUT(后文的2---GMII时钟)

后两个是200M系统时钟用来控制gtx_gt_usrclk_source.v文件生成TXUSRCLK和TXUSRCLK2(后文的1---系统时钟)

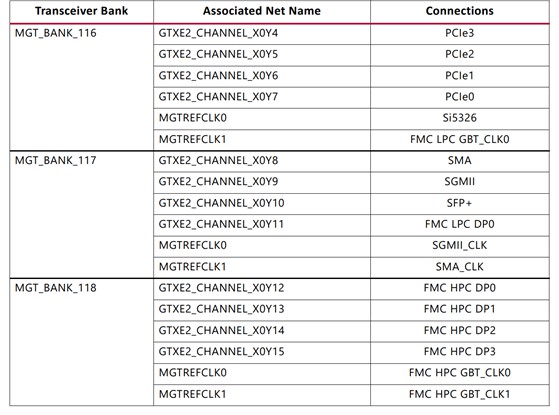

我们使用的开发板为FPGA:XC7K325T-2FFG900

这个板子的时钟资源有四个

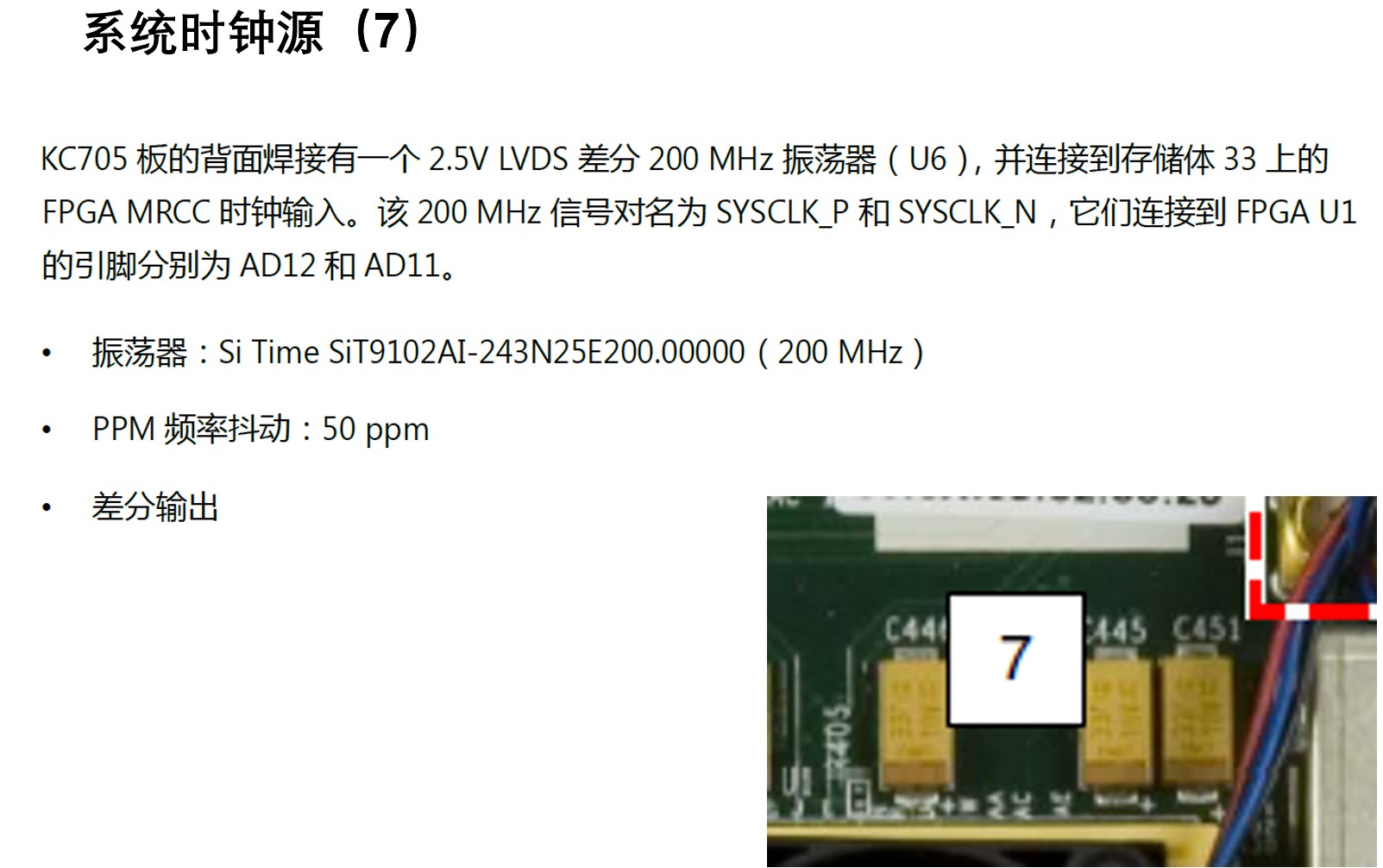

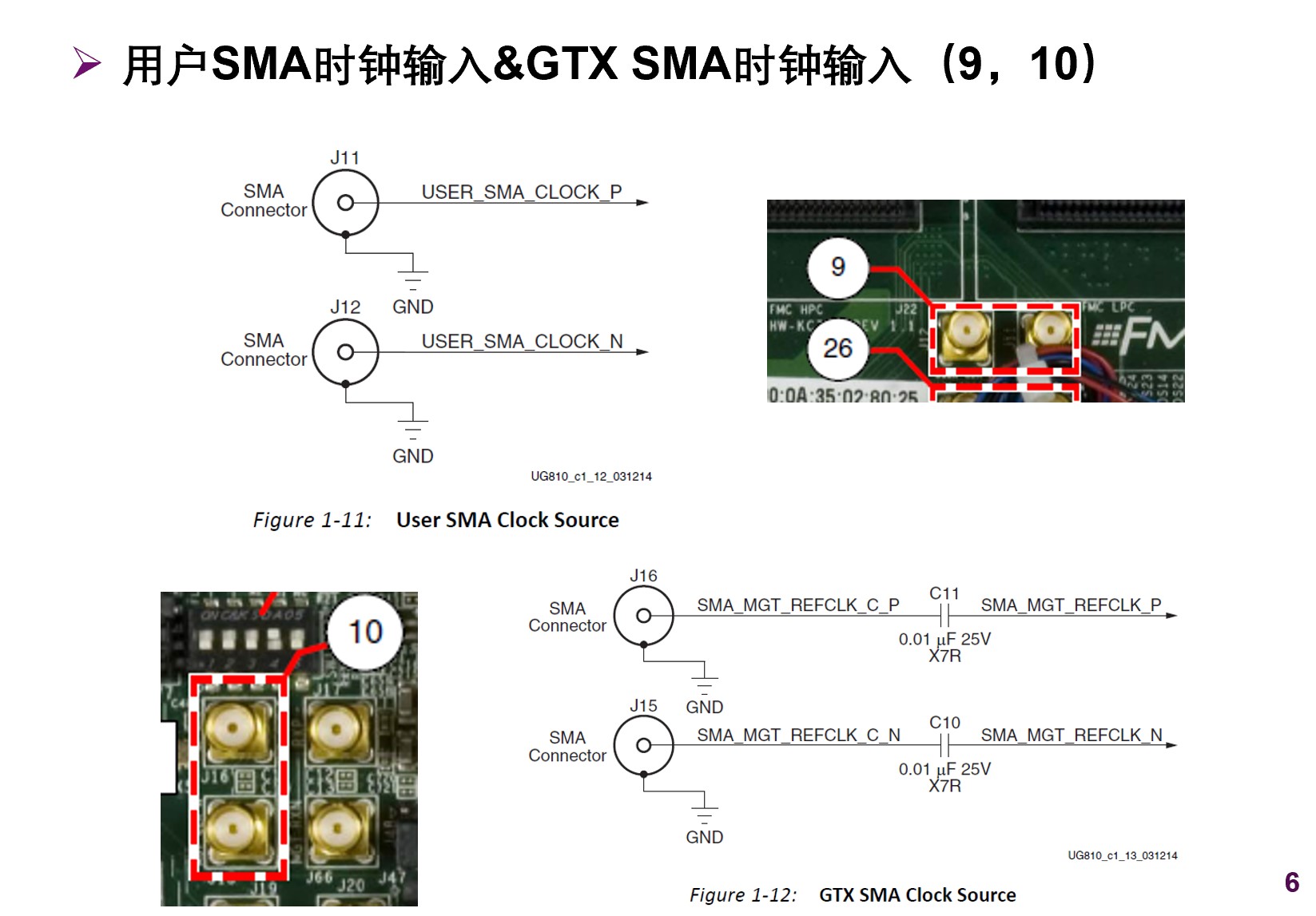

1.系统时钟

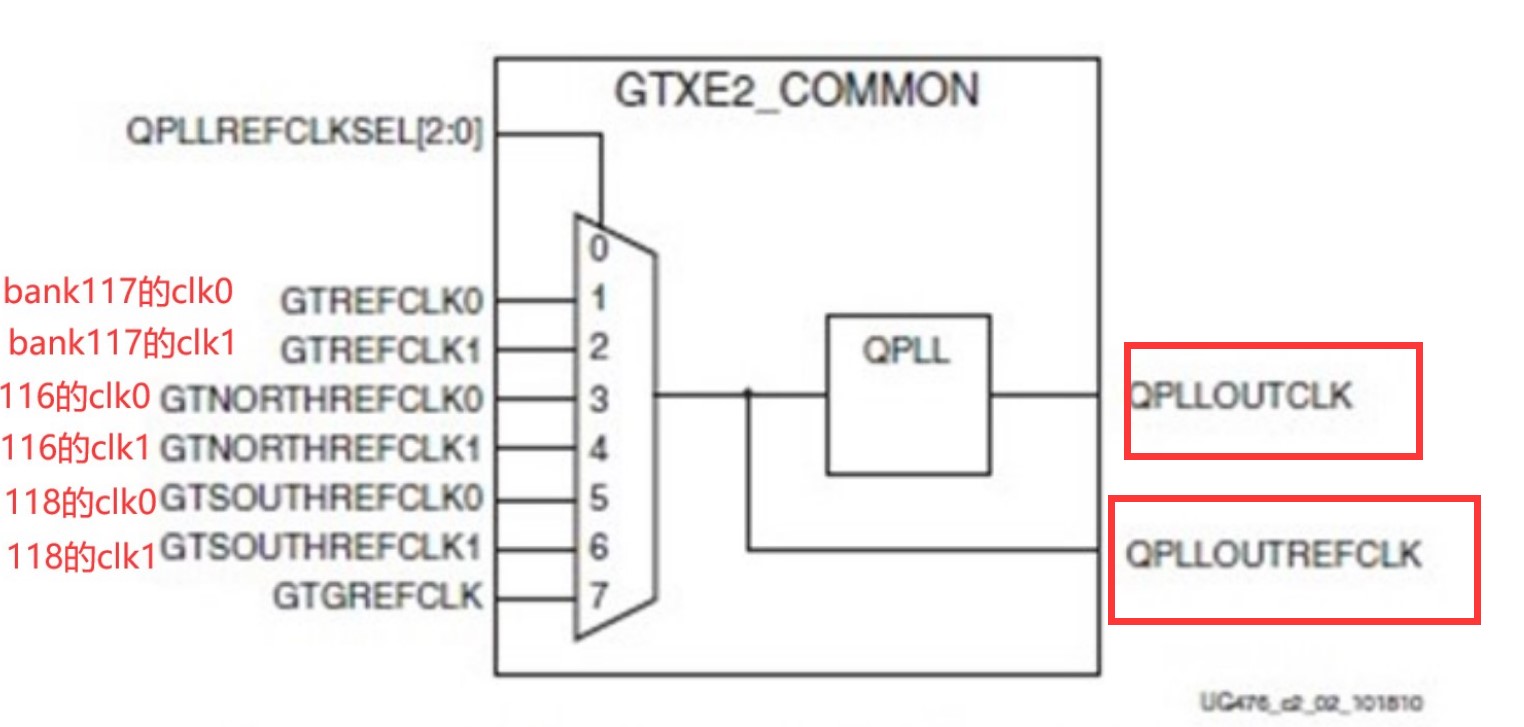

XC7K325具有16个GTX的通道,按照bank进行划分,一个bank中有4个独立的GTX通道,每个bank (Quad)拥有两个参考时钟Pin,也可以从上下两个Quad中获得参考时钟。(以bank117举例,其可用时钟为MGTREFCLK0--SGMII时钟,MGTREFCLK1--SMA时钟,还可以时钟上下bank116\118的时钟,116的成为南向时钟,118成为北向时钟)

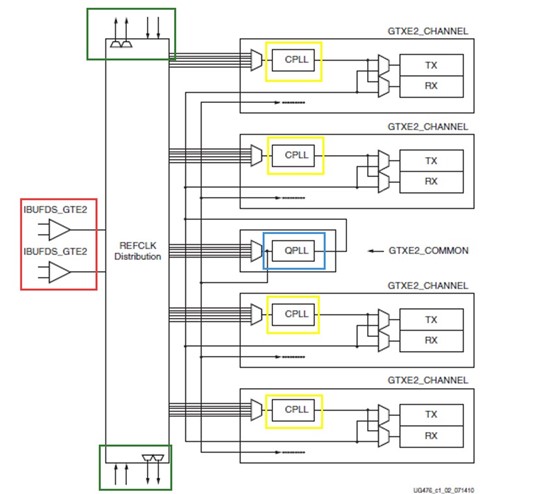

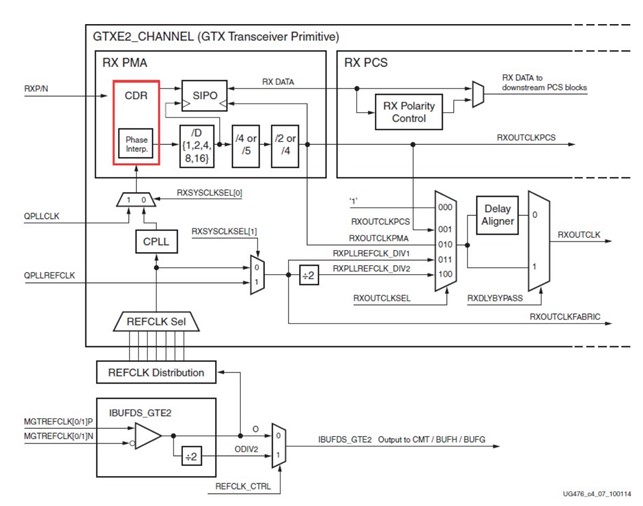

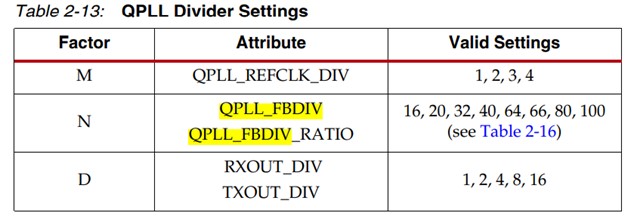

XC7K325的GTX时钟如下所示,红色方框部分是两个差分参考时钟输入,每个外部参考时钟的输入必须经过IBUFDS_GTE2源语之后才能使用。绿色方框是来自其他Quad的参考时钟输入,7系列FPGA支持使用相邻(南北方向)Quad的参考时钟作为当前Quad的参考时钟,多路参考时钟源经过一个选择器之后,分两路进入QPLL和CPLL,

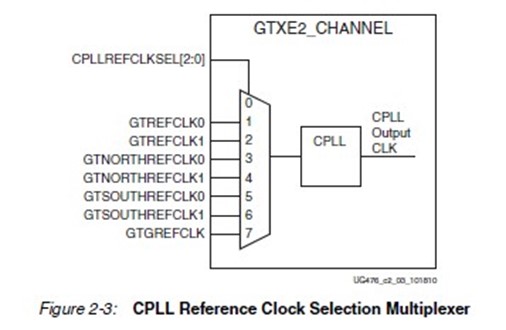

路参考时钟源如何经过一个选择器进入CPLL和QPLL呢?主要利用一个多路选择器,QPLLREFCLKSEL,如3b'001为选择GEREFCLK0进入QPLL

CPLL同理不做介绍

QPLL和CPLL的区别,在于两者支持的线速率不同,对于CPLL来说,支持的线速率位1.6GHz到3.3GHZ之间,而对于QPLL来说,GTX支持的线速率分两档,Lower

Baud支持5.93GHz~8.0GHz,Upper Baud支持9.8GHz~12.5GHz

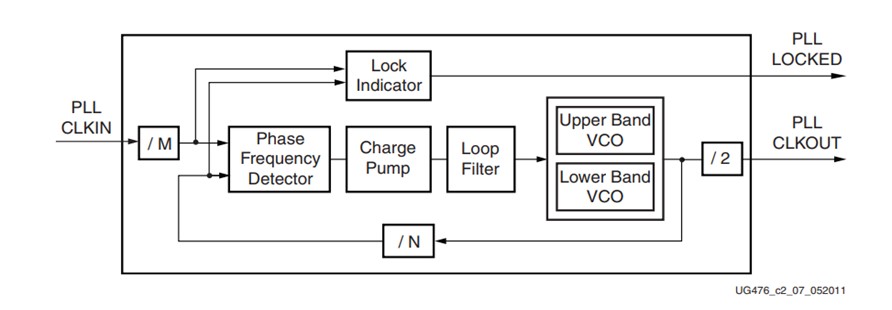

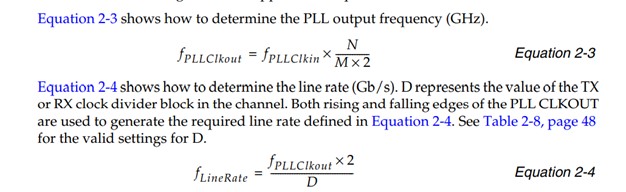

输入信号为125mhz,但是QPLL支持输出的线速率为12.5GHZ,那么信号的频率是如何改变的呢?信号通过多路选择器,经过分频器M和倍频器N进行倍频。然后根据官网手册的计算公式得到相关的线速度。表2-3说明了如何通过代码控制M\N和D。

这样,我们的时钟就从GMII那个固定的时钟,扩展到了支持的线速率,这个线速率如何进入TX和RX端呢?主要通过TXSYSCLKSEL来进行选择,为1时,进入QPLL。为0时,进入CPLL,如下图所示。这样时钟基本配置的原理就说清楚了!

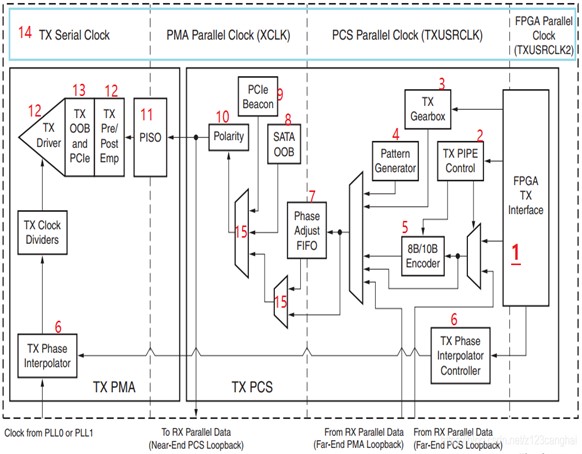

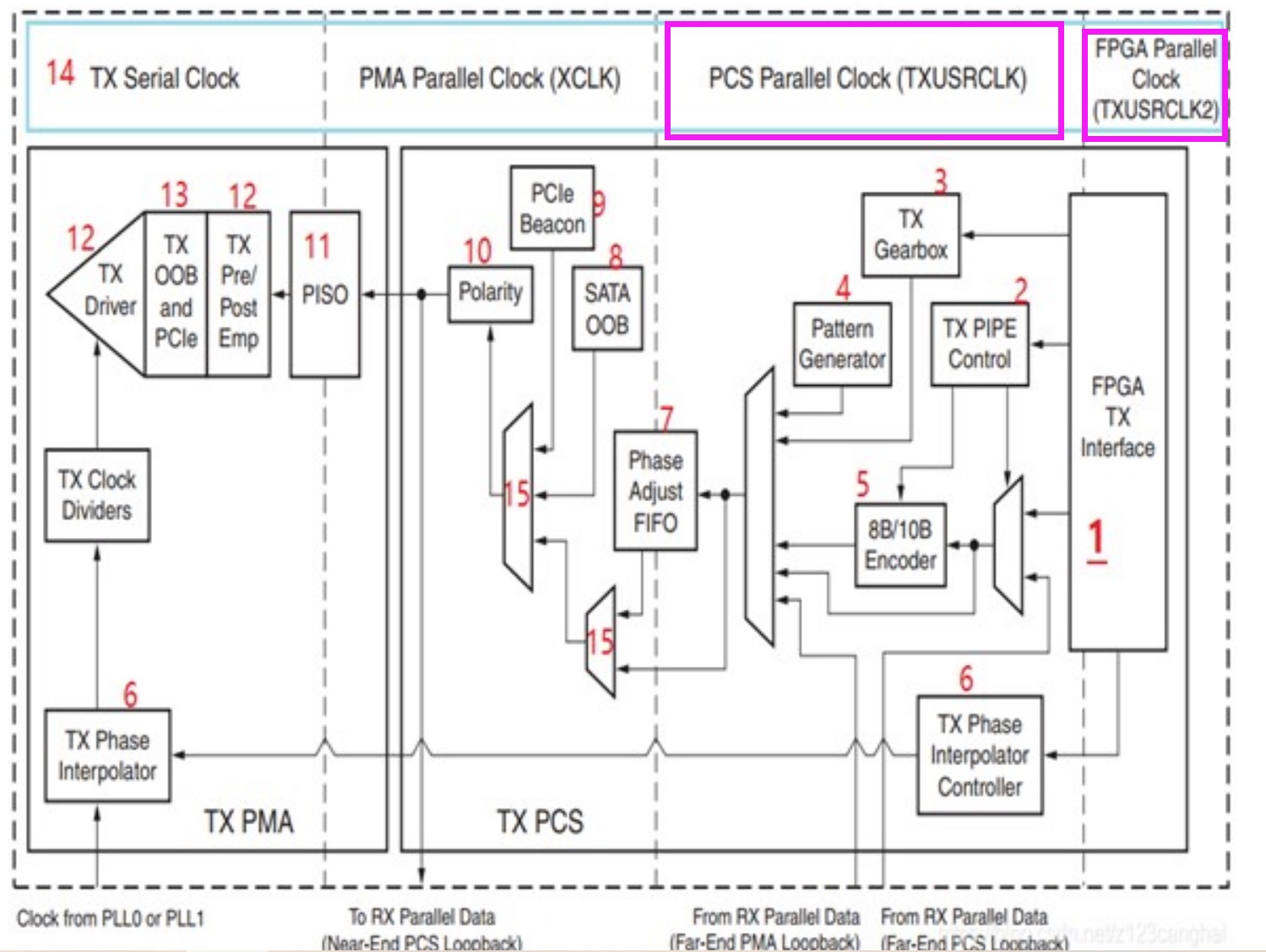

GTX发射端的各个模块如下图所示

①用户数据的输入接口

②PCIe物理层接口,如果使能了PCIE接口,则该通道是PCIE的数据通道。

③GTX除了支持8B / 10B编码外还支持64B / 66B和64B / 67B编码方式,以此来提高有效数据的传输效率,支持这些通过对该模块的配置实现。

④产生伪随机序列,用于高速串行通信通道传输的误码率测试

⑤8B/10B 编码

⑥TX相位插值器控制器模块,对TX PMA中的数据进行微调。

⑦为了保证数据传输速率一致,XCLK必须和TXUSERCLK时钟的速率匹配,并且要解决2个时钟域之间的相位差异。

⑧串口硬盘

⑨提供PCIE的唤醒功能

⑩从PSC子层输出的编码数据,在发送端的串行化处理之前进行极性翻转(为了兼容不同板卡间极性的不同或是PCB搞错的了情况。)

⑪并行输入串行输出,实现数据的串并转换功能

⑫发器TX驱动器是高速电流模式差分输出缓冲器

⑬这个主要是当GTX作为PCIE或SATA接口时所需要的功能

⑭CLK:用户接口的数据输入到串行数据的输出要跨四个时钟域

⑮MUX:多路选择器

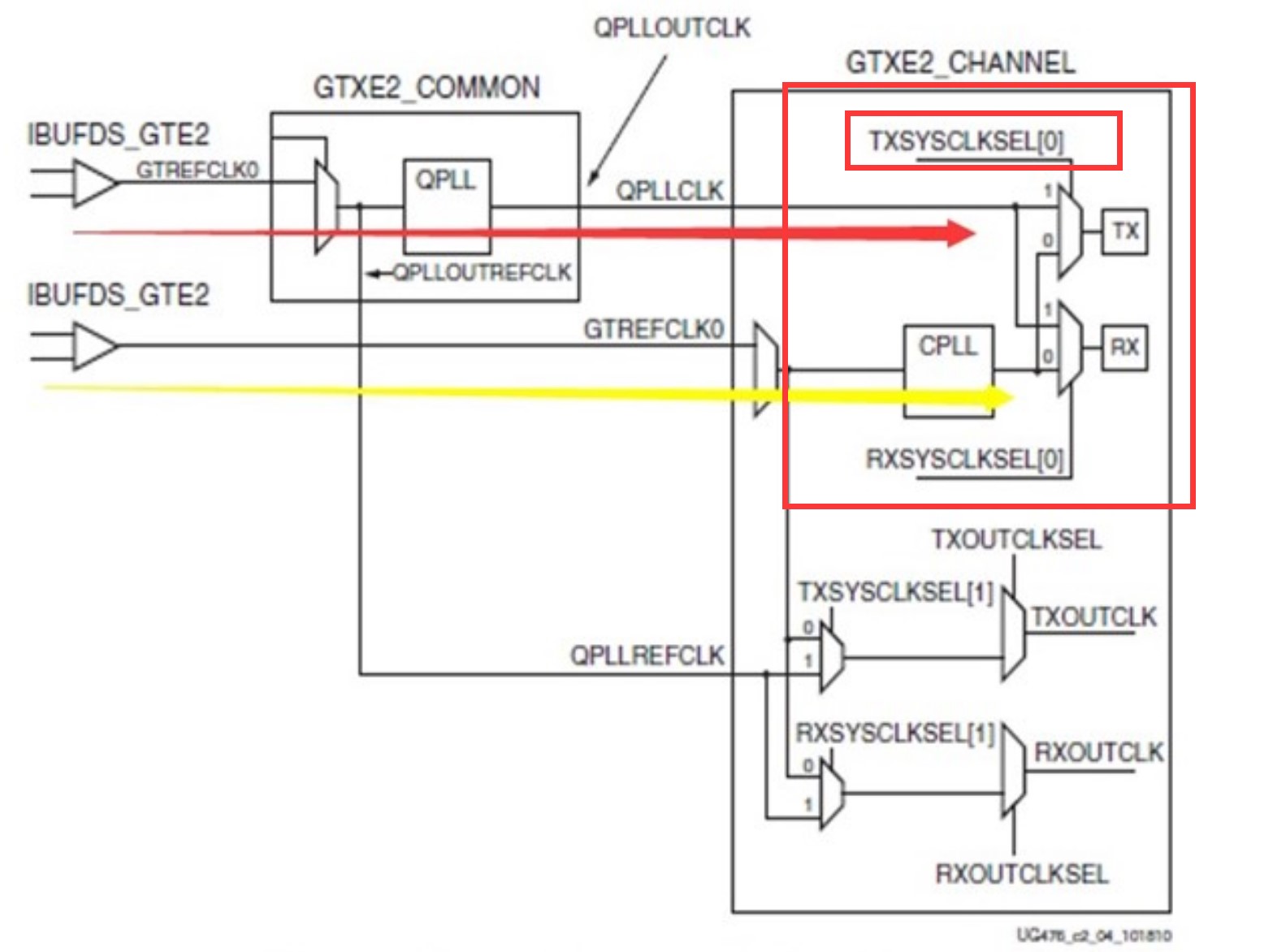

介绍了模块的作用后,还需要了解GTX发射端的时钟,才可以了解他的工作方式。①其中红框部分和黄底部分的内容是我们需要重点了解的地方,图中的MGTREFCLK是前面提到的GTX的参考时钟,经过一个IBUFDS_GTE2源语之后进入GTX,用以驱动CPLL或者QPLL。对于TX PMA来说,主要实现的功能是并串转换,其并串转换的时钟可以由CPLL提供,也可以由QPLL提供,由TXSYSCLKSEL选择,TX PMA子层里面有三个红色方框部分是串行和并行时钟分频器,作用是产生并行数据的驱动时钟。

②D分频器主要用于将PLL的输出分频,以支持更低的线速率。

③÷2/÷4这个选项由TX_INT_DATAWIDTH决定,如果TX_INT_DATAWIDTH为“0”,则选择÷2,反之选择÷4。

④对于÷4/÷5,则由TX_DATA_WIDTH决定,如果是位宽是16/32/64,则选择÷4,如果位宽是20/40/80,则选择÷5。

然后红框的1是通过QPLL或者CPLL的时钟输出,由图所知,分别负责PISO的时钟。和GTX的发射域时钟,红框2为具体控制发射域时钟的数据方法。

数据域时钟又是什么呢?我们回到刚刚的图。框框所示。

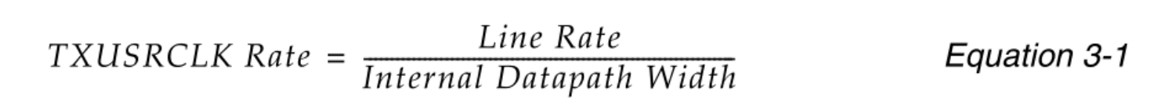

根据这个公式还有我们上面计算的线速度,我们可以计算出TXUSERCLK的时钟

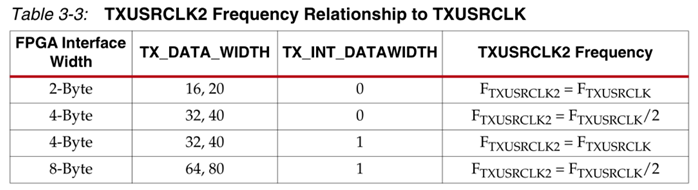

根据这个表格,我们可以计算出TXUSERCLK2的时钟。具体的控制方式如下图,通过TXOUTCLK和位宽来控制这两个时钟的速度

![]()

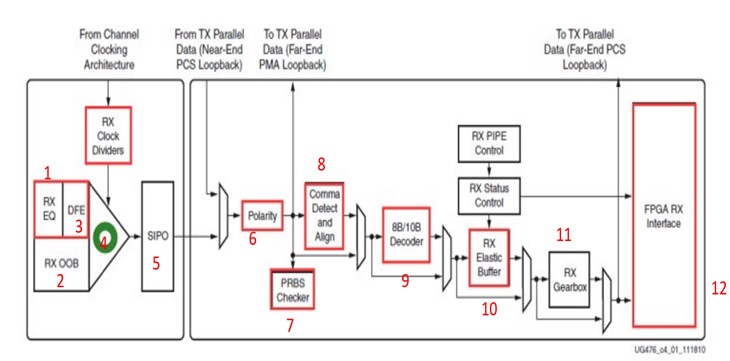

①模拟前端

②OOB信号

③均衡器

④CDR 时钟数据恢复

⑤串并行转换

⑥极性翻转

⑦伪随机序列码检查其

⑧字节、字的对齐功能

⑨8/10bit解码

⑩接收弹性缓冲区

⑪变速器

⑫用户数据的输入接口

具体各个模块的功能介绍如下:

OOB信号:带外信号,为了发送这些数据,协议一般不使用与普通数据相同的通道,而是使用另外的通道。

DFE均衡器:RX信号从AFE(模拟前端)进来之后,首先经过RX均衡器,均衡器的主要作用是用于补偿信号在信道传输过程中的高频损失,因为信道是带宽受限的,所以信号经过它必将造成衰减甚至遭到破坏。RX接收端的均衡器有两种,分别是LPM和DFE,两者功耗和性能有所不同,其中LPM功耗较低,DFE能提供更精确的滤波器参数,从而可以更好的补偿传输信道损失,因此性能更好。

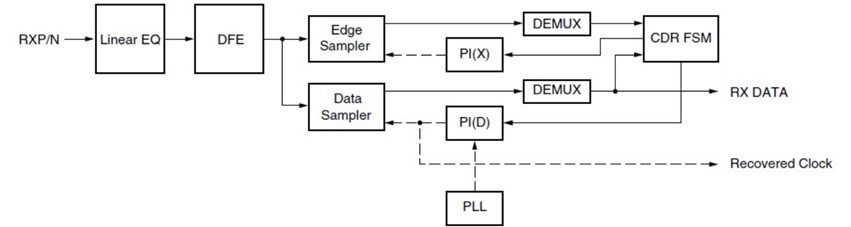

RX CDR:RX的时钟数据恢复电路是图1的绿色圆圈部分,因为GTX传输不带随路时钟,因此在接收端必须自己做时钟恢复和数据恢复,时钟数据恢复电路如图所示:

具体过程如图2所示,首先外部数据进来之后经过均衡器,紧接着均衡器出来的数据就进入时钟数据恢复电路。GTX使用相位旋转CDR结构,从DFE进来的数据分别被边缘采样器和数据采样器捕获,然后CDR状态机根据两者决定数据流的相位并反馈控制相位内插器(PI),当数据采样器的位置位于眼图中央的时候边缘采样器锁定到数据流的传输域。其中CPLL或者QPLL为相位内插器提供基础时钟,使CDR状态机能很好进行相位控制。

GTP收发器接收器包括一个内置的PRBS检查器:可以将此检查器设置为检查四种行业标准PRBS模式之一。检查器是自同步的,并在K码对齐或解码之前处理传入的数据。此功能可用于测试通道的信号完整性。

GTX RX端接收的串行数据在进行解串(并行化)之前,需要进行特征边界对齐,使得并行数据得到正确的恢复。GTX进行对齐操作的方式是通过检测K码实现的。RX接收器从输入的串行数据流中搜索comma,若RX接收器检测到K码则将K码移动到字节边界,使得接收端接收的并行数据与发送端发送的数据一致。为实现该功能,

8/10bit的解码不做介绍

接收弹性缓冲区:GTX收发器RX数据通路的PCS部分有两个内部并行时钟域:PMA并行时钟域(XCLK)和RXUSRCLK域。要保证数据的正确接收,不仅要求速率一致,也要解决两个时钟域之间的相位差异。

变速器是处理64B / 66B编的

FPGA RX接口与TX端类似

综上,信号回到了数据输入输出接口,可以继续从发送端发射数据

PS关于时钟域的问题

RX接收端的时钟结构和TX发送端的很类似,如图所示,图中红色方框的CDR部分是和TX端最大的区别。

浙公网安备 33010602011771号

浙公网安备 33010602011771号