GTX_IP核实现SMA口发送数据(一)IP核配置

1 概述

本文是用于总结GTX例程的学习成果。主要是从IP的设置,IP核的例程代码构成与引用两方面介绍使用GTX IP核来控制SMA口发送数据的方法。

2 参考文档

《pg168-gtwizard》

《ug476_7Series_Transceivers》

3 GTX的IP设置

本例程使用环境

编译环境:vivado 2017.4

选用FPGA:XC7K325T-2FFG900

GTX IP界面的设置情况

本例程使用GTX主要是实现SMA口,而不是PCIE,SATA等特殊协议。采用的编码形式为8B/10B,对齐字符为K码。

本例程的IP设置情况如下所示:

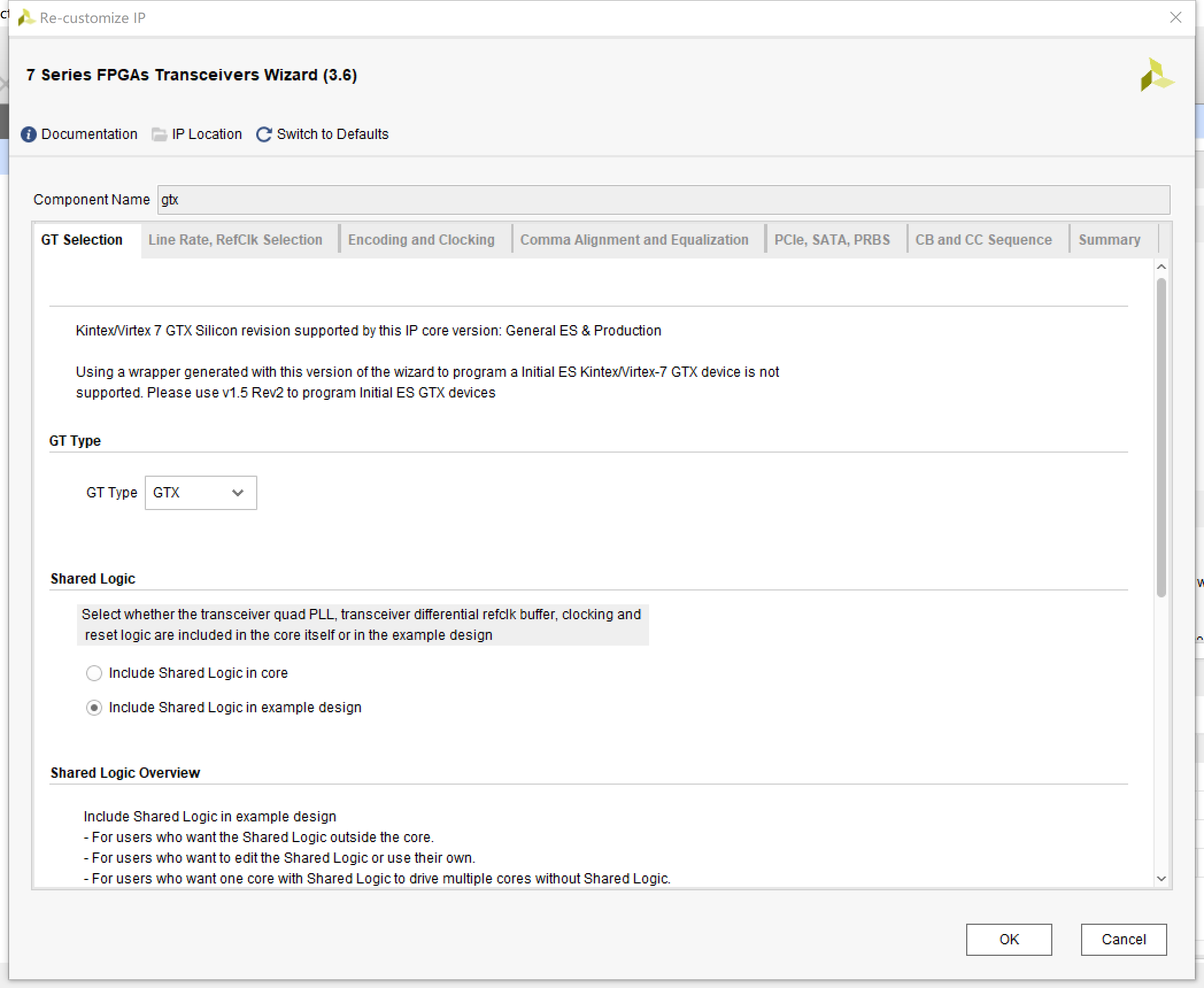

GTX IP设置第1页

第1页设置主要是GT的类型,这个一般根据器件会确定默认选择,高端器件可能有两种根据自己需要的速率设置即可。

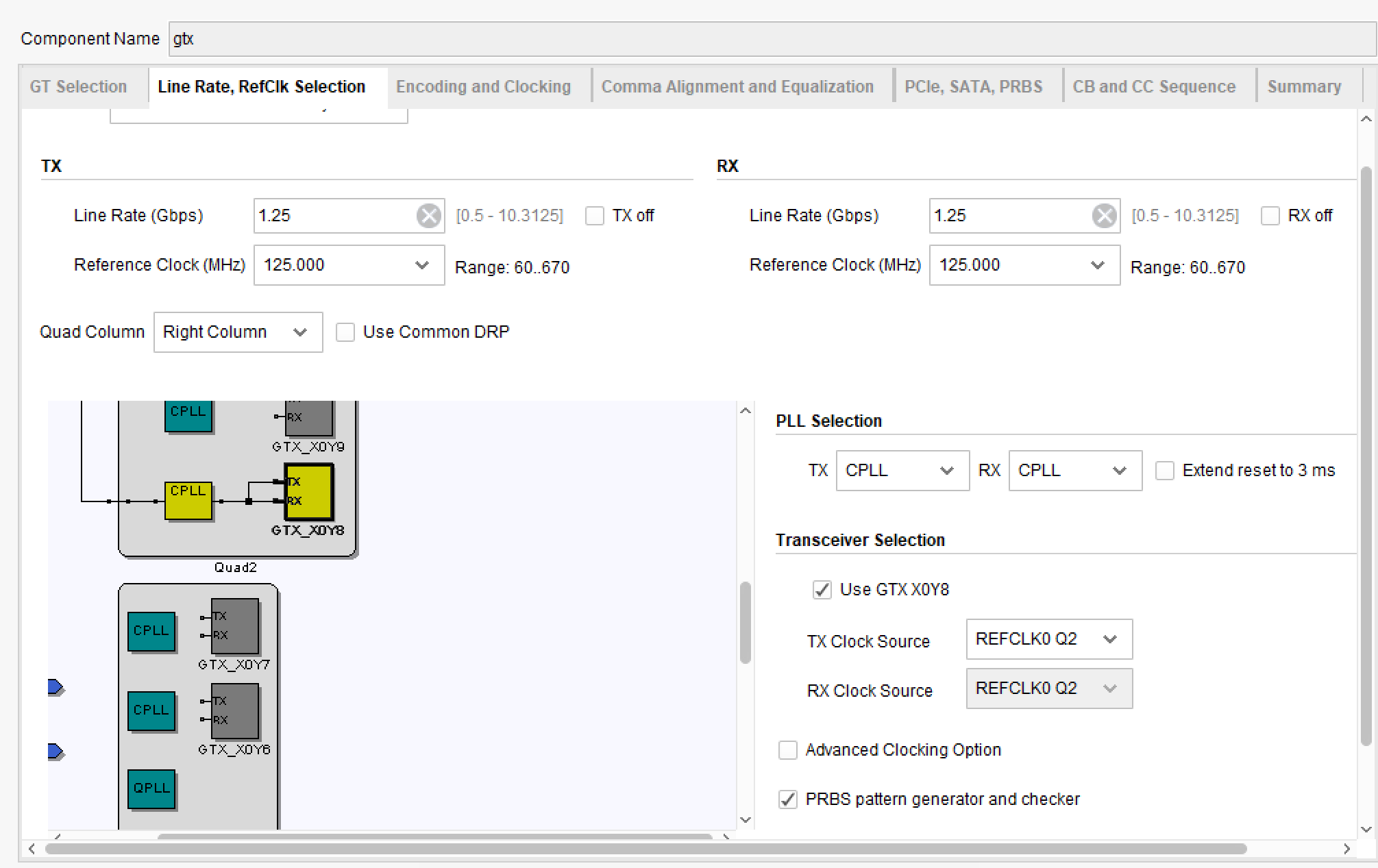

GTX IP设置第2页

通过上文的介绍,我们知道SMA口在GTX bank117里面 所以打开GTX_X0Y8通道 时钟选择REFCLK1 Q2

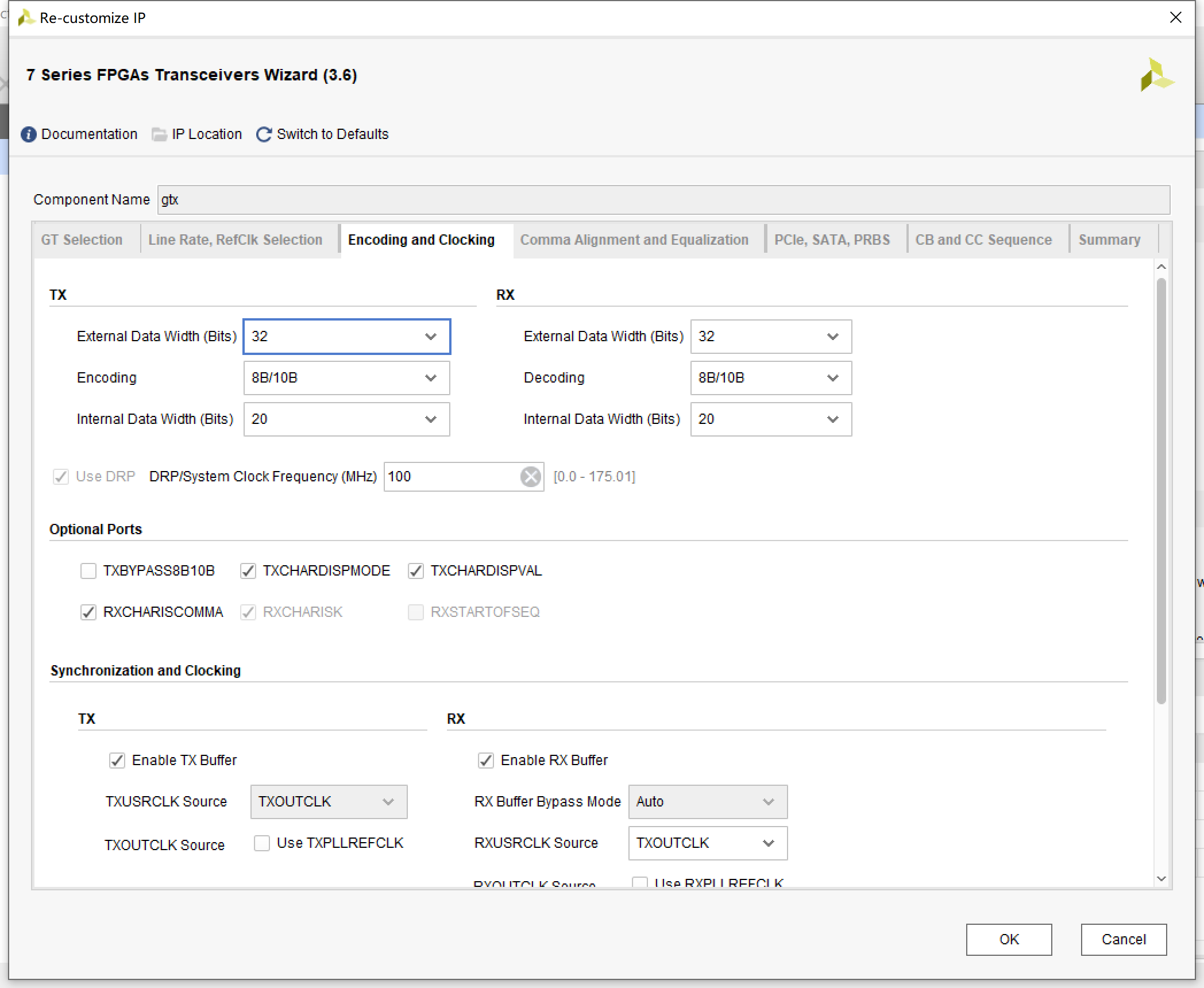

GTX IP设置第3页

具体参数如下

| Option | I/O | Description |

| TXPCSRESET | Input | Active-High reset signal for the transmitter physical coding sublayer (PCS) logic. |

| TXBUFSTATUS | Output | 2-bit signal monitors the status of the TX elastic buffer. This option is not available when the TX buffer is bypassed. |

| TXRATE | Input | Transmit rate change port. |

| RXPCSRESET | Input | Active-High reset signal for the receiver PCS logic. |

| RXBUFSTATUS | Output | Indicates condition of the RX elastic buffer. Option is not available when the RX buffer is bypassed. |

| RXBUFRESET | Input | Active-High reset signal for the RX elastic buffer logic. This option is not available when the RX buffer is bypassed. |

| RXRATE | Input | Receive rate change port. |

| QPLLPD | Input | Visible only when GTX or GTH transceiver is selected. Powerdown port for QPLL. |

| CPLLPD | Input | Visible only when GTX or GTH transceiver is selected. Powerdown port for channel PLL (CPLL). |

GTX IP设置 其他页面设置保持不变,默认即可。

具体代码解读后续更新

<wiz_tmp_tag id="wiz-table-range-border" contenteditable="false" style="display: none;">

浙公网安备 33010602011771号

浙公网安备 33010602011771号