GTX简介

1.GTX收发器接口

1)GTX接口的基本简介

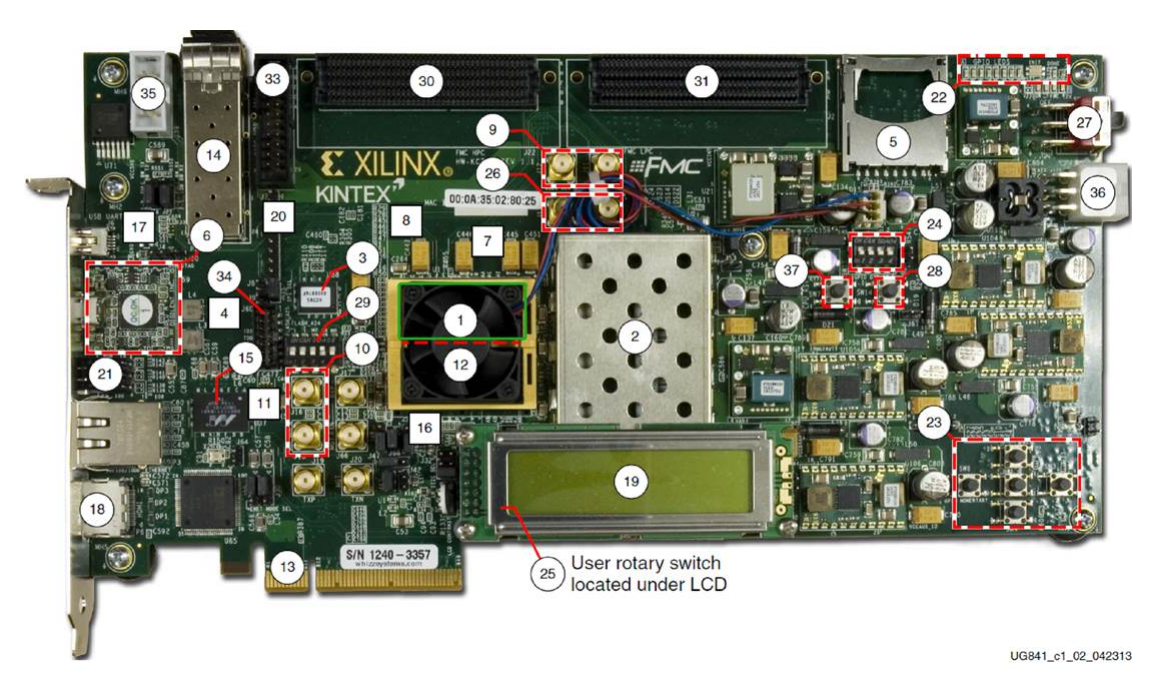

Xilinx 7系列FPGA全系所支持的GT(GT,Gigabyte Transceiver,G比特收发器)。通常称呼为Serdes、高速收发器。内嵌在FPGA中,如绿色框框所示。

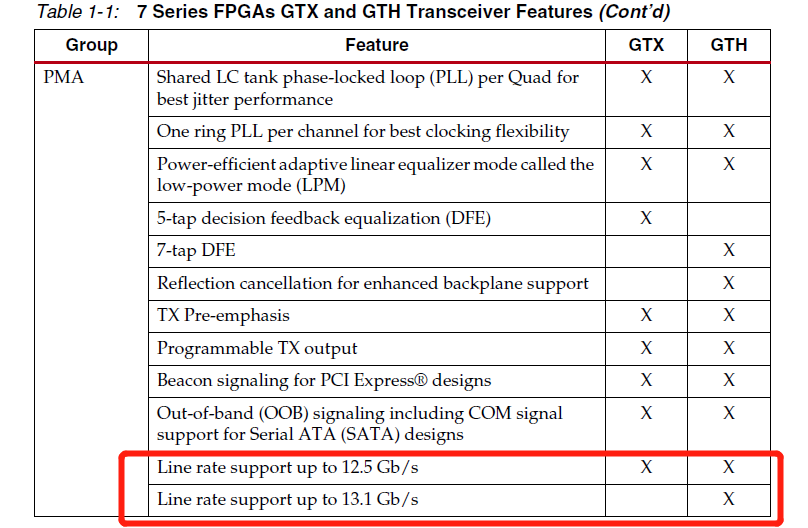

Xilinx 7系列中,按支持的最高线速排序,GTP<GTX<GTH<GTZ。GTP被用于A7系列,GTZ被用于少数V7系列。从K7到V7,最常见的是GTX和GTH,GTH的最高线速比GTX稍微高一点点。(咱们的板子是K7系列,所以用的是GTX或者GTH)。GTX 收发器支持 500 Mb/s 至 12.5 Gb/s 线速率。GTH的最大速率为13.1Gb/s,总体二者原理和速率相差不大。

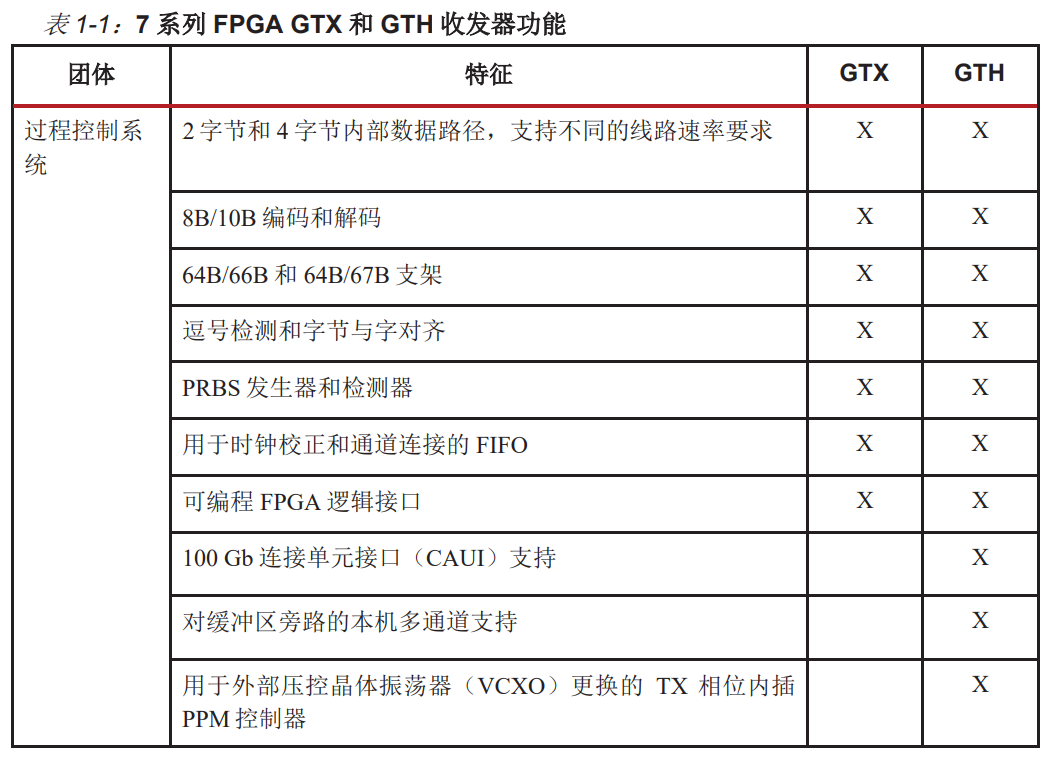

GTX/GTH 收发器具有高度可配置性,支持多种功能。支持的功能如下图。(X代表支持)PRBS(Pseudo-Random Binary Sequence) 伪随机二进制序列。GTX收发器功能如下:

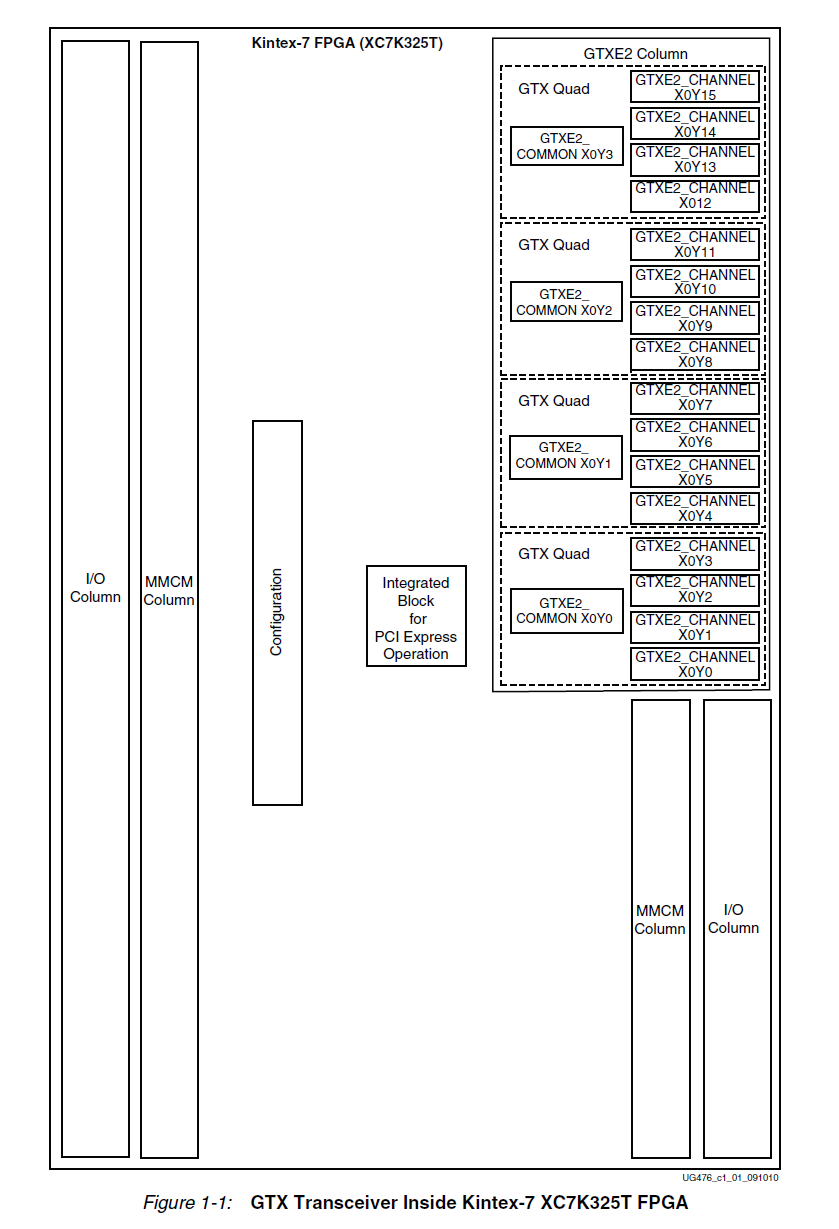

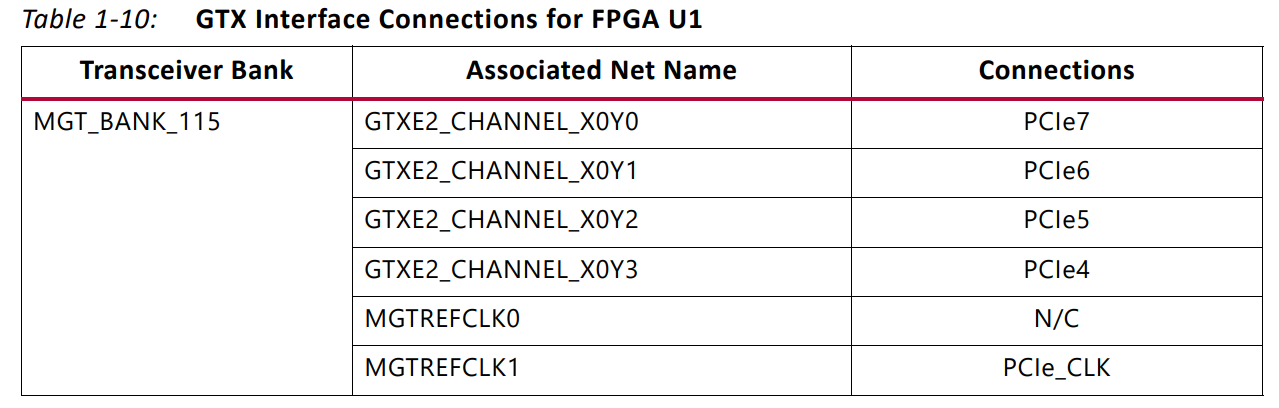

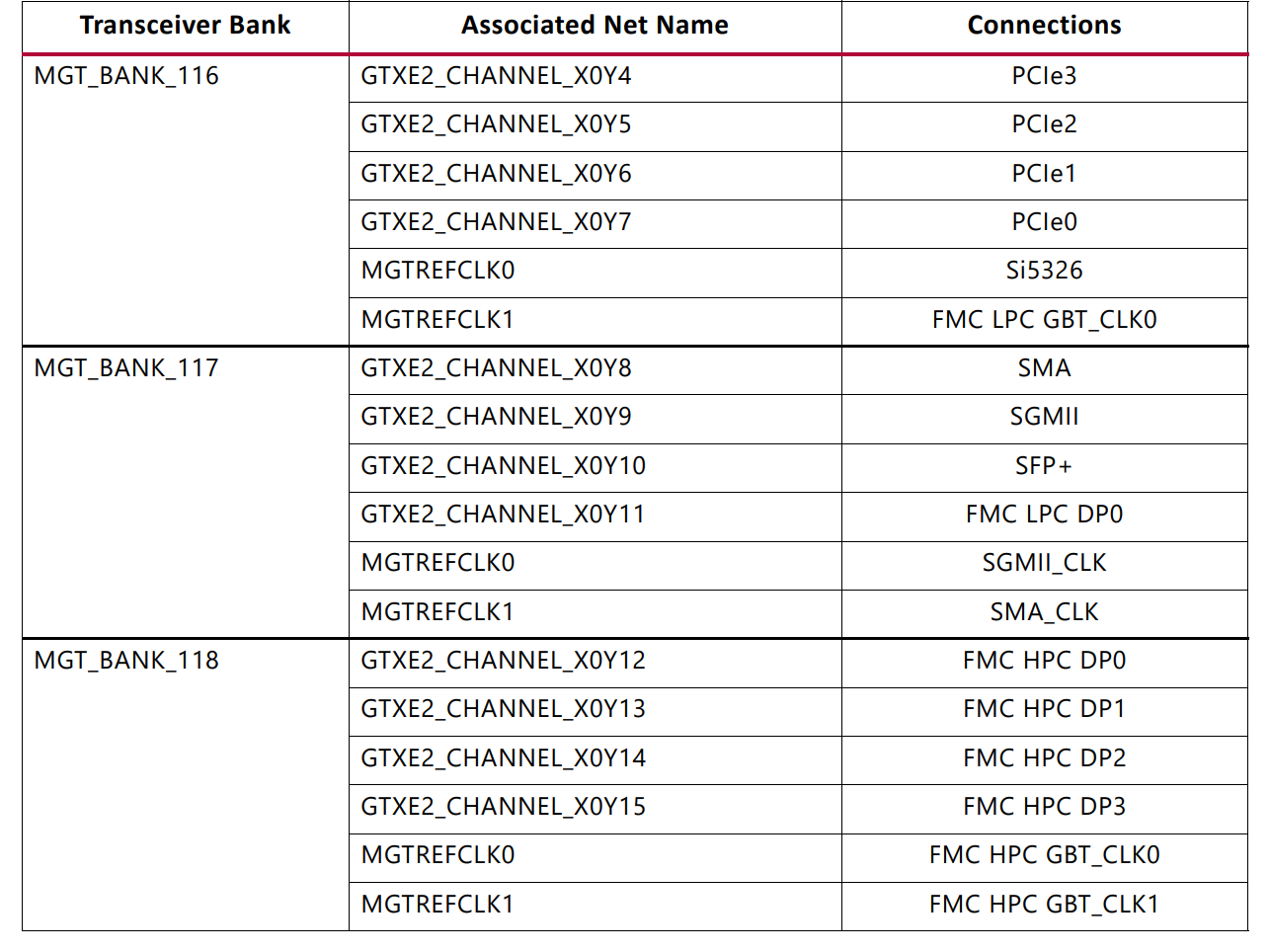

2)本板子的GTX资源:

我们使用的XC7K325具有16个GTX的通道,7系列FPGA通常按照bank进行划分,对于GTX/GTH的bank,一般称为一个Quad(一个bank中有4个独立的GTX通道,每个通道称为channel);每个Quad拥有两个参考时钟Pin,也可以从上下两个Quad中获得参考时钟。

•八个 GTX 收发器连接至 PCIExpress x8 端点边缘连接器

• 四个 GTX 收发器连接到 FMC HPC 连接器(J22)

• 一个 GTX 连接到 FMC LPC 连接器(J2)

• 一个 GTX 连接到 SMA 连接器(RX:J17,J18 TX:J19,J20)

• 一个 GTX 连接到 SFP / SFP +模块连接器(P5)

• 一个 GTX 用于 SGMII 与以太网 PHY(U37)的连接

具体四个QUAD的分配

Quad 115:

包含用于 PCI Express 通道 4-7 的 4 个 GTX 收发器

MGTREFCLK1-来自 P1 的 PCIE_CLK

• Quad 116:

包含用于PCIe 通道 0-3 的 4 个 GTX 收发器

MGTREFCLK0-Si5326 抖动衰减器

MGTREFCLK1-FMC LPC GBT 时钟

• Quad 117:

包含 4 个 GTX 收发器,其中一个分配给:SMA,SGMII,SFP 和 FMC LPC(DP0)

MGTREFCLK0-SGMII 时钟

MGTREFCLK1-SMA 时钟

• Quad 118:

包含用于 FMC HPC 的 4 个 GTX 收发器(DP0-DP3)

MGTREFCLK0-FMC HPC GBT 时钟

MGTREFCLK1-FMC HPC GBT 时钟

3)GTX收发机具体功能介绍

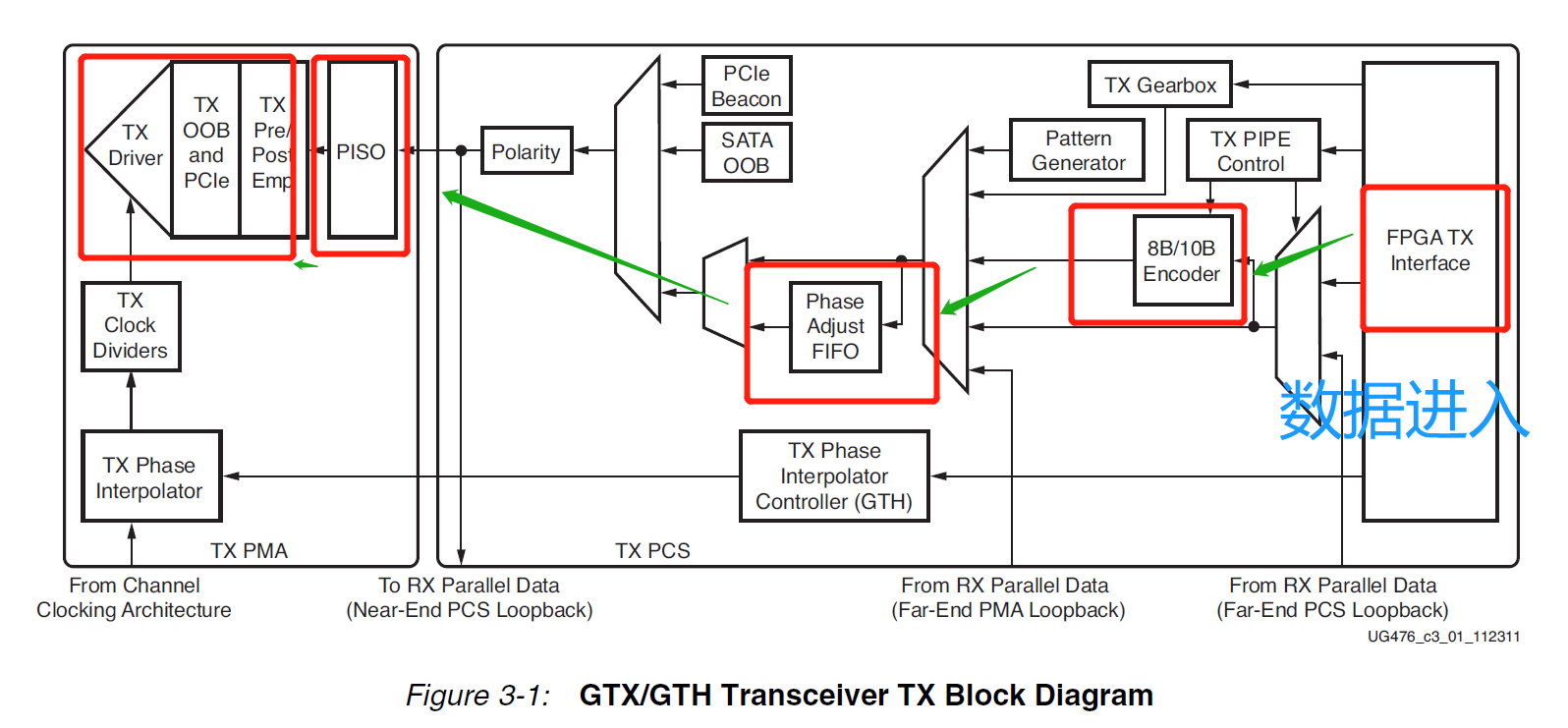

发射端TX工作原理如图3-1所示:

官方说法:

GTX每个收发器包括一个独立的发射器,该发射器由一个PCS和一个PMA组成。并行数据从FPGA逻辑流入FPGA TX接口,通过PCS和PMA,然后作为高速串行数据输出TX驱动程序。发出的信号为模拟信号

专有名词解释:(PCS是物理编码子层,位于协调子层(通过GMII)和物理介质接入层(PMA)子层之间)

个人理解步骤:

1)将需要发送的16/32bit(或者8/10bit)并行数据通过内部fifo传给编码模块;

2)编码后的数据需要跨时钟域到并串转换模块(PCS到PMA)缓存到fifo;

3)并串转换完成后发给TX驱动器调整数据电器特性后从高速IO口发出;

RX模块工作原理与TX正好相反

调整数据电器特性、串并转换、8B/10B编码。

缺点:8B/10B编码效率比较低(不知道对整体系统影响如何),有20%的额外开销;常用于8G以下使用;

改进:GTX还提供了GearboX,其内部包含64b/66b编码;

更具体的介绍如下

GTX_IP核实现SMA口发送数据(4)GTX具体各个模块原理详细介绍 - 快乐气氛组阿宇 - 博客园 (cnblogs.com)

浙公网安备 33010602011771号

浙公网安备 33010602011771号