20155212 2017-2018-1 《信息安全系统设计》第7周学习总结

20155212 2017-2018-1 《信息安全系统设计》第7周学习总结

教材学习内容总结

Chapter 4

- 定义一个指令集包括

- 状态单元

- 指令集

- 编码

- 编程规范

- 异常事件处理

- 程序员可见状态:每条指令都会读取或修改处理器状态的某些部分

- 状态码Stat:表明程序执行的总体状态

- 执行字级计算的组合电路根据输入字的各个位,用逻辑门来计算输出字的各个位

- 组合电路从本质上讲,不存储任何信息,只是简单地响应输入信号,产生等于输入的某个函数的输出

- 处理

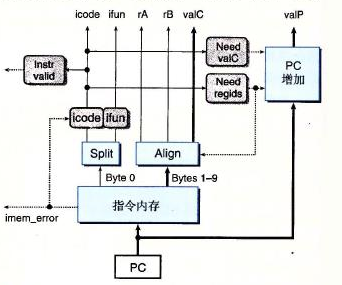

- 取指——PC增加器:从内存读取指令字节,地址为PC的值。从指令中抽取出指令指示符的两个四位部分

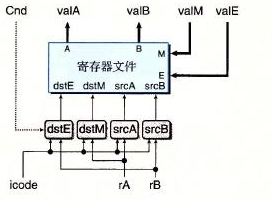

icode(指令代码)和ifun(指令功能) - 译码——读端口A和B:从寄存器文件读入最多两个操作数,得到值valA和/和valB

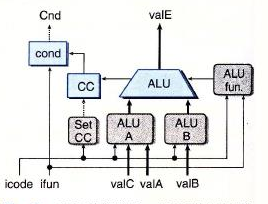

- 执行——ALU、CC:ALU,要么执行指令指明的操作(根据ifun),计算内存引用的有效地址,要么增加或减少栈指针。该阶段决定分支。

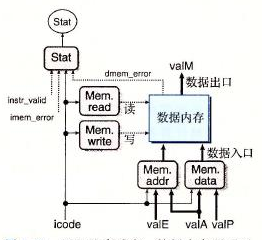

- 访存——内存:读写数据

- 写回——两个写端口:最多可以写两个结果到寄存器文件

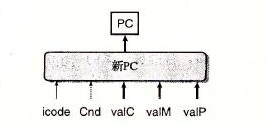

- 更新PC——PC:将PC设置成下一条指令的地址

- 取指——PC增加器:从内存读取指令字节,地址为PC的值。从指令中抽取出指令指示符的两个四位部分

- 处理器停止的异常:执行halt指令或非法指令、或试图读/写非法地址

- 除了ALU计算必须根据ifun中编码的具体的指令操作来设定

- 组织计算原则:从不回读

- SEQ阶段实现

- 取指阶段

- 译码和写回阶段

- 执行阶段

- 访存阶段

- 更新PC阶段

- 取指阶段

- 引入流水线能获得更好的性能

- 现代逻辑设计中,电路延迟以微微秒或皮秒,即2^-12秒为单位计算

- 流水线的局限性

- 不一致的划分

- 流水线过深,收益反而下降

- 在PIPE-中流水线一直携带dstE和dstM的目的是:确保写端口的地址和数据输入是来自同一条指令

- 相邻指令的相关/冒险:数据相关/冒险、控制相关/冒险

- 如果一条指令在器处理中于某个阶段产生了一个异常,这个转台字段就被设置成指示异常的种类

- 异常时,流水线控制逻辑必须禁止更新条件码寄存器或是数据内存

- 流水线控制逻辑:

- 加载/使用冒险

- 处理ret

- 预测错误的分支

- 异常

- CPI=(Ci+Cb)/Ci=1.0+Cb/Ci=1.0+lp+mp+rp

教材学习中的问题和解决过程

- 电路中的寄存器和汇编中说的寄存器有区别吗?

- 在硬件中,寄存器直接将输入和输出线连接到电路的其他部分;在机器级编程中,寄存器代表的是CPU中为数不多的可寻址的字。

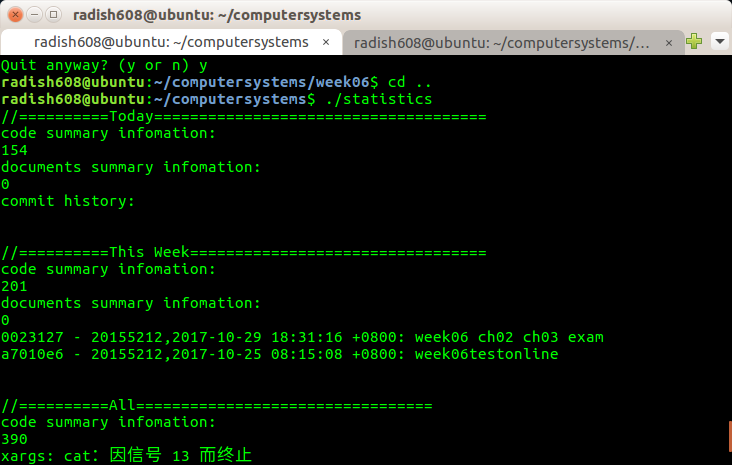

代码托管

其他

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 96/96 | 1/1 | 15/15 | |

| 第二周 | 30/126 | 1/2 | 21/36 | |

| 第三周 | 30/156 | 1/3 | 21/57 | |

| 第四周 | 10/156 | 1/4 | 20/77 | |

| 第五周 | 23/189 | 1/5 | 20/97 | |

| 第六周 | 201/390 | 1/6 | 8/95 | |

| 尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。 | ||||

| 耗时估计的公式 | ||||

| :Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。 |

-

计划学习时间:10小时

-

实际学习时间:8小时

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)