CPU性能指标简览

作为计算机的运算核心和控制核心,CPU(Central Processing Unit)由运算器、控制器、寄存器和实现其之间联系的数据、控制及状态的总线构成,决定着计算机运算性能强弱。作为信息技术产业的核心基础元器件,CPU的运作可分为四个阶段:提取(Fetch)、译码(Decode)、执行(Execute)和回写(Writeback)。

用一句话来概括CPU的运作原理:CPU从存储器或高速缓冲存储器中取出指令,将指令放入寄存器,并对指令译码、执行指令。

在嵌入式系统行业,用于评价CPU性能指标的标准主要有:

- MIPS(Million Instructions Per Second):即每秒能够执行的百万级机器语言指令数,用于计算系统的秒级处理能力,是衡量CPU速度的一个指标。

- DMIPS(Dhrystone MIPS):指CPU运行整数运算(Dhrystone)时所表现的相对性能,只适用于评估标量机(对应:向量机)。

- FLOPS(Floating-point Operations Per Second):表示CPU每秒执行的浮点运算次数,主要用于衡量计算机的浮点运算能力。

- CoreMark:以每秒迭代次数作为性能评价。

MIPS标准

1970年代,小型电脑的性能是通过与VAX MIPS相比较来评估的,指比较与VAX 11/780(市场公认的1 MIPS机器)运行同一工作的运行时间。

▲ 已经46岁的VAX 11/780

MIPS无法在不同的处理器架构下进行比较。由于不是每一条机械指令都能在单周期计算完成,所以计算MIPS的时候会引入一个CPI(Clock cycle per intruction,每条指令的平均时钟周期数)值。公式如下:

- MIPS=指令数/(执行时间*1000000)

- MIPS=主频/(CPI*1000000)

DMIPS标准

在一定意义上,DMIPS也是以VAX 11/780处理器作为标称值的。

这里要先引入当今最有代表性的通用跑分处理程序之一,Dhrystone。Dhrystone是由Reinhold P. Weicker在1984年提出来的一个基准测试程序,其主要目的是测试处理器整数运算和逻辑运算的性能。由于VAX 11/780处理器每秒能够循环Dhrystone程序1757次,因此其他处理器每秒钟执行Dhrystone程序的循环次数除以1757即为其 DMIPS值。

在此基础上,除去工艺、功耗等可能的影响因素,将处理器的DMIPS值除以其频率,便可得到更能直观体现处理器微架构设计本身性能的DMIPS/MHz。

MIPS和DMIPS的区别:

- MIPS反映的能力——每秒钟能够执行的指令集数量,这个能力由CPU的架构、内存的访问速度等硬件特性决定;

- DMIPS反映的能力——每秒钟能够实现的工作数量。

*按字面意思进行理解,MIPS与DMIPS之间似乎存在转换公式,但经查证,两者完全是从不同角度来评估CPU性能的,并无直接转换

*“Dhrystone”名字的由来是相对更早出现的另一个测试CPU浮点计算性能的工具“Wetstone”。“Wetstone”本意为“湿石头”,Dhrystone则是干石头,用于测试CPU的整数计算性能。

FLOPS标准

FLOPS常被用来估算电脑的执行效能,尤其是在使用到大量浮点运算的科学计算领域中。“浮点运算”由于涵盖所有涉及小数的运算,相较于整数运算会更花时间。当前大部分的处理器中都会配备专用于处理浮点运算的“浮点运算器”(Float Point Unit,FPU),因此FLOPS标准所测量的实际上是FPU执行速度。

CoreMark标准

CoreMark可以理解为与Dhrystone类似的综合处理器跑分程序,由非营利组织嵌入式微处理器基准评测协会EEMBC的Shay Gla-On于2009年提出,其主要目标是测试处理器核心性能。

*EEMBC:Embedded Micro-processor Benchmark Consortium

CoreMark程序使用C语言写成,包含如下的运算法则:列举(寻找并排序)、数学矩阵操作(普通矩阵运算)、状态机(用来确定输入流中是否包含有效数字)和CRC(Cyclic Redundancy Check,循环冗余校验)。CoreMark具有特定的运行和报告规则,从而可以避免由于所使用的编译库不同而导致的测试结果难以比较。因此CoreMark标准被认为比Dhrystone标准更有实际价值。

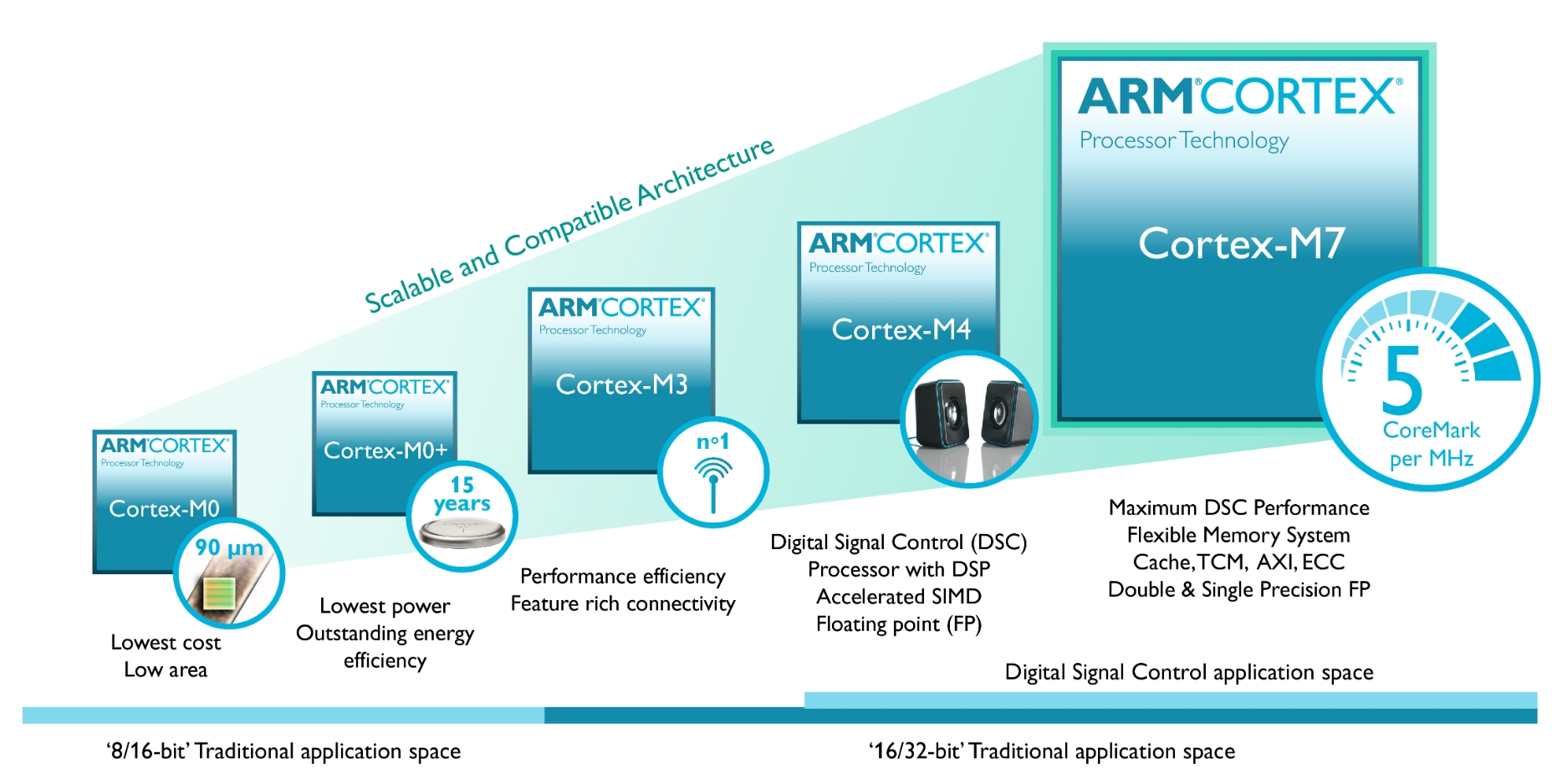

CoreMark标准以在某配置参数组合下,单位时间内CoreMark程序的运行次数作为度量标准,其指标单位为CoreMark/MHz。CoreMark数字越高,意味着性能更高。

▲ARM处理器官方性能对比:Cortex-M部分系列

参考文献

[1]顾梦杰. 基于RISC-V指令集架构的通用微控制器设计[D].东华大学,2022.DOI:10.27012/d.cnki.gdhuu.2022.000609.

[2]从性能指标角度看ARM Cortex-M各处理器区别,https://mp.weixin.qq.com/s/o1amLyzc8ZO8l59N5F2vyw

[3]性能评估单位说明,https://zhuanlan.zhihu.com/p/571545878

[4]科普总结:Flops、FLOPS、GFLOPS,https://imgtec.eetrend.com/blog/2020/100048896.html

[5]Classic Benchmarks,http://www.roylongbottom.org.uk/classic.htm

浙公网安备 33010602011771号

浙公网安备 33010602011771号