MIG(Memory Interface Generator)--用于读写DDR的控制器

一、MIG核设置:

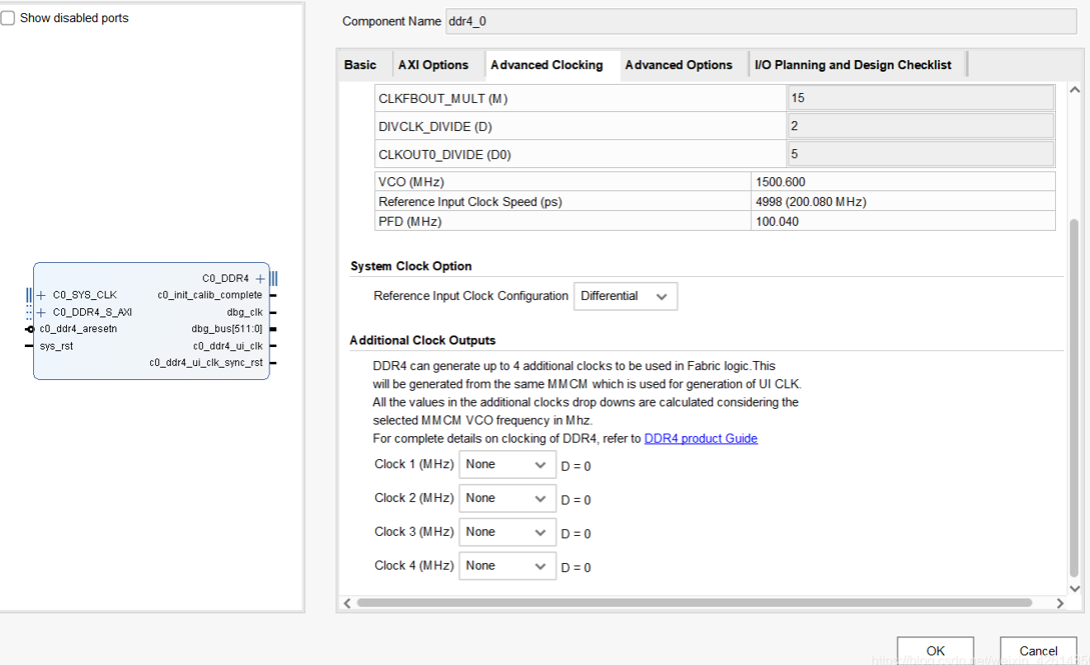

cloking - 时钟模块配置

Memory Device Interface Speed : 芯片的时钟频率 (一般选择默认)1200MHz;

Phy to controller clock frequency ratio: 物理层与控制器时钟频率比,即DDR内部时钟和用户时钟的频率比,此处默认为4:1模式,且只有4:1模式;

Reference Input Clock Speed : 参考时钟频率200Mhz。

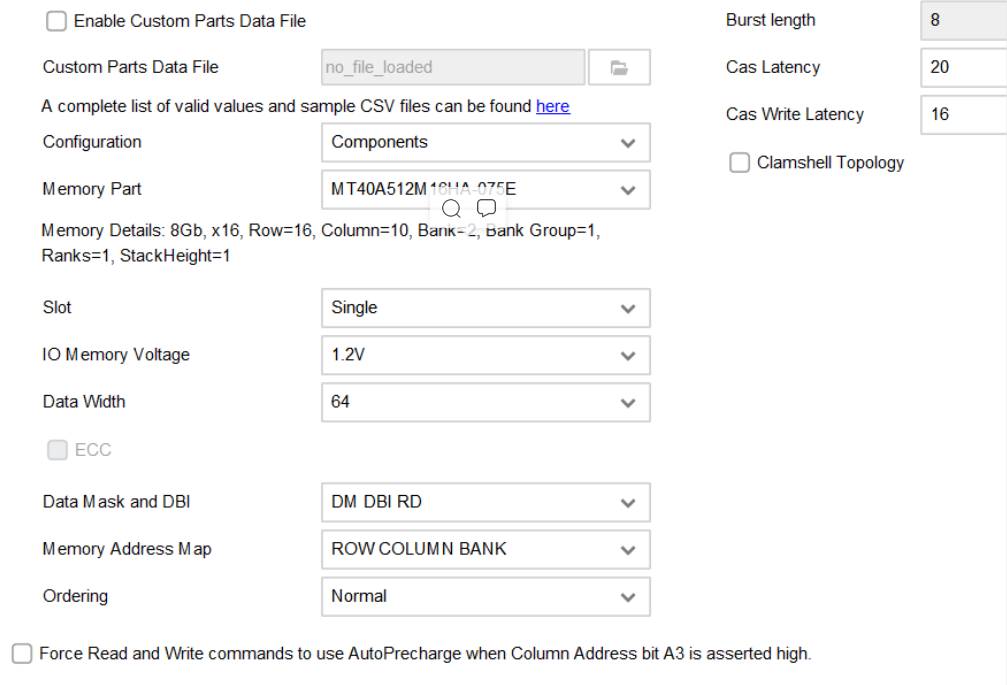

Memory Options – 内存操作

Cas latency是“内存读写操作前列地址控制器的潜伏时间”;

此处的 Cas latency 和 Cas Write latency 为 DDR 内部数据的延迟时间,设定成多少都可以,都不妨碍正常数据的存储和传输。

Controller Options – 控制操作

Configuration : 选择默认的配置 components; (其中components指的是DDR的型号是元器件,而不是类似于笔记本电脑那种插条式的内存条<笔记本内存条是SODIMMS>,这里一共有4个选项)

Memory Part : 内存型号,根据DDR 型号进行配置;

Slot : 选择默认的 Single ;(只有该选项)

IO Memory Voltage : 芯片电压;(只有该选项)

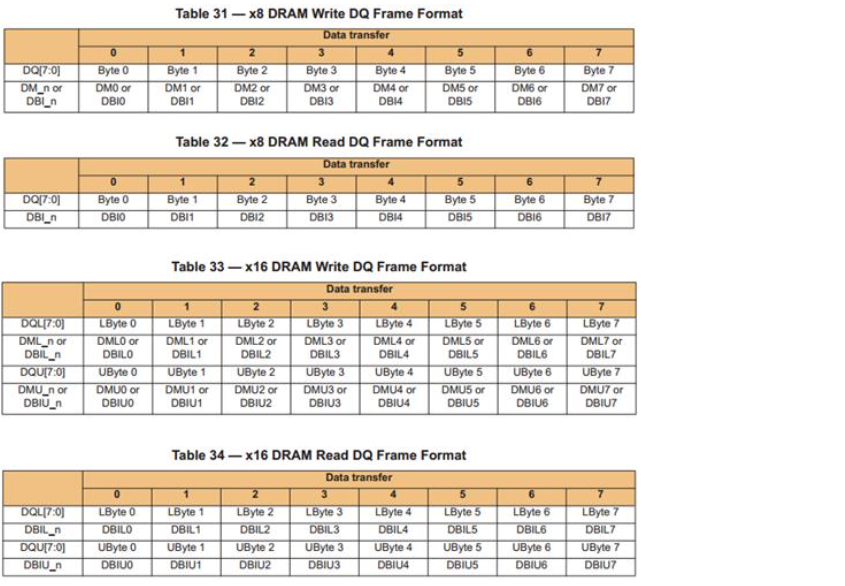

Data Width : 64; DDR的物理位宽,这个需要根据芯片选择。DDR对应的每片存储颗粒位宽为16bit,那么4个颗粒度的DDR的总位宽为64bit;

Data Mask and DBI : 数据掩码和DBI(Data Bus Inversion<数据总线反转>): 选择 DM DBI RD;

Memory Address Map : 内存地址映射,选择 ROW COLUMN BANK;

Ordering : 选择默认 Normal。

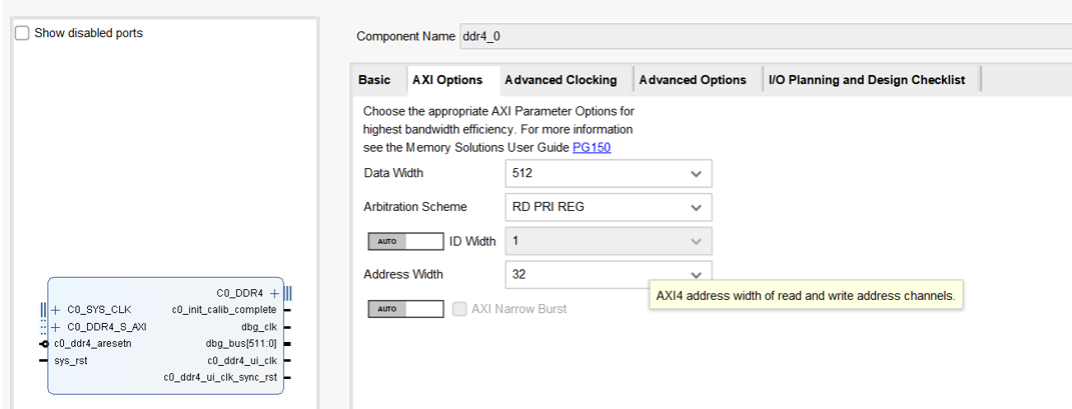

AXI Options – AXI 配置

Data Width : 在 AXI4 中数据的传输位宽,本工程设定为 512 bit;

Arbitration Scheme : 仲裁方案 选择默认,RD PRI REG;

ID Width 和 Address Width 系统自动生成。

Advanced Options – 高级选项

System Clock Option : 系统时钟选项,可以选则使用差分时钟和选用无缓冲区(单端);

Additional Clock Outputs : 附加时钟输出,本工程没有添加额外时钟,故不做选择。

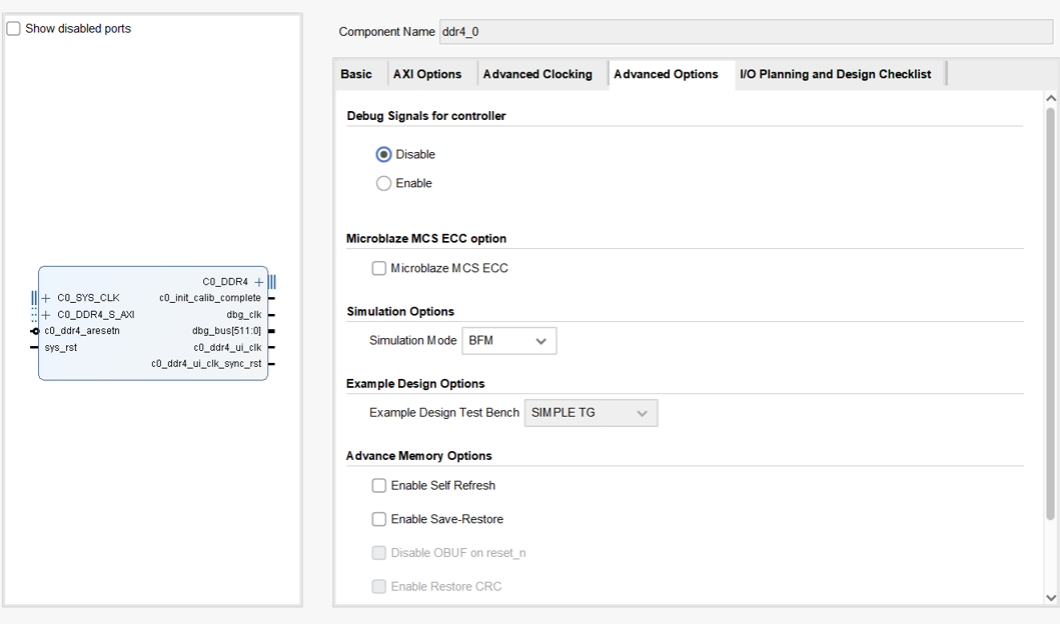

Advanced Options – 高级选项

此处为设置 Debug 模式的选项区;

debug signals for controller : 控制器调试信号,若希望添加调试信号则选 Enable,否则选 Disable。

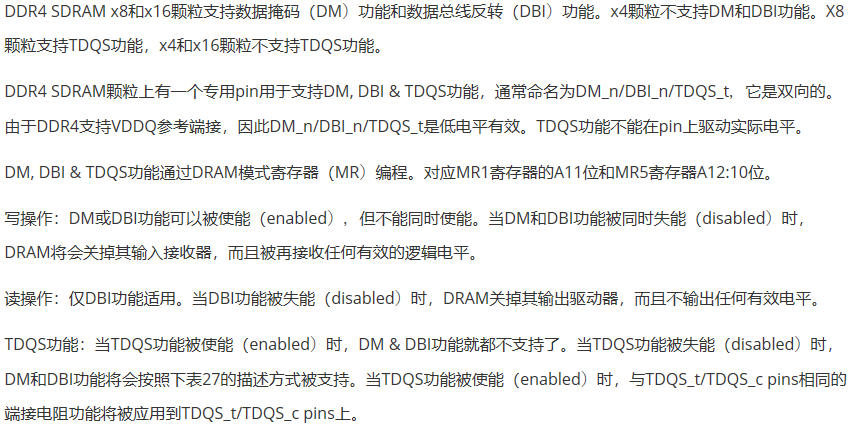

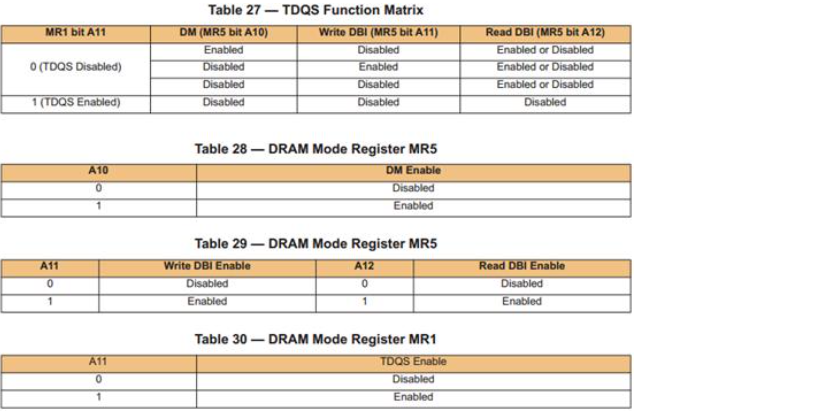

二、DDR4 SDRAM的DM/DBI/TDQS

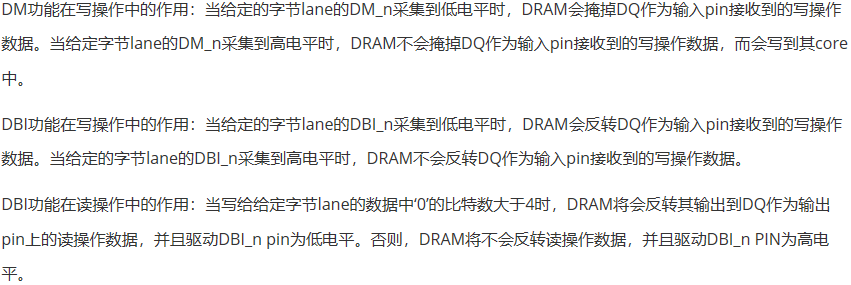

DM:Data Mask(数据掩码);

DBI:Data Bus Inversion(数据总线反转);

TDQS: 在 Datasheet中Pinout Description关于TDQS的描述可以看出,当 TDQS 启用时,TDQS是作为终端电阻吸收反射信号,提高信号完整性。

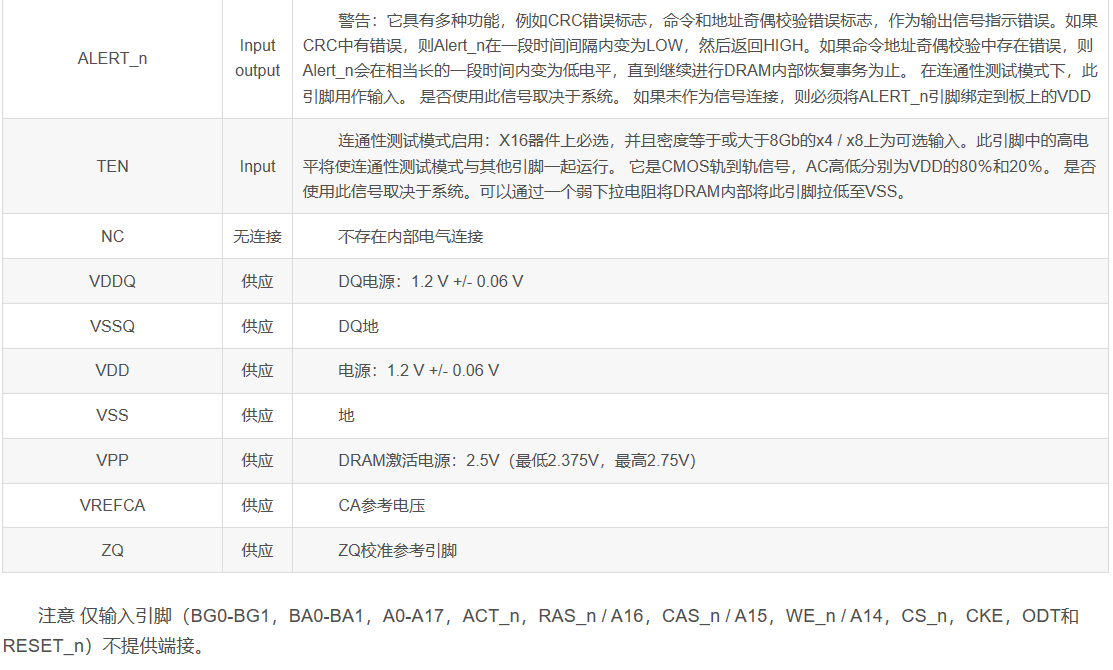

三、DDR4 SDRAM引脚说明

从功能上来讲,SDRAM总线由命令总线、地址总线和数据总线构成。其中,地址信息可以看做命令信息的一部分,

因此SDRAM的寻址需要和命令结合。在DDR4 SDRAM中,命令或者说寻址被分成了两部,激活命令(行寻址),读写命

令(列寻址)。在行列寻址过程中,也存在行列地址公用的情形,因此DDR4的操作变得比较复杂。

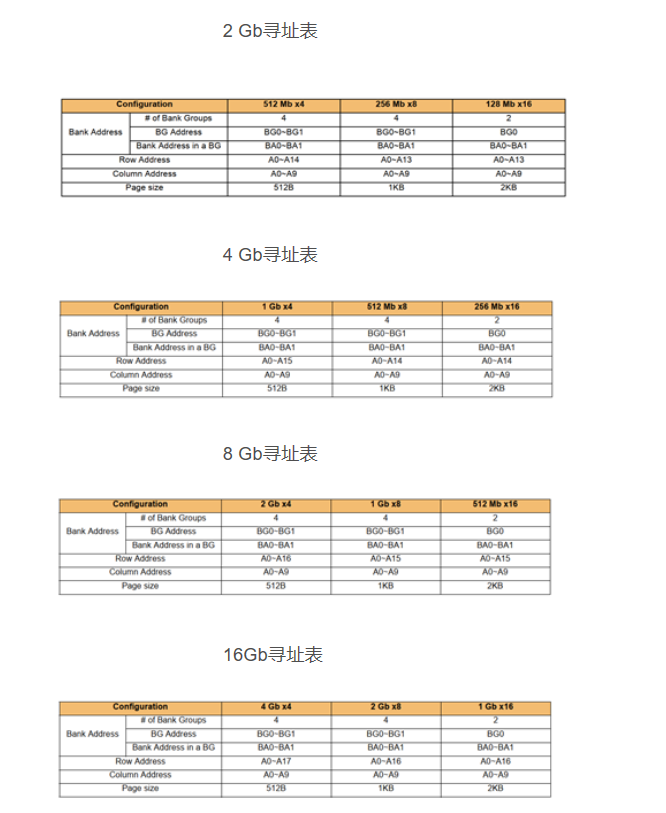

四、DDR4 SDRAM寻址

在DDR4中,新增了BANK GROUP的概念,一颗存储芯片中会有4个或者8个Bank Group,使用BG[1:0]或BG[2:0]进行寻址;

而每个BG组中有4个BANK存储体,使用BA[1:0]寻址;每个BANK中可以存在多个行,A0-A17用来寻址行,(只有16Gb容量DDR4存在A17),

行地址从A14到A17不等,由容量和位宽决定;在每一行中,又存在多个列,DDR4协议规定每行为1024列,即页大小为1024,使用A0-A9进行寻址。

浙公网安备 33010602011771号

浙公网安备 33010602011771号