Modelsim用法:使用modelsim直接导出数据 - 不依赖于testbench的更简便的方式

1. Motivation

对于一个复杂的设计,导出子模块的输出结果不是一件容易的事,通常我们采用以下的方式:

- 把子模块的输出接入到最外层的 testbench,并且加入数据导出的程序;

- 在子模块设计文件中加入数据导出的程序,但是这种写法是极其不规范的。

在单次仿真开始后,如果想要导出其他信号的数据,则需要重新编译,对于 Xilinx Vivado 来说这是一个极其耗时的过程,幸运的是,我们可以使用 Modelsim。

本文中提到的方法,可以借助 Modelsim 来导出整个设计中的任意信号,并且经过简单的 Perl 脚本处理后,可以直接提供给 VHDL 或者 MATLAB 进行调用分析。

Modelsim 的安装可以参考:https://www.cnblogs.com/devindd/articles/16837346.html

2. 使用Modelsim List

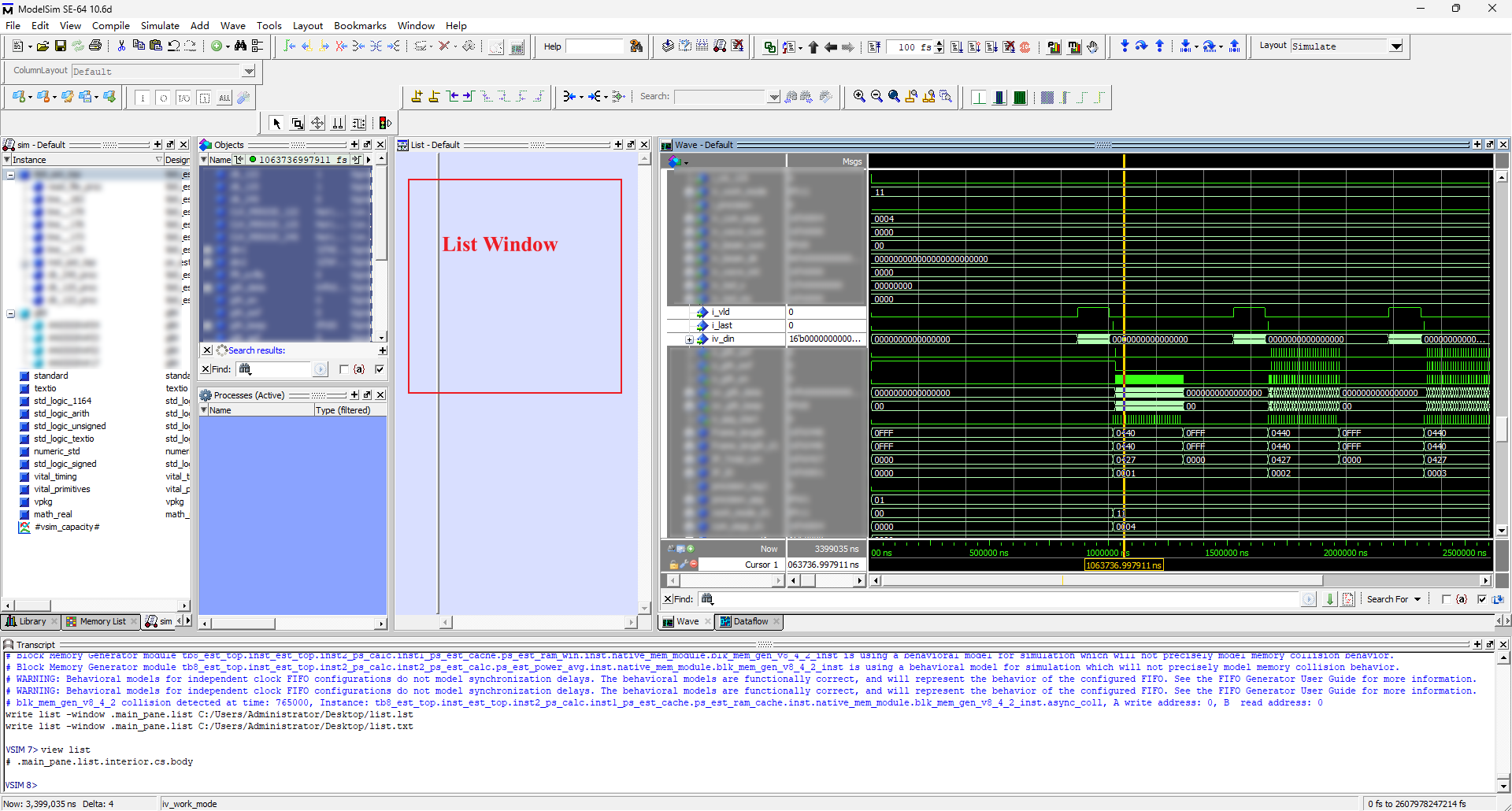

在Modelsin GUI窗口依次点击 View -> List,启用 List 窗口,默认与 Wave 窗口在同一个层级,可以随意拖动进行布局。

或者使用 Modelsim 内置的 Tcl 命令

view list

把需要导出数据的信号进行多选,然后拖动到 List Window 中,此时可以看到相关信号的值,以及对应时刻。

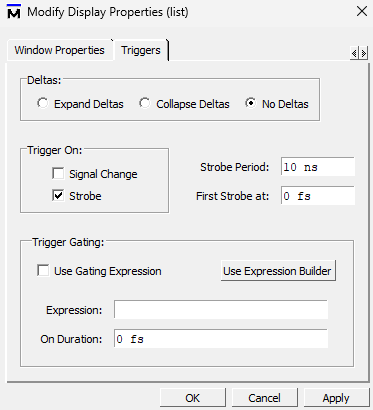

依次点击 List -> Edit Preferences 来修改触发类型。

在这里,我们选择将 Deltas 修改为 No Deltas,即触发到的数值不使用偏移的方式进行显示。

将 Trigger On 修改为 Strobe,而非 Signal Change,Strobe会周期性的 Examine 数据的值,而后者仅在信号的值发生改变时才导出到 List 中。

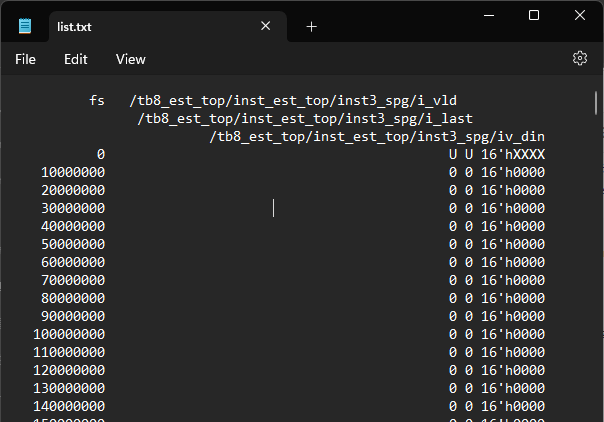

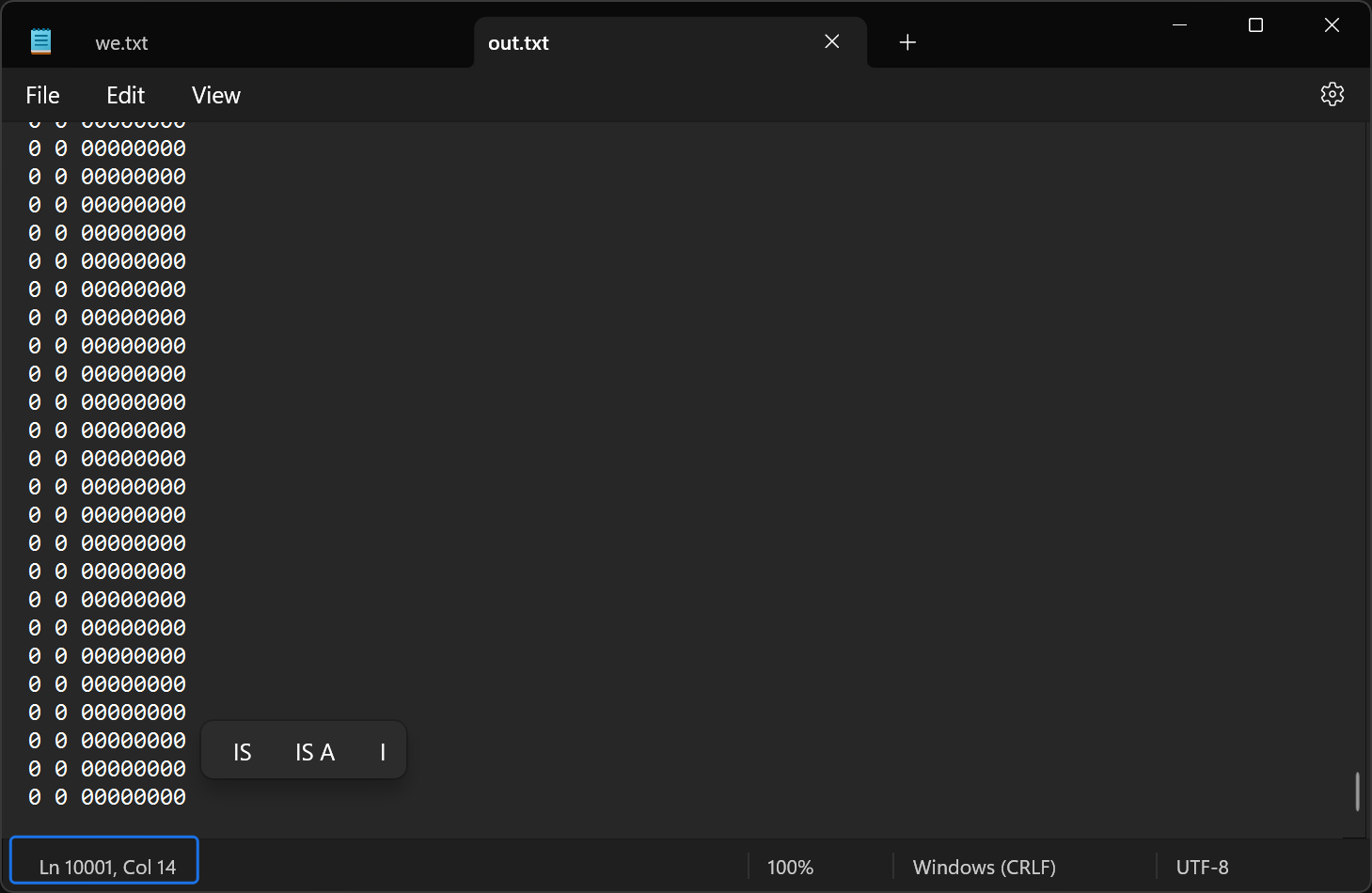

信号的值已经正确显示了,接下来使用 File -> Export -> Tabular List,把文件导出为 txt 格式。

3. Perl 处理

使用 Perl 处理的目的是把文件修改为可以被 VHDL 或者 MATLAB 后续调用的格式,你可以很方便的在 Modelsim 中修改数值的进制,并且在 List 中显示为你所需要的形式。

Perl 是实用性提取报表语言(Pratical Extraction Report Language),提取文字,处理报表是他的强项,是数字 IC 领域几乎必备的技能。

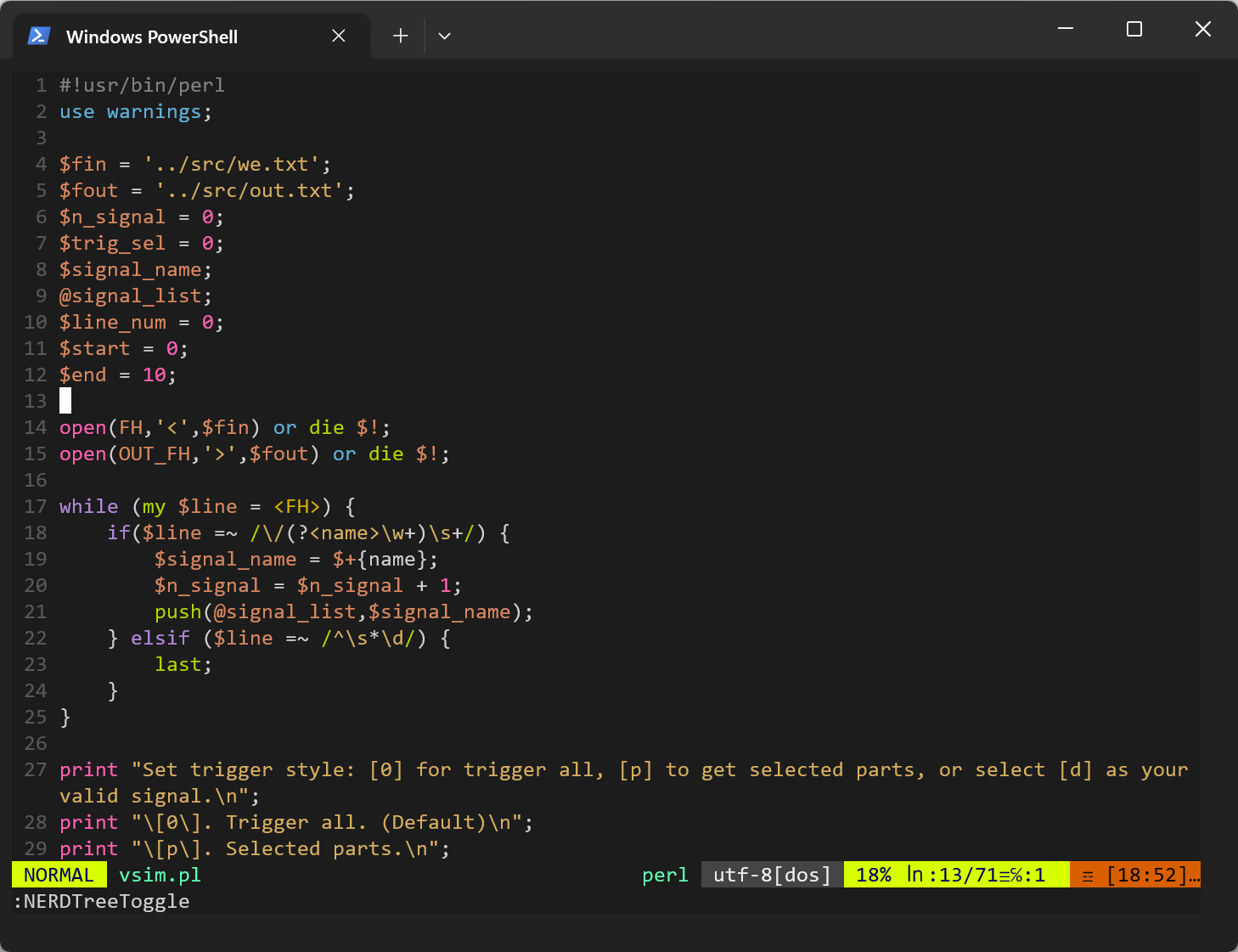

Perl 脚本由于太长我放到了github,地址如下:

https://github.com/devindang/openip-hdl/blob/main/perl_scripts/vsim.pl

TAB 显示比较奇怪是因为我用的 VIM,TAB SIZE 为 4,它貌似用的不是空格

Perl 脚本演示

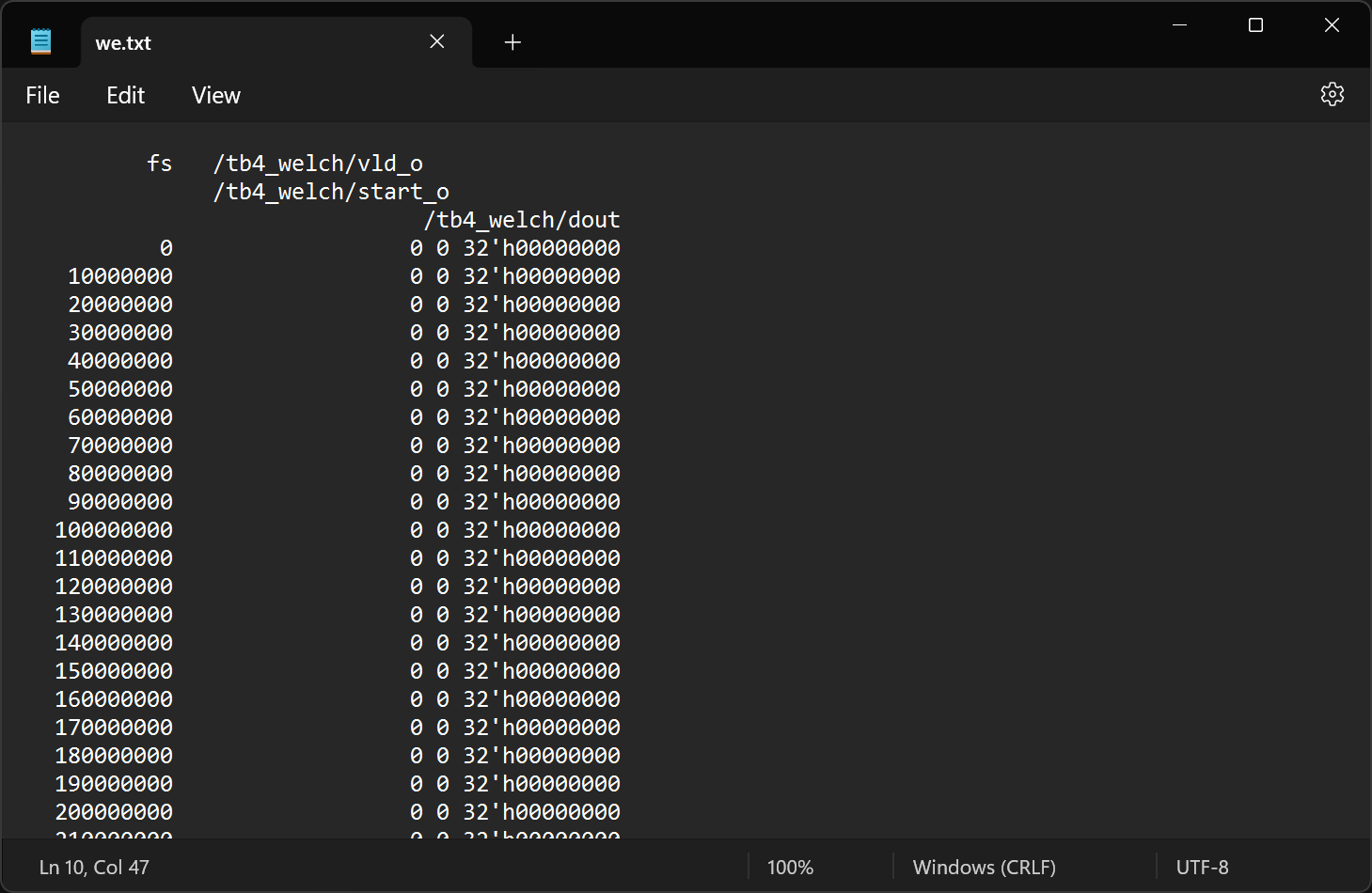

需要处理的数据如下:

修改 perl 脚本中的文件名,windows 的 perl 不支持使用 diamond 操作符把文件作为 perl 脚本的选项,因此只能使用这种方式。但是我没有删除脚本的 shebang line,你可以在你的 linux 系统中修改 shebang line 和源代码,使其支持文件名作为 option 的功能。

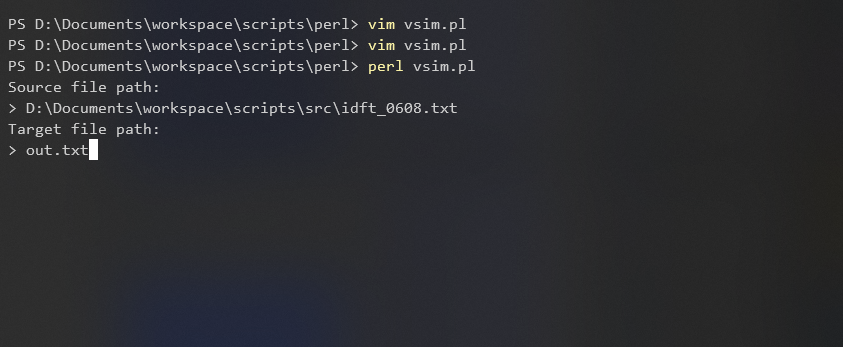

运行:

perl vsim.pl

输入源文件的文件名,你可以直接拖动你的文件到命令行中;

输入目的文件的文件名,你可以手动输入(默认创建在脚本执行位置),也可以使用 touch 创建的空文件并拖入

同时支持 .. 等索引,需要你的shell具有expand的功能。

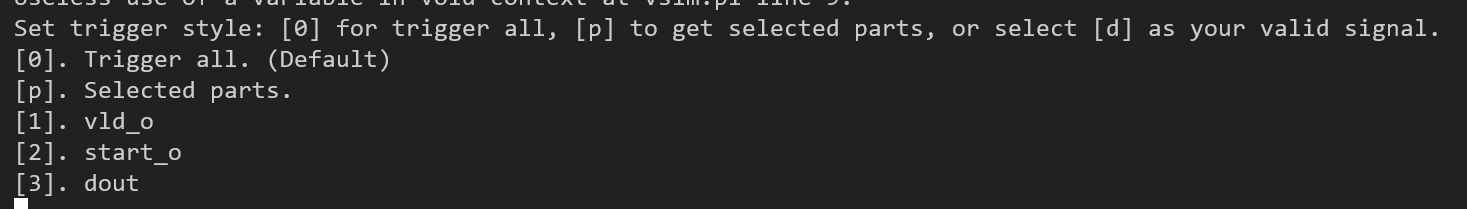

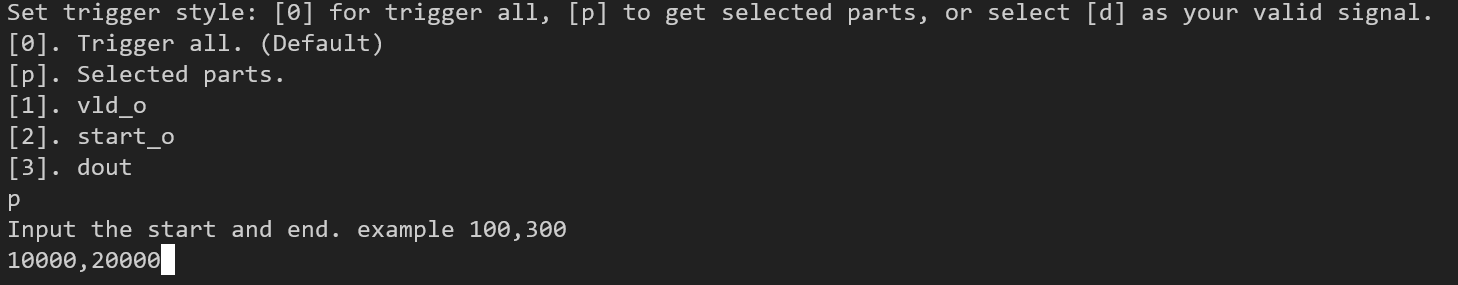

选择触发方式:

输入 0 ,则处理后输出所有文本内容;

输入 p ,后续可以指定输出的时间范围;

输入后续数字,则可以把对应的信号作为使能信号,输出使能信号为 1 时的内容。

例如使用 [1] vld_o 作为使能信号。

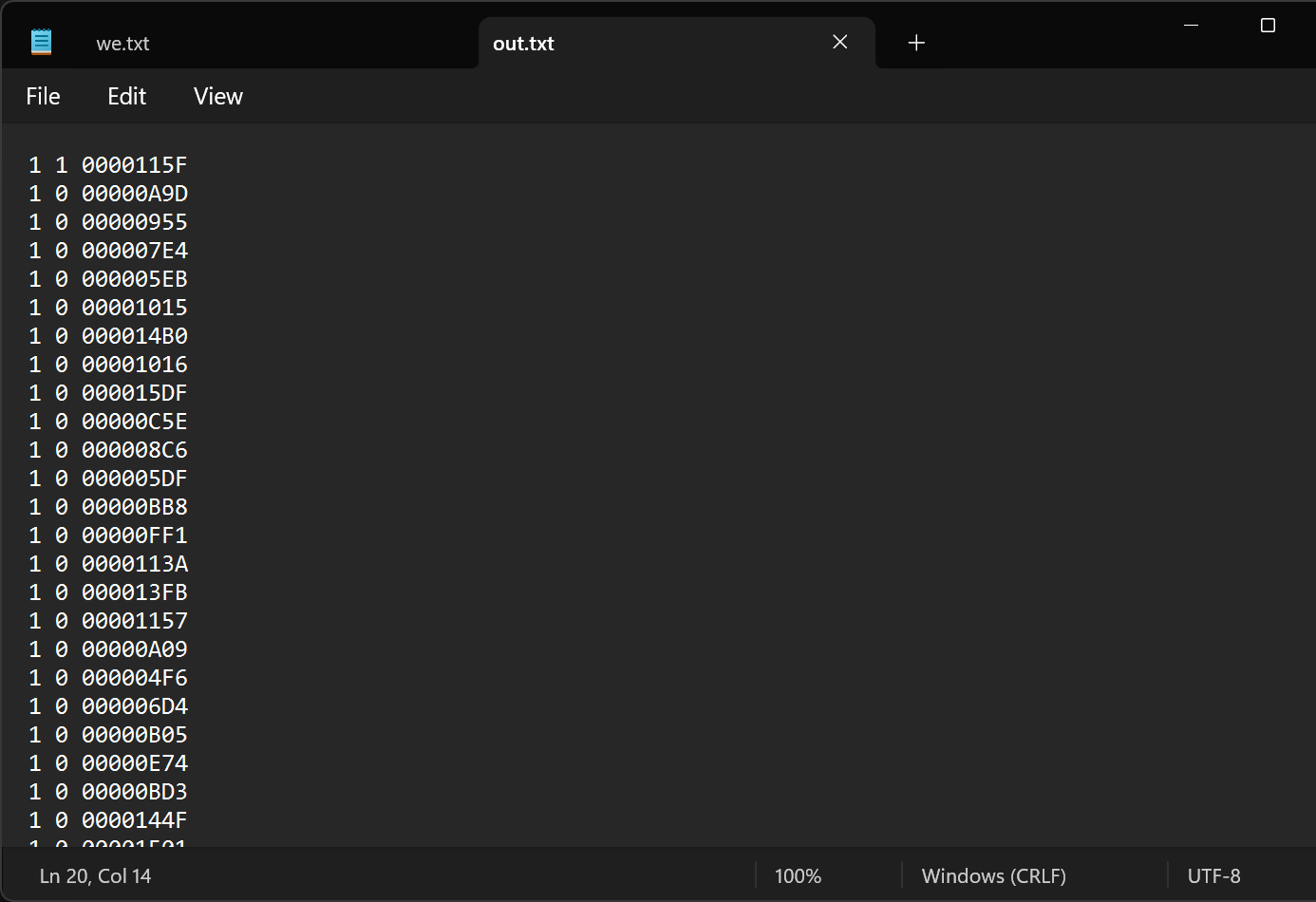

脚本会给出以下输出。

这里再演示一下使用 [p] 作为输入。

输出第 10000 到第 20000 个时钟的值,共 10001 个。

VHDL 中,对于十六进制数的读入,使用 textio 库的 hread 函数替代 read 函数。

如果需要其他格式,对应的修改 regex 内容即可。

4. Reference

https://www.thecodingforums.com/threads/exporting-data-in-modelsim.23392/

转载请注明出处,欢迎 PR 和评论,禁止商用。

浙公网安备 33010602011771号

浙公网安备 33010602011771号